Fターム[5J055AX06]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153) | スイッチの基本性能向上 (933) | 完全開放状態の確保 (142)

Fターム[5J055AX06]に分類される特許

1 - 20 / 142

半導体素子のゲート駆動方法

【課題】ターンオフスイッチング時に発生するノイズとスイッチング損失のトレードオフ特性を改善する。

【解決手段】半導体素子をターンオフさせるとき、半導体素子のコレクタ・エミッタ間電圧がコレクタ・エミッタ間に印加された直流電圧に達するまでは、前記コレクタ・エミッタ間電圧の変化率を大きくし、半導体素子のコレクタ・エミッタ間電圧が直流電圧に達した後は、前記コレクタ・エミッタ間電圧の変化率を小さくする。

(もっと読む)

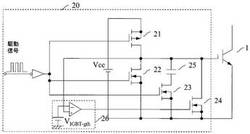

トランジスタ駆動回路

【課題】より簡単な構成で、出力トランジスタを確実にオフ状態に維持できるトランジスタ駆動回路を提供する。

【解決手段】NチャネルMOSFET5とコイル2との共通接続点;出力端子OUTとグランドとの間にフライホイールダイオード3を接続する。FET5のゲートには、NPNトランジスタ6及びPNPトランジスタ7のプッシュプル回路により制御信号を出力し、トランジスタ7のベースとグランドとの間にNPNトランジスタ11を接続し、トランジスタ11のベースとグランドとの間にNチャネルMOSFET14を接続して、FET14にPWM信号を入力する。ダイオード13は、FET14がオフ状態になるとトランジスタ11のベースにベース電流を供給し、ダイオード15をダイオード13のアノードとトランジスタ6及び7のベースとの間に接続する。NPNトランジスタ22をFET5のゲートと出力端子との間に接続し、トランジスタ22をPWM信号に応じてFET5がオフする際にオンさせる。

(もっと読む)

パワーMOSFETの駆動回路およびその素子値決定方法

【課題】パワーMOSFETを高速駆動する場合であっても、寄生インダクタンスに流れる電流の時間変化に応じて発生する電圧に起因したセルフターンオンの発生を防止できるようにしたパワーMOSFETの駆動回路、また、その素子値決定方法を提供する。

【解決手段】制御回路が、駆動回路によってスイッチを駆動制御することで、(2)区間においてスイッチS2HおよびS2Lをオンすると共にその他をオフとし、(3)区間においてスイッチS1LおよびS3Hをオンすると共にその他をオフとする。すると、(2)〜(3)区間にかけて、ハイサイド側のMOSFETのゲートソース間を所定のインピーダンスに切り替えることができ、リカバリー後半に至ったとしてもハイサイド側のMOSFETのゲートソース間電圧Vgs1を閾値電圧Vt未満に抑制できる。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

スイッチング回路装置及び制御回路

【課題】スイッチングトランジスタを適切にオフ動作する。

【解決手段】スイッチング回路装置は,高電位端子に接続されたドレインと低電位電源に接続されたソースとゲートとを有し,高電位端子と低電位電源との間に接続されたスイッチングトランジスタと,入力制御信号に応答して,スイッチングトランジスタのゲートにスイッチングトランジスタの閾値電圧より高い高電位と前記低電位電源の電位とを有する駆動パルスを出力する駆動回路とを有し,駆動回路は,スイッチングトランジスタのゲートとソースとの間に設けられた第1の駆動トランジスタを含む第1のインバータを有し,駆動パルスにより前記スイッチングトランジスタがオンからオフに変化するときに,第1の駆動トランジスタが導通してスイッチングトランジスタのゲートとソース間を短絡する。

(もっと読む)

電圧出力回路

【課題】プッシュ・プル接続された二つのスイッチ素子のON/OFFを切り換えること

によって生じる電力損失を抑制する。

【解決手段】プッシュ・プル接続された二つのスイッチ素子に対して並列に還流ダイオー

ドを設けておく。そして、何れのスイッチ素子もOFFの期間(デッドタイム期間)では

、ONにしようとする方のスイッチ素子に設けられた還流ダイオードに順方向電圧がかか

ったら、デッドタイム期間を終了して、一方のスイッチ素子をONにする。こうすれば、

二つのスイッチ素子の寄生容量での電荷の回生および充電が完了した後に、スイッチ素子

をONに切り換えることができるので、ONにしようするスイッチ素子の寄生容量に蓄え

られた電荷が、ONにしたスイッチ素子を流れて電力損失が発生することを回避すること

が可能となる。

(もっと読む)

アナログスイッチ回路

【課題】高位電源の電位より高い又は低位電源の電位より低い伝送信号を、MOSトランジスタを用いたアナログスイッチにより好適に阻止可能なアナログスイッチ回路を提供する。

【解決手段】第1のアナログスイッチ11と、第1のアナログスイッチ11の制御端子11cに至る制御信号経路21上に設けられた第2のアナログスイッチ12と、伝送信号の電位が所定の高電位レベルより高い場合又は伝送信号の電位が所定の低電位レベルより低い場合に第1のアナログスイッチ11の一方の入出力端子11aと制御端子11cとを短絡するよう構成された第3のアナログスイッチ13と、を備え、第2のアナログスイッチ12は、少なくとも第3のアナログスイッチ13が第1のアナログスイッチ11の一方の入出力端子11aと制御端子11cとを短絡する場合に、所定のレベルの電位が印加されてオフするようMOSトランジスタを用いて構成される。

(もっと読む)

高周波スイッチ

【課題】マルチモードシステムにおいてSOI基板上に形成された高周波スイッチの挿入損失特性を改善する。

【解決手段】少なくとも1つの第1ポート10および第2ポート20、共通ポート30、第1および第2シリーズスイッチ40,50を有する。第1ポート、第2ポートは、各々高周波信号を入力または出力する。共通ポートは、第1ポートまたは第2ポートを介して入出力される高周波信号を送信または受信する。第1シリーズスイッチは、少なくとも1つの第1のFETを備え、第1のFETのゲートに接続される第1ゲート抵抗への印加電圧に応じて第1ポートと共通ポートとの間を導通または遮断する。第2シリーズスイッチは、少なくとも1つの第2のFETを備え、第2のFETのゲートに接続され、第1ゲート抵抗よりも大きな抵抗値を有する第2ゲート抵抗への印加電圧に応じて第2ポートと共通ポートとの間を導通または遮断する。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

電子回路

【課題】 スイッチ回路におけるリーク電流を低減すること。

【解決手段】 本電子回路は、一端がそれぞれの入力端子AN1〜ANnに接続され、他端が共通の出力端子OUTに接続された複数のスイッチ回路SW1〜SWnであって、入力端子ANiと出力端子OUTとの間に直列に接続された第1スイッチSWia及び第2スイッチSWibを含む複数のスイッチ回路SW1〜SWnと、第1スイッチSWiaと第2スイッチSWibとの中間に位置する中間ノードMiに対し、出力端子OUTの電圧を供給する電圧供給回路20と、を備えることを特徴とする。

(もっと読む)

スイッチ回路

【課題】リーク電流がスイッチ回路に接続される回路に影響を与えることを抑制することが可能なスイッチ回路の提供。

【解決手段】第1の電位と第2の電位の間の接続状態をオンオフする第1のトランジスタと、該第1のトランジスタのドレインにソースが接続され、前記第1のトランジスタと略同一の特性を有する第2のトランジスタとを備え、前記第1のトランジスタをオフした時に、前記第1のトランジスタのゲート−ソース間電圧VGS1と、前記前記第2のトランジスタのゲート−ソース間電圧VGS2が略等しくなることを特徴とするスイッチ回路。

(もっと読む)

半導体スイッチ

【課題】端子切替時の挿入損失の増加を抑制した半導体スイッチを提供する。

【解決手段】実施形態によれば、電源回路部と制御回路部とスイッチ部とを備えた半導体スイッチが提供される。前記電源回路部は、内部電位生成回路と第1のトランジスタとを有する。前記内部電位生成回路部は、電源線に接続され、入力電位よりも高い第1の電位を生成する。前記第1のトランジスタは、前記内部電位生成回路の入力と出力との間に接続され、前記第1の電位が前記入力電位よりも低下したときオンして前記第1の電位を前記入力電位以上に保持するようにしきい値電圧が設定されたことを特徴とする。前記制御回路部は、前記第1の電位を供給され、ハイレベルまたはローレベルの制御信号を出力する。前記スイッチ部は、前記制御信号を入力して端子間の接続を切り替える。

(もっと読む)

半導体装置

【課題】小型化と高いアイソレーションを実現可能な半導体装置を提供する。

【解決手段】装置本体2は、半導体素子搭載部3と、第1の導電体4及び第2の導電体5を有する。第1の導電体4及び第2の導電体5は、半導体素子搭載部3の周囲に互いに近接して設けられている。半導体素子は、半導体素子搭載部に配設される。半導体素子は、第1のスルースイッチFET1と、第1のシャントスイッチFET1と、第2のスルースイッチFET2と、第2のシャントスイッチFET2と、を有する。第1のスルースイッチFET1は、共通端子ANTと第1の高周波端子RF1との間に接続される。第1のシャントスイッチFET1は、第1の高周波端子RF1に接続される。第2のスルースイッチFET2は、共通端子ANTと第2の高周波端子RF2との間に接続される。第2のシャントスイッチFET2は、一端が第2の高周波端子RF2に接続される。

(もっと読む)

CMOS回路及び半導体装置

【課題】しきい電圧VTが小さくてもリーク電流が小さく、また高速にかつ小さな電圧振幅で動作するCMOS回路さらには半導体装置を提供することである。

【解決手段】ゲートとソースを等しい電圧にしたときにドレインとソース間に実質的にサブスレショルド電流が流れるようなMOST(M)を含む出力段回路において、その非活性時には、前記MOST(M)のゲートとソース間を逆バイアスするように該MOST(M)のゲートに電圧を印加する。すなわち、MOST(M)がpチャンネル型の場合にはp型のソースに比べて高い電圧をゲートに印加し、また、MOST(M)がnチャンネル型の場合にはn型のソースに比べて低い電圧をゲートに印加する。活性時には、入力電圧に応じて該逆バイアス状態を保持するかあるいは順バイアス状態に制御する。

(もっと読む)

スイッチ回路

【課題】高周波信号が通る信号線と、オーディオ信号が通る複数の信号線が合流して使用される場合において、高周波信号およびオーディオ信号に発生する歪成分を抑制する。

【解決手段】高周波信号を伝送可能なケーブルの端子と、オーディオ信号を専用に伝送するケーブルの端子を共通に挿し込むことができる共通端子50からの信号線は二つに分岐して、高周波系スイッチ(USBスイッチ10)の一端と、第1階層のオーディオ系スイッチ(オーディオスイッチ20)の一端にそれぞれ接続される。高周波系スイッチの他端からの信号線は目的の回路に接続される。第1階層のオーディオ系スイッチの他端からの信号線は複数に分岐して、それぞれ第2階層のオーディオ系スイッチ(ヘッドホンスイッチ21、マイクスイッチ22)の一端に接続される。第2階層の複数のオーディオ系スイッチの他端からのそれぞれの信号線はそれぞれの目的の回路に接続される。

(もっと読む)

正負電圧論理出力回路及びこれを用いた高周波スイッチ回路

【課題】負電圧の変化に対して正常な論理回路動作を確保できる範囲である動作ウィンドウの幅の拡張を可能とする。

【解決手段】負電圧レベルシフト回路4aは、第3のレベルシフタ13aと、第4のレベルシフタ14aとを具備すると共に、レベルシフト基準電圧回路3からの切替信号に応じて第4のレベルシフタ14aを短絡、開放するレベルシフト切替スイッチ8aとを具備してなり、負電圧VSSの大きさに応じて、レベルシフト切替スイッチ8aのオン、オフを選択することで、負電圧VSSの変動に対して正常な回路動作を確保できる範囲である動作ウィンドの拡張が可能に構成されたものとなっている。

(もっと読む)

ドライブ信号生成回路、制御装置、スイッチング電源装置、および、制御方法

【課題】発振信号にノイズが発生してデッドタイムパルスが短くなる場合でも、ハイサイドドライブ信号およびローサイドドライブ信号を切り替えて出力することが可能なドライブ信号生成回路を提供する。

【解決手段】ドライブ信号生成回路1は、第1のパルス信号を出力するデッドタイムパルス生成回路1aと、第2のパルス信号Aを出力するデッドタイム調整回路1bと、第3のパルス信号Bを出力する補償パルス生成回路1cと、第2のパルス信号Aと第3のパルス信号Bとの論理和を演算し、この演算結果に応じた第4のパルス信号Zを出力するOR回路1dと、第4のパルス信号Zに応じて、ハイサイドドライブ信号SHおよびローサイドドライブ信号SLを出力する論理回路1eと、を備える。

(もっと読む)

半導体装置

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】直列に複数個接続されたそれぞれのMISFETQN1〜QN5のソース領域とドレイン領域の間に、ソース領域の電位を基準としてドレイン領域に正電圧を印加する場合と、ソース領域の電位を基準としてドレイン領域に負電圧を印加する場合のいずれの状態においても、ソース領域の電位とドレイン電極の電位が同電位の状態よりも容量が減少する電圧依存性を持つ歪補償用容量回路CAPC2が接続されている。

(もっと読む)

高周波スイッチ回路

【課題】通過損失が少なく出力特性が良いSOI基板上の高周波スイッチ回路を提供する。

【解決手段】本発明の実施形態の高周波スイッチ回路は、シリコン基板20上に形成された酸化膜21上に、第1の端子1と、入出力端子2と、第1の電極4bが前記第1の端子1に電気的に接続され、第2の電極4cが前記入出力端子2に接続されたFET4とを備える。第1の層間絶縁膜22が前記FETを周囲から離間分離し前記酸化膜21に達する溝に埋め込まれて配置され、前記酸化膜21と接続され、前記FET4を周囲から絶縁する。導電体層10が、前記溝内の前記第1の層間絶縁膜22上に形成され、接地端子GNDに接続される。第2の層間絶縁膜23が、前記導電体層10上及び前記FET4上に形成される。直流電圧を供給する配線層7が、前記溝内の第1の層間絶縁膜22上且つ前記導電体層10上に前記第2の層間絶縁膜23を介して形成されている。

(もっと読む)

高周波スイッチ回路およびその設計方法

【課題】コストの増大を抑え、ひずみ特性の良好な高周波スイッチ回路およびその設計方法を提供する。

【解決手段】共通端子と個別端子との間に高周波スイッチ部を備え、高周波スイッチ部は、スタック段数n段の直列スイッチ素子群と、スタック段数n+1段以上の直列スイッチ素子群で構成されている。スタック段数の異なる直列スイッチ素子群は、レイアウト面積と高調波特性に関連するコスト係数のトレードオフ関係を微調整し、最適なひずみ特性を実現しつつ、チップ面積の増加を抑制する。

(もっと読む)

1 - 20 / 142

[ Back to top ]