国際特許分類[H01L27/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733)

国際特許分類[H01L27/00]の下位に属する分類

1つの共通絶縁基板上に形成された薄膜または厚膜受動素子のみからなるもの (10)

整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321)

赤外線,可視光,短波長の電磁波または粒子線輻射に感応する半導体構成部品で,これらの輻射線エネルギーを電気的エネルギーに変換するかこれらの輻射線によって電気的エネルギーを制御するかのどちらかに特に適用されるもの (11,270)

少なくとも1つの電位障壁または表面障壁を有し,光放出に特に適用される半導体構成部品を含むもの (80)

異種材料の接合を有する熱電構成部品またはそれを有しない熱電構成部品を含むもの;熱磁気構成部品を含むもの

超電導を示す構成部品を含むもの (2)

圧電構成部品を含むもの;電歪構成部品を含むもの;磁歪構成部品を含むもの

電流磁気効果,例.ホール効果,を利用した構成部品を含むもの;同様な磁界効果を利用するもの (24)

整流,増幅,スイッチングをする固体構成部品で,電位障壁または表面障壁を有しないものを含む。

バルク負性抵抗効果構成部品を含むもの

能動部分として有機材料を用い,または能動部分として有機材料と他の材料との組み合わせを用いる構成部品を含むもの (2,779)

国際特許分類[H01L27/00]に分類される特許

1 - 10 / 247

半導体装置及びその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置および半導体装置の製造方法

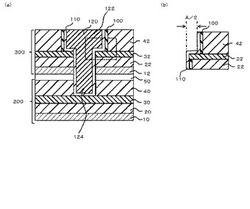

【課題】貫通電極が絶縁膜で被覆されていようがいまいが、貫通電極と配線の接触面積を確保すること。

【解決手段】本実施形態に係る半導体装置は、第1の半導体チップ200と、第1の半導体チップ200上に積層された第2の半導体チップ300と、第1の半導体チップ200と第2の半導体チップ300とを接続する貫通電極120と、を有している。貫通電極120は、第1の貫通電極部122と第2の貫通電極部124を有している。第1の貫通電極部122は、第2の半導体チップ300において、第2の絶縁膜42の上面から第2の配線32の上部まで設けられている。第2の貫通電極部124は、第1の貫通電極部122の下面と繋がっており、かつ第2の配線32と同一層から第2の半導体チップ300の第1の配線30上部まで設けられている。第1の貫通電極部122と第2の貫通電極部124の孔径は、平面視で、第1の貫通電極部122の孔径の方が大きい。

(もっと読む)

半導体装置、半導体装置の製造方法、および電子機器

【課題】アスペクト比の異なる複数の開口下部に接続される配線に対して最適な処理を施すことができるようにする。

【解決手段】半導体装置の製造方法において、第1の半導体基板と第2の半導体基板が接合された半導体基板の第1の開口の下部配線と、貫通接続孔と異なるアスペクト比の第2の開口の下部配線に対して、バリアメタル膜の成膜と、スパッタガスによる物理エッチングを同時に行うアンカー処理工程が含まれる。本技術は、例えば、固体撮像装置などの半導体装置に適用できる。

(もっと読む)

積層型半導体装置及びその製造方法

【課題】本発明は、接続電極のピッチを大きくせずにゲートの寄生容量を小さくすることができ、回路の高速化と層間接続の高密度化の両立が図れる積層型半導体装置及びその製造方法を提供することを目的とする。

【解決手段】第1のゲート60と、該第1のゲートよりも下層に形成された第1及び第2の不純物拡散領域31、33とを有する第1の半導体素子70と、

前記第1のゲートと対向して接合された第2のゲート65と、該第2のゲートよりも上層に形成された第3及び第4の不純物拡散領域36、38とを有する第2の半導体素子75と、を有することを特徴とする。

(もっと読む)

3DIC方法および装置

【解決手段】 切り分けられたダイまたはウェハのような素子を3次元的に集積する方法および切り分けられたダイまたはウェハのような素子が接続された集積構造。ダイまたはウェハの一方または両方は、その中に形成された半導体デバイスを有する。第1コンタクト構造を有する第1素子は、第2コンタクト構造を有する第2素子に接着される。第1、第2コンタクト構造は、接着の際に露出されることが可能で、また接着の結果、電気的に接続される。接着後にビアがエッチングされるとともに埋め込まれて電気的配線を露出および形成して第1、第2コンタクト構造を接続するとともに、この電気的配線への表面からの電気的なアクセスが可能になる。または、第1、第2コンタクト構造は接着の際に露出されず、接着後にビアがエッチングおよび埋め込みされて第1、第2コンタクト構造が電気的に接続されるとともに接続された第1、第2コンタクト構造への電気的なアクセスが得られる。 (もっと読む)

三次元集積回路を作製する方法

【課題】集積回路を作製する新規なタイプの方法を提供する。

【解決手段】少なくとも第3の層がその間に配置された、少なくとも半導体の第1および第2の層を備える基板を作製するステップと、少なくとも第1のMOSデバイスを作製するステップであって、その活性領域が半導体の第1の層の少なくとも一部に形成される、ステップと、少なくとも第2のMOSデバイスを作製するステップであって、その活性領域が半導体の第2の層の少なくとも一部に形成され、第2のMOSデバイスの活性領域が第2のMOSデバイスのゲートと第1のMOSデバイスの活性領域との間に配置される、ステップとを少なくとも含む、集積電子回路を作製する方法。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体チップを積層して半導体装置を製造する際に、当該半導体チップの回路の不良電子素子を救済し、半導体装置の歩留まりを向上させる。

【解決手段】ウェハ10を厚み方向に貫通する一対の貫通電極50〜52を形成し、デバイス層11に一対の貫通電極50〜52を短絡する共有配線24、26、28を形成し、デバイス層11の表面11aにおいて異なる場所につながる一対のフロントバンプ20〜22を形成する。一対の貫通電極50〜52に対して異なる極性で電圧を印加し、一対の貫通電極50〜52のうちの一の貫通電極50〜52上にバックバンプ80〜82を形成する。ウェハ10を積層し、一のウェハ10上のバックバンプ80〜82と、他のデバイス層11上のフロントバンプ20〜22とを接続する。

(もっと読む)

固体撮像素子および電子情報機器

【課題】多層化した複数層の受光部により複数の色信号を、1画素部で一括して同時に検出した1画素部毎の各層の信号電荷から得ると共に、静止画および動画のいずれであっても鮮明なフルカラー撮像を実現する。

【解決手段】半導体層または半導体基板に交互に一方向に隣接配置されたP型注入領域4およびN型注入領域5であって、被写体からの画像光を光電変換する複数層の光電変換部(3層のP型注入領域およびN型注入領域)が、光電変換部とはバンドギャップの異なる透明層(SiO2膜)をその各間に介在して積層され、一方向に直交する他方向にそれぞれ配置された3層のP型注入領域4およびN型注入領域5と、P型注入領域4およびN型注入領域5上に設けられた一方向の複数の電荷転送駆動用の透明電極6〜11と、複数の電荷転送駆動用の透明電極6〜11上に設けられ、入射光を透過または遮光制御する入射光透過/遮光制御手段とを有している。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

集積電力段

【課題】集積電力段において、入力電圧を集積電力段の一側面(例えば上面)で受け取り、出力電圧を集積電力段の反対側面(例えば底面)から出力する。

【解決手段】集積電力段は負荷段の上に位置する共通ダイを備え、共通ダイはドライバ段102及び電力スイッチ104を備える。電力スイッチは制御トランジスタ110及び同期トランジスタ112を含む。制御トランジスタのドレインD1が共通ダイの入力電圧を共通ダイの一側面(例えば上面)で受ける。制御トランジスタのソースS1が同期トランジスタのドレインD2に結合され、前記共通ダイの出力電圧を共通ダイの反対側面(例えば底面)で出力する。電力段の下にインターポーザ106を含めることができる。インターポーザは共通ダイの反対側面で共通ダイの出力電圧に結合される出力インダクタ118及び必要に応じ出力キャパシタ120を含む。

(もっと読む)

1 - 10 / 247

[ Back to top ]