Fターム[2G132AL06]の内容

Fターム[2G132AL06]の下位に属するFターム

品種、試験項目で試験プログラムを変更 (30)

Fターム[2G132AL06]に分類される特許

1 - 20 / 100

インターフェースボード

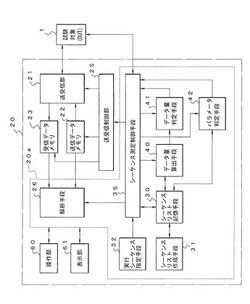

移動体通信装置試験システムおよび試験方法

【課題】試験対象に対してシーケンス測定を実行する際に、取得データ量の面で、誤った測定の無駄な測定をしないで済むようにする。

【解決手段】シーケンス測定制御手段35が実行指定された測定シーケンスにしたがう制御を開始する前に、実行指定された測定シーケンスで送受信部21が解析対象として取得する予定のデータ量の合計値を算出するデータ量算出手段40と、算出したデータ量の合計値が受信データメモリ23の所定容量に応じて予め設定した許容値を超えるか否かを判定するデータ量判定手段41とを備え、シーケンス測定制御手段35は、データ量判定手段41により算出したデータ量の合計値が許容値を超えると判定されたとき、その判定結果を表示部61に表示して、ユーザーに通知する。

(もっと読む)

半導体集積回路及び半導体集積回路の検査方法

【課題】ジッタ耐性検査における検査コストの低減を図りつつ、入力される主信号の特性劣化を抑制できる半導体集積回路を提供する。

【解決手段】半導体集積回路101は、主信号にジッタ信号が付加されてなる検査信号を生成する機能を有し、ジッタ信号の基となる信号を生成するジッタ信号生成部50と、電源線Vccと接地線GNDとの間に介在し、電源線Vccからの電力供給を受けて外部からの主信号を増幅して出力するバッファ回路10と、電源線Vccとバッファ回路10との間およびバッファ回路10と接地線GNDとの間に介在し電源線Vccからバッファ回路10への供給電力をジッタ信号の基となる信号の大きさに基づいて変化させることにより主信号にジッタ信号を付加するジッタ信号付加部30とを備える。

(もっと読む)

試験情報表示装置、方法、プログラム、および該ソフトウェアを格納したコンピュータ可読媒体

【課題】STILで記述された電子回路素子用試験プログラムから所望の試験情報を取得し、その取得した情報をユーザが見やすい形式で表示する装置を提供する。

【解決手段】STILで記述された電子回路素子用試験プログラムから所定の試験情報を取得し、その取得した情報を表示する試験情報表示装置(1000)は、前記試験プログラムを参照するプログラム参照手段(10)と、前記所定の試験情報に関連したコマンドを基に、前記参照した試験プログラムから該試験情報を含むデータブロックを取得するデータブロック取得手段(20)と、前記取得したデータブロックから前記所定の試験情報を取得する試験情報取得手段(20)と、前記取得した試験情報を配列する試験情報配列手段(40)と、前記配列された試験情報を表示する試験情報表示手段(50)と、を備える。

(もっと読む)

検査装置

【課題】クロック信号発生手段の不具合の有無を一目で認識することができる検査装置を提供する。

【解決手段】検査基板400のFPGA92は、入力されたクロック信号の周波数、周期、Duty比の各期待値、実施回数をレジスタ部923へ記憶する(S14)。FPGA92は、入力されたクロック信号CLK1,CLK2の周波数、周期、Duty比を算出する(S32)。FPGA92は、算出したクロック信号CLK1,CLK2の周波数、周期、Duty比のそれぞれがレジスタ部923のクロック信号CLK1,CLK2の周波数、周期、Duty比の各期待値を満たすか否か判定して(S33)、判定結果をレジスタ部923の所定の領域へ記憶する(S34)。FPGA92は、満たさなければ(S35:No)、表示部93のLEDを赤色発光させ(S36)、満たせば(S35:Yes)、LEDを青色発光させる(S38)。

(もっと読む)

半導体試験システム及び半導体装置の試験方法

【課題】試験ボード側からの更新要求に応じて簡単に試験プログラムを更新することができる半導体試験システムを提供する。

【解決手段】本発明の一形態に係る半導体試験システム1は、試験対象の半導体装置4が搭載される試験ボード2と、試験ボード2に半導体装置4の試験信号を出力する半導体試験装置3と、を備える半導体試験システムである。試験ボード2は、搭載される半導体装置4に応じて、半導体装置4に対応する試験プログラムを半導体試験装置3に要求し、要求した試験プログラムを半導体試験装置3に読み出し指令させるインターフェース回路5を有する。

(もっと読む)

ウェハテスト装置、ウェハテスト方法およびプログラム

【課題】ウェハテストのテスト時間を増加させることなく、検出された不良セルがいずれの不良パターンで不良となったのかを検知できるようにすること。

【解決手段】ウェハテスト装置は、第1および第2のテストプログラムを保持する記憶部と、第1のテストプログラムを用いてロット内の複数のウェハのうちの一部のウェハに対するテストを行なうとともに、第2のテストプログラムを用いてロット内の複数のウェハのうちの残部のウェハに対するテストを行なう演算部とを備え、第1のテストプログラムは、ウェハに対して複数の動作テストを実行し、各動作テストが終了するごとにウェハに含まれる不良メモリセルの累積情報を装置の外部に出力し、第2のテストプログラムは、ウェハに対して複数の動作テストを実行し、すべて動作テストが終了した後にウェハに含まれる不良メモリセルの累積情報を装置の外部に出力する。

(もっと読む)

半導体試験装置におけるドライバ波形生成回路

【課題】 小変更で、様々なドライバ波形生成仕様に適応可能な、半導体試験装置におけるドライバ波形生成回路を提供する。

【解決手段】 並列処理プロセッサ16は、波形生成プログラムメモリ15に予めプログラムされた内容に従い、選択されるオンザフライ入力データポート11をアクセスして複数のテストデータを取り込み、続いて選択されるマルチポートレシスタ群13及びマルチポートメモリ群14に記憶された各設定データに基づき、ドライブデータ生成に必要なテストレートの数だけ並列に演算処理を行い、結果生成される複数のドライブデータを、続いて選択される複数のオンザフライ出力データポート12をアクセスして同時に出力する。

(もっと読む)

平面回路基板の電気検査装置及び電気検査方法

【課題】平面回路基板の種類によらず同一装置により検査を行うこと。

【解決手段】電気検査装置2は、平面回路基板1に対向可能に配置され、所定の規則により一様に配列された多数のプローブピン3と、多数のプローブピン3を支持すると共に、多数のプローブピン3を平面回路基板1に対して移動させるためのピンボード4と、各プローブピン3に接続され、各プローブピン3からの信号に基づき平面回路基板1の電気的特性を計測するための計測部12等と、各プローブピン3を、計測部12等に対して選択的に接続するための接続切替部15と、電源部13と、通信部14と、制御部11とを備える。平面回路基板1上に形成されたプローブピン3と接触可能な検査点37A〜37Hの配置は、多数のプローブピン3の配列に整合するように予め配置される。

(もっと読む)

半導体試験装置

【課題】格別の操作を要することなく最適な電圧供給を行い、無駄な電力消費や負荷の削減を行うことを目的とする。

【解決手段】本発明の半導体試験装置は、DUT2の試験を行う出力制御ユニット5を備える半導体試験装置1であって、試験を行うためのテストプログラムに設定された設定電圧の情報に基づいて動作を行う複数のドライバ32と、設定電圧の情報を取得して、取得した情報に基づいてドライバ32に設定される設定電圧の電圧をドライバ32に供給する供給電圧を変更可能な1または複数の可変電源33と、を備えている。これにより、DUT2が無駄な電力を消費することなく、負荷が与えられなくなる。且つ、テストプログラムの設定電圧の情報を利用しているため、電源制御の操作を要することなく、最適な電圧を供給することができる。

(もっと読む)

システムインパッケージおよびソケット

【課題】サイズやコストを増大させることなく、テスト容易なシステムインパッケージを実現するとともに、そのシステムインパッケージをテストボードとして活用する。

【解決手段】テスト容易化回路内装SIP1cは、少なくともその1つに集積回路チップが搭載された複数のコア基板を、絶縁樹脂層を介して貼り合わせて構成するとともに、コア基板に形成された配線層を、スルーホールを介して接続して構成される。そのコア基板の1つであるテスト容易化回路内装基板10cには、テスト対象の集積回路であるDUT121を装着するソケット122が搭載されており、また、そのソケット122内に設けられたポゴピン1220には、インピーダンス整合用のチップ抵抗1224、インダクタ1225などの受動素子が設けられている。

(もっと読む)

波形発生装置および半導体試験装置

【課題】複数のタイミングエッジ発生回路を制御して所望の波形を出力するときに、出力波形のパターンを自由に変更可能にすることを目的とする。

【解決手段】波形を発生させる波形発生ユニット2を備える波形発生装置であって、エッジを変化させるタイミングを規定したタイミングデータTDに基づいてタイミングエッジTEを発生させる複数のタイミングエッジ発生回路14と、タイミングエッジ発生回路14のうち駆動するタイミングエッジ発生回路14を特定する真理値テーブルTTを書き換え可能に記憶するテーブル記憶部22と、真理値テーブルTTに基づいて、発生させる波形に応じたタイミングエッジ発生回路14を駆動する駆動制御部23と、真理値テーブルTTに基づいて、駆動するタイミングエッジ発生回路14にタイミングデータTDを入力させる複数のタイミングデータ出力部12と、を備えている。

(もっと読む)

試験装置および接続装置

【課題】付加回路を用いて既存の試験装置を低コストで高速および高機能化する。

【解決手段】被試験デバイスの種類に応じたソケットボードに接続されて、被試験デバイスを試験する試験装置であって、被試験デバイスを試験する試験モジュールを内部に有するテストヘッドと、テストヘッド内の試験モジュールにケーブルを介して接続されると共に、ソケットボードに接続される機能ボードと、機能ボードに搭載され、試験モジュールおよび被試験デバイスに接続される付加回路と、を備える試験装置を提供する。

(もっと読む)

コンタクトピンリングの構築方法とコンタクトピンリング

【課題】 汎用性に富むコンタクトピンリングの構築方法と、それに用いるコンタクトピンリングを提供することを課題とする。

【解決手段】 枠体と、前記枠体によって形成されるリング状の収容部と、前記収容部に着脱自在に取り付け可能な1又は複数のピンブロックと、前記ピンブロックに保持される1又は複数のコンタクトピンとを有するコンタクトピンリングを用い、前記収容部に取り付ける前記ピンブロックの数、その取付位置、又は種類を選択することにより、コンタクトピンリングに保持されるコンタクトピンの数又は配置を前記ピンブロック単位で設定してコンタクトピンリングを構築するコンタクトピンリングの構築方法、及びそれに用いるコンタクトピンリングを提供することによって解決する。

(もっと読む)

プローブカードの搬送機構、プローブカードの搬送方法及びプローブ装置

【課題】プローブカードが大型化しても機械的強度を十分に確保することができると共にプローブカードの交換作業を円滑に行うことができるプローブカードの搬送機構を提供する。

【解決手段】本発明のプローブカードの搬送機構は、プローブカードを搬送する第1のカード搬送機構11と、第1のカード搬送機構11とインサートリング54との間でプローブカード56を搬送する第2のカード搬送機構12と、を備え、第1のカード搬送機構11は、ヘッド旋回駆動機構57側に設けられ且つ第2のカード搬送機構12との間でプローブカード56の受け渡しを行う進退動可能なカード保持具13を有し、第2のカード搬送機構12は、第1のカード搬送機構11とインサートリング54の間でプローブカード56を搬送する載置台52と、載置台52の周囲に互いに所定間隔を空けて昇降可能に設けられ第1、第2、第3昇降機構16A、16B、16Cと、を有する。

(もっと読む)

被測定デバイス搭載ボード、及びデバイスインタフェース部

【課題】複数種類のパフォーマンスボードと接続できる接続ユニットを提供する。

【解決手段】ICソケットが載置されたパフォーマンスボードと、ICソケットに保持される電子デバイスを試験する試験装置とを電気的に接続する接続ユニットであって、パフォーマンスボードと対向して設けられる保持基板と、保持基板上における位置が変更可能に保持基板上に設けられ、パフォーマンスボードが備えるパフォーマンスボード側コネクタと接続されるべき接続ユニット側コネクタとを備えることを特徴とする接続ユニットを提供する。

(もっと読む)

ユニバーサルチャネルインタフェース試験回路及びシステム

【課題】電子回路等の被試験装置に試験信号を印加して被試験装置を監視することにより、被試験装置の1つ又は複数の電気特性を試験する試験回路及びシステムを提供する。

【解決手段】試験回路は、単一の自動試験システム内の複数のユニバーサルインタフェースチャネル回路210を用いて、電子回路又は装置を試験を行う。単一のデータ収集回路120を、1つ又は複数のユニバーサルインタフェースチャネル回路210に結合する。各ユニバーサルインタフェースチャネル回路210は、様々な試験信号のうちの1つをDUTに供給することを、データ収集回路120から個別に命令する。

(もっと読む)

試験装置、試験方法およびプログラム

【課題】複数の試験モジュールを制御する。

【解決手段】被試験デバイスを試験する試験モジュール部と、試験モジュール部を制御する制御パケットを生成する試験制御部と、試験制御部から制御パケットを受けて試験モジュール部に送信する接続部とを備え、試験モジュール部は、第1のパケット構造の制御パケットに応じて動作する第1試験モジュールと、第1のパケット構造の制御パケットに拡張領域が追加された第2のパケット構造の制御パケットに応じて動作する第2試験モジュールとを有する試験装置を提供する。

(もっと読む)

半導体装置テスト接続体

【課題】テスト用のパッドを共用可能とする半導体装置テスト接続体を提供する。

【解決手段】半導体ウェーハ5と、半導体ウェーハ5に形成され、ダイシングライン13により個片化される予定の複数の半導体チップ11と、半導体ウェーハ5に形成され、半導体チップ11を特定する識別符号の少なくとも一部を付与するシフトレジスタ(33、34)と、半導体チップ11から離間し、半導体ウェーハ5の周辺に設けられ、外部から電気的な接続が可能なテスト用パッド18が複数配設されたパッド部17と、ダイシングライン13にあり、一端が識別符号に基づいて選択された半導体チップ11に接続され、他端がパッド部17の側に引き出されたテスト用のバス配線15と、バス配線15の他端とパッド部17との間にあり、バス配線15を決められたテスト用パッド18に接続する接続線部19とを備える。

(もっと読む)

半導体試験装置、および半導体装置の試験方法

【課題】試験対象の半導体装置のデバイスピンの配置、数、およびサイズならびにPKGサイズなどの規格に変更があっても対応可能な半導体試験装置を提供する。

【解決手段】試験対象の半導体装置が搭載される、複数のテストピンを含むテストボードと、複数のテストピンと複数のデバイスピンとの導通を試験するテスト部と、複数のテストピンのうち、デバイスピンと導通するテストピンを特定し、デバイスピンの座標を参照してデバイスピンに接続するテストピンを割り当てる制御部とを有する。

(もっと読む)

1 - 20 / 100

[ Back to top ]