Fターム[4K029DC39]の内容

Fターム[4K029DC39]の下位に属するFターム

永久磁石によるもの (199)

電磁石によるもの (30)

磁石の形状、構造 (79)

磁石の配置 (175)

ターゲット、磁石の相対運動 (334)

Fターム[4K029DC39]に分類される特許

41 - 60 / 1,642

導電性膜及びその製造方法並びに導電性膜形成用銀合金スパッタリングターゲット及びその製造方法

【課題】 低抵抗かつ高反射率の特性と共に表面粗さが小さく、高い耐硫化性及び耐塩化性を兼ね備えた導電性膜およびその製造方法を提供すること。

【解決手段】 導電性膜が、InおよびSnのうち1種または2種を合計で:0.1〜1.5原子%、Sb:0.1〜1.5原子%を含有し、さらにGa,Mgの内の1種または2種を合計で0.5〜3原子%を含有し、残部がAgおよび不可避不純物からなる成分組成を有した銀合金で構成されている。この導電性膜は、表面に有機EL素子の透明導電膜が積層され、さらにその上に有機EL層を含む電界発光層が積層される有機EL素子用の反射電極膜として好適である。

(もっと読む)

導電体膜およびその製造方法

【課題】低抵抗であると共に耐塩化性及び耐熱性に優れた導電体膜およびその製造方法を提供すること。

【解決手段】導電体膜3が、Mgを、0.5〜2質量%含有し、さらにEuを、0.05〜1質量%含有し、残部がAgおよび不可避不純物からなる成分組成の銀合金で構成されている。この導電体膜3の製造方法は、Mgを、0.5〜2質量%含有し、さらにEuを、0.05〜1質量%含有し、残部がAgおよび不可避不純物からなる成分組成の銀合金で構成されているスパッタリングターゲットを用いてスパッタにより成膜する。

(もっと読む)

薄層を堆積させる方法、およびこのように得られた製品

【課題】良好な薄膜処理方法およびその製品の提供。

【解決手段】本発明の主題の一つは、基材の第1の側上に堆積された少なくとも1層の薄い連続的な膜の処理のための方法であって、薄膜を連続に保ちながら、そしてこの薄膜を溶融するステップ無しで該薄膜の結晶化度を高めるように、この少なくとも1つの薄膜が少なくとも300℃に昇温され、該第1の側とは反対側上の温度が150℃以下ように保ちたれることを特徴とする、方法。

発明の別の主題は、この方法によって得ることができる材料である。

(もっと読む)

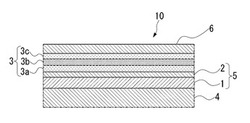

透明導電性積層体およびその製造方法

【課題】異なる組成のスパッタリングターゲットを使用して、インラインで積層し、短時間の加熱処理で結晶性を有することができ、低抵抗の透明導電膜を有した透明導電性積層体及びその製造方法を提供する。

【解決手段】透明導電膜はIn、Sn、Oを主成分とし、Snの含有量が1重量%以上4重量%以下であるインジウム・スズ複合酸化物からなる第一透明導電膜3aと、同じくIn、Sn、Oを主成分とし、Snの含有量が4重量%超え、10重量%以下であるインジウム・スズ複合酸化物からなる第二透明導電膜3bで形成され、前記第一及び第二透明導電膜の膜厚がそれぞれ10nm以上30nm以下であり、両者の透明導電膜の合計厚みが20nm以上40nm以下であり、真空中で加熱温度が120℃以上200℃以下であり、加熱時間が1分以上、30分以下の条件で加熱処理することで前記第一及び第二透明導電膜のいずれも結晶化することを特徴とする。

(もっと読む)

スパッタクリーニング方法

【課題】真空成膜装置に発生するパーティクルをスパッタリングすることなく、低減するスパッタクリーニング方を提供する。

【解決手段】成膜チャンバ101を形成する真空容器と、前記真空容器の内部を真空排気する排気機構102と、前記真空容器の内部に成膜材料ターゲットを取り付けたカソードと、前記真空容器にプロセスガス103を導入するプロセスガス導入機構と、前記真空容器にクリーニングガス104を導入するクリーニングガス導入機構と、前記真空容器の内部に基板を搬送する基板搬送機構110を備え、前記カソードの成膜材料ターゲットを放電でスパッタし、前記基板の成膜面側にスパッタ成膜を行うスパッタ成膜装置において、クリーニング基板111を基板搬送機構により真空容器の内部に搬入し、前記クリーニング基板の捕捉面の逆側に磁石を配置し、前記磁石の磁力により前記真空容器内の異物をクリーニング基板の捕捉面に付着させる。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】バリア層(バリアメタル)13を覆うようにライナー層14が形成されている。ライナー層14は、Ni(ニッケル)から構成される。ライナー層14は、このライナー層14の内側に形成されるCu(銅)からなる導電体15に対する濡れ性を高め、かつ、溝部12の内側の平滑性を高める。

(もっと読む)

透明薄膜積層体の製造装置及びその製造方法

【課題】透明樹脂基材に吸着しているガスの放出を抑え、ロール巻取りの際の巻きシワを抑制することができる透明薄膜積層体の製造装置及び製造方法を提供する。

【解決手段】基材巻出し室1の基材ロール2より透明樹脂基材3を巻出し、搬送ロール4を通過後、スパッタ室5のアノードドラム6を通過させる。その際にカソード7a、7b、7cとの間に電力を印加しスパッタリングで透明導電性膜の成膜を行ない、搬送ロール4を通してフィルム巻き取り室8で再びロール9に巻き上げることにより、長尺、具体的には数100m以上、場合により数1000mの透明薄膜積層体を連続的に製造する。基材ロール2に巻かれている透明樹脂基材3は、基材巻出し室1の調温装置1aによって温度0℃に冷却する。また、搬送ロール4a、4b、4c、4dとアノードドラム6及びスパッタ室5内雰囲気の温度を、調温装置12により、透明樹脂基材3と同じ0℃に冷却する。

(もっと読む)

酸化物焼結体および酸化物透明導電膜

【課題】150℃以下の低い基板温度の成膜によっても、比抵抗が5×10-3Ω・cm以下、可視波長(400nm〜800nm)において98%以上の高い透過率を有する結晶性の透明導電膜を提供する。

【解決手段】Sn/Inが0.019〜0.102であり、かつ、In/(In+Sn+Co)が0.771〜0.967、Sn/(In+Sn+Co)が0.016〜0.091、Co/(In+Sn+Co)が0.015〜0.15であり、相対密度が98%以上、比抵抗が5×10-3Ω・cm以下である酸化物焼結体をスパッタリングターゲットとして成膜して透明導電膜を得る。

(もっと読む)

スパッタリングターゲット

【課題】高密度かつ低抵抗のスパッタリングターゲット、電界効果移動度の高い薄膜トランジスタを提供する。

【解決手段】Gaをドープした酸化インジウム、又はAlをドープした酸化インジウムを含み、正4価の原子価を示す金属を、Gaとインジウムの合計又はAlとインジウムの合計に対して100原子ppm超1100原子ppm以下含み、結晶構造が、実質的に酸化インジウムのビックスバイト構造からなる焼結体を含むスパッタリングターゲット。

(もっと読む)

Zn−Si−O系酸化物焼結体とその製造方法および透明導電膜

【課題】スパッタリングターゲットに利用された場合には異常放電等が抑制され、蒸着用タブレットに利用された場合にはスプラッシュ現象が抑制されるZn-Si-O系酸化物焼結体とその製法等を提供する。

【解決手段】酸化亜鉛を主成分とし、Siを含有するZn-Si-O系酸化物焼結体であって、Siの含有量が、Si/(Zn + Si)原子数比で0.1〜10原子%であり、Si元素がウルツ鉱型酸化亜鉛相に固溶していると共に、SiO2相および珪酸亜鉛(Zn2SiO4)であるスピネル型複合酸化物相を含有していないことを特徴とする。上記焼結体の製法は、原料粉末であるZnO粉末とSiO2粉末から得られた造粒粉を成形し、その成形体を焼成して上記焼結体を製造する際、700〜900℃の温度域を昇温速度5℃/分以上の速さで昇温させる工程と、成形体を焼成炉内において900℃〜1400℃で焼成する工程を有することを特徴とする。

(もっと読む)

純すずターゲット材料がマグネトロンスパッタ法を利用したフッ素ドープ酸化すず薄膜の製造方法

【課題】純すずターゲット材料がマグネトロンスパッタ法を利用したフッ素ドープ酸化すず薄膜の製造方法を提供する。

【解決手段】高純度すずをマグネトロンスパッタリングのターゲット材料として、マグネトロンスパッタの生産プロセスにおいて、反応ガス四フッ化炭素(CF4)と酸素(O2)を導入する。四フッ化炭素(CF4)は、作業ガスによって励起されるプラズマがフッ化物(F)イオンとフッ化物(F)励起状態原子を分離し、すずターゲット材料と合わせて、基板上にフッ素ドープ酸化すず薄膜を形成することにより、生産コストを軽減でき、フッ素ドープ酸化すず薄膜の品質を向上できる。

(もっと読む)

マグネトロンスパッタカソード

【課題】ターゲットに局所的な侵食が発生することが抑制できてターゲットの利用効率を高めることができるマグネトロンスパッタカソードを提供する。

【解決手段】マグネトロンスパッタカソードは、立体形状の輪郭を有するターゲット1aと、トンネル状の磁場を形成する磁石ユニット2aとを備える。このターゲットの表面の一部をスパッタリングにより侵食されるスパッタ面12a、12cとし、前記磁場の垂直成分がゼロとなる位置を通る線が、スパッタ面を跨いでターゲットの周囲を周回するように磁石ユニットが構成される。

(もっと読む)

相変化メモリの形成方法、及び相変化メモリの形成装置

【課題】金属カルコゲナイド膜の積層体を有する相変化メモリにおいて、読み書き動作の速度を高めることのできる相変化メモリの形成装置、及び相変化メモリの形成方法を提供する。

【解決手段】GeTe膜とSbTe膜とを基板上にて交互に積層することによって相変化メモリを形成する際に、処理基板Sの温度を250℃以上350℃以下の所定温度に維持する。加えて、互いに異なる組成を有する二つのターゲットであるGeTeターゲット22aとSb2Te3ターゲット22bの各々を互いに異なるタイミングでアルゴンガスによりスパッタする。このとき、互いに異なる組成を有した二つ以上の金属カルコゲナイド膜であるGeTe膜とSb2Te3膜とを毎秒3nm以上10nm以下の速度で前記基板上に積層する。

(もっと読む)

スパッタリングターゲット及びそれを用いた磁気メモリの製造方法

【課題】磁気トンネル接合素子のMR比を向上させることが可能なスパッタリングターゲット、及びそれを用いた磁気メモリの製造方法を提供する。

【解決手段】MgOを主成分とし、厚さが3mm以下であるターゲット本体10を備えることを特徴とするスパッタリングターゲット、及びそれを用いた、MR比を向上させることができる磁気メモリの製造方法である。

(もっと読む)

真空コーティング装置およびナノ・コンポジット被膜を堆積する方法

【解決課題】 真空コーティング装置およびナノ・コンポジット被膜を堆積する方法を提供すること。

【解決手段】 真空チャンバ(31)と、少なくとも1対の対向カソード(1および4)と、この対向カソードにAC電圧を供給してこれをデュアル・マグネトロン・スパッタリング・モードで動作させる電源(8)とを備え、PVDコーティングのための少なくとも1のさらなるカソードが真空チャンバ内に提供された真空コーティング装置および方法は、少なくとも1のさらなるカソード(6および/または7)がマグネトロン・カソードとされ、マグネトロン・カソードまたはアーク・カソードに接続可能なパルス化電源またはDC電源の形態としてさらなる電源(42,44)が提供されている。

(もっと読む)

炭素薄膜成膜方法

【課題】水素フリーで緻密で硬質なダイヤモンドライクカーボン膜を容易に形成することができる炭素薄膜成膜法を提供する。

【解決手段】この炭素被膜成膜方法は、マグネトロンスパッタ法により試料基板電極上に配置された試料基板表面に炭素被膜を堆積させる炭素被膜成膜装置を用い、炭素ターゲット基板電極と試料電極に対し、下記1〜4の条件でそれぞれ電圧を印加させることを特徴とする。

1.ターゲット基板電極に印加する電圧が負のパルス電圧であって、かつ、そのパルス電圧時間比が40%以下であること。

2.ターゲット基板電極に印加するパルス電圧のパルス時間が20μs〜200μsであること。

3.試料基板電極に印加する電圧が負のパルス電圧であって、かつ、そのパルス電圧時間比が50%以下であること。

4.試料基板電極に印加する負パルス電圧の大きさが−20V〜−200Vであること。

(もっと読む)

長尺ガラスフィルムの処理方法および処理装置

【課題】 樹脂フィルムに比べて伸び難く且つ割れやすい長尺ガラスフィルムに対して熱負荷の掛かる表面処理を連続的に施す方法を提供する。

【解決手段】 巻出ロール210から連続的に引き出された長尺ガラスフィルムGを搬送経路に沿って搬送しながら順に加熱処理、表面処理および冷却処理を施す長尺ガラスフィルムGの処理方法であって、前記表面処理では長尺ガラスフィルムGの一方の面を熱媒で加熱されたキャンロール233の外周面上に接触させながら他方の面にスパッタリング等の熱負荷の掛かる処理を施し、前記搬送経路における前記表面処理と前記加熱処理との間および/または前記冷却処理の後において例えばアキュムレータロールを用いて長尺ガラスフィルムGの伸縮を調整する。

(もっと読む)

両面真空成膜方法、及び該方法によって得られる積層体

【課題】単純な装置構成を用いて適宜に加熱処理等を施すことにより、両面に真空成膜が施された積層体を効率的に製造できる成膜方法を提供すること等。

【解決手段】ロール状に巻かれた長尺の基体を第1の面を被成膜面として第1ロール室から第2ロール室へ向う方向に第1ロール室から繰り出し、繰り出された基体を脱ガスし、脱ガスされた基体の第1の面に第1成膜室において第1の膜材料を成膜し、第1の膜材料の上に第2成膜室において第2の膜材料を成膜し、膜材料が積層された基体を第2ロール室でロール状に巻取り、巻き取った基体を第1の面とは反対側の第2の面を被成膜面として方向に第1ロール室から繰り出し、上記全ての処理を繰り返す。

(もっと読む)

スパッタリング装置

【課題】複数のターゲット表面上の反応ガスの分圧を互いに等しくし、各ターゲットを互いに同じ速度でスパッタできるスパッタリング装置を提供する。

【解決手段】

互いに離間して一列に並んで配置された複数のターゲット211〜214と、隣り合う二個のターゲット211〜214を一組として、一組のターゲット211〜214間に電圧が印加されるターゲット装置2012、2034とを有し、各ターゲット装置2012、2034は、一組のターゲット211〜214の側面と対向して配置された隔壁231〜234と、隔壁231〜234とターゲット211〜214との間に設けられたガス導入口281〜284と、真空槽11の底面に設けられた主排気口2512、2534とをそれぞれ有し、ガス導入口281〜284から導入された反応ガスは、一組のターゲット211〜214間を通って主排気口2512、2534から真空排気される。

(もっと読む)

両面真空成膜方法、及び該方法によって得られる積層体

【課題】単純な装置構成を用いて適宜に加熱処理等を施すことにより、両面に真空成膜が施された積層体を効率的に製造できる成膜方法を提供する。

【解決手段】ロール状に巻かれた長尺の基体を第1ロール室W1から第2ロール室W2へ向う第1の方向に第1ロール室から繰り出し、繰り出された基体10を脱ガスし、第1の面に第1成膜室41において第1の膜材料を成膜し、第1の膜材料が成膜された基体を、第2ロール室から第1ロール室へ向う第2の方向で第2成膜室42へ案内し、第2の方向に案内中の基体の第1の面とは反対側の第2の面に第2成膜室において第2の膜材料を成膜し、第1の面に第1の膜材料が成膜され且つ第2の面に第2の膜材料が成膜された基体を第1ロール室と第2ロール室の間に設けた第3ロール室W3でロール状に巻取り、第3ロール室で巻き取った基体を第1の方向に第1ロール室から繰り出し、上記全ての処理を繰り返す。

(もっと読む)

41 - 60 / 1,642

[ Back to top ]