Fターム[5C058BB12]の内容

電気信号の光信号への変換 (29,260) | 信号処理、回路 (3,942) | メモリを使用するもの (1,362) | ラインメモリ (55)

Fターム[5C058BB12]に分類される特許

1 - 20 / 55

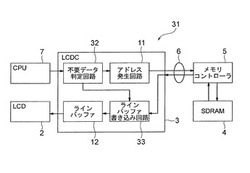

画像表示駆動装置及び画像表示システム

【課題】画像データの読み出しを高速化し、表示エリアの移動をきめ細かに行なう。

【解決手段】不要データ判定回路32がデータ転送要求にかかる表示エリアの画像データの先頭のアドレスが内部バス6のバス幅の先頭のアドレスと合致するか否かを判定し、合致しないと判定したときは、アドレス発生回路11には先頭アドレスを0と出力する。このときSDRAM4からから読み出された内部バス6のバス幅の転送データには、無効データを含むことになる。この場合には、不要データ判定回路32が無効データを含んでいるのは無効データの位置データをラインバッファ書き込み回路33に出力する。ラインバッファ書き込み回路33は、このデータに基づいて、読み出した1つのバス幅分のデータのうちの無効データをラインバッファ12に書き込まないようにする。

(もっと読む)

プロジェクタ、及び画像処理装置

【課題】低製造コストかつコンパクトな装置で、光学系で生じる種々の歪みを補正することができる、プロジェクタ、及び画像処理装置を提供する。

【解決手段】1ライン分の入力画像信号を保持する入力ラインメモリ4aと、入力ラインメモリ4aから転送された入力画像信号を用いて投影レンズ7の歪みに対応する補正を施した中間画像信号を生成する画像処理部5と、1ライン分の中間画像信号を保持する出力ラインメモリ4bと、中間画像信号に従って光源からの光を投影レンズ7に導くLCOS6とを備えており、画像処理部5は、複数ラインの入力画像信号を格納する入力補充バッファ51と、1ライン分の中間画像信号の生成に必要な入力画像信号を格納する入力データバッファ52と、入力補充バッファ51から入力データバッファ52への補充ライン数を計算する補充ライン数計算部531とを備えていることを特徴とする。

(もっと読む)

画像処理装置、画像処理方法、画像処理プログラム

【課題】フレームデータ内から特定の種別の画素データを抽出する際に、精度良く画素データを取得すること

【解決手段】システム制御部110は、フレームデータをラスタースキャン形式で供給する。システム制御部110は、フレームデータ内の各画素データの有効/無効を示すデータイネーブル信号を同時に供給する。ラインバッファ120は、フレームデータに含まれる画素データを逐次保持する。有効データ検出部130は、データイネーブル信号に基づいて、フレームデータの有効データ区間を検出する。比較部140は、有効データ検出部130が検出した有効データ区間と、予め指定された表示サイズと、を比較する。画素データ取得部150は、比較部140による比較結果に基づき、ラインバッファ120から画素データを取得する。

(もっと読む)

画像処理装置

【課題】 ラインバッファ方式の画像処理装置においてフルカラーかつ高解像度の画像表示を実現する。

【解決手段】 コントローラ103は、各垂直走査期間において、各表示対象の画像データのLCD202での表示に先行して、各表示対象の画像データの生成を画像データ生成部105に順次指令し、画像データ生成部105は、指令された表示対象の画像データを生成し、仮想メモリとしてのワークメモリ108にMMU107を介して格納する。ラインバッファ描画部112は、このワークメモリ108内の画像データに基づいて、各水平走査期間において表示する1ライン分の画像データを生成する。また、MMU107は、ワークメモリ108において画像データを記憶しているページのうちLCD202での表示に使用された画像データを記憶するページを新たな画像データの記憶に備えて解放する。

(もっと読む)

画像表示装置

【課題】入力ビデオ信号の映像を、その映像におけるノイズまたは歪みが発生し易い周縁が映り込まない様に表示パネルに表示する画像表示装置を提供する。

【解決手段】この画像表示装置は、表示パネル5と、入力ビデオ信号S1の映像における各々一定の垂直方向幅の上下の周縁が前記表示パネルの映像表示領域の外にはみ出す様に、前記映像の垂直方向サイズを前記映像表示領域の垂直方向サイズよりも前記周縁に対応する分大きくなる様に変更して前記入力ビデオ信号を前記表示パネルに出力する表示信号処理部4と、表示信号処理部4を制御する制御部3とを備える。

(もっと読む)

プロジェクター

【課題】プロジェクターのリソースの小型化を図る。

【解決手段】フレーム映像記憶部に記憶されたフレーム映像の入力映像データにおけるライン方向およびピクセル方向にそれぞれM×N(M,N≧2)個の画素から成るブロック映像データ毎に記憶するブロック映像記憶部と、被投写面上に投写される映像の歪みを補正する補正処理行う補正処理部であって、ライン方向およびピクセル方向にK×L(2≦K≦M,2≦L≦N)個の画素から成る補間ブロック映像データに基づいて、補正後の映像データである補正後映像データを生成する補正処理部と、補正処理に用いられる補間ブロック映像データの少なくとも一部を含むブロック映像データがブロック映像記憶部に記憶されているか否かを、補間ブロック映像データの隅部のうち、少なくとも補正処理の処理方向の下流に位置する2隅の画素を用いて判定する判定部とを備えるプロジェクター。

(もっと読む)

複数の表示パネルの駆動および同期化

画像表示装置およびプログラム並びに画像表示制御方法

【課題】画像の表示をより適切に行なう。

【解決手段】VRAMからの1画素分のデータの読み出しタイミングがVRAMへの1画素分のデータの書き込みタイミングよりも速いLCDコントローラーにおいて、通常時は読み出しタイミング(クロック信号DCLK)にデフォルト値Ddefを設定し(S320)、書き込み用のアドレスカウンターAc1と読み込み用のアドレスカウンターAc2との差分(Ac1−Ac2)が所定値Aref以下となったときに読み出しタイミングを書き込みタイミングと同一の設定値Dlowに設定する(S330)。これにより、データの読み出しが書き込みを追い越す追い越し現象が生じるのを回避でき、液晶ディスプレイへの画像の表示をより適切に行なうことができる。

(もっと読む)

画像信号処理装置と画像信号処理方法および画像表示装置

【課題】拡大表示で広い階調表現を可能とする。

【解決手段】画像拡大処理部21は、画素の繰り返しを行い拡大された画像の画像信号を生成する。多階調化処理部22のパターンデータ出力部は、画素を繰り返した繰り返し領域毎に、拡大された画像の画像信号から上位側の所定ビット数を除いた信号に基づく階調を繰り返し領域の画素で再現するためのパターンデータを出力する。多階調化処理部22の加算部は、繰り返し領域毎に、拡大された画像の画像信号における上位側の所定ビット数の信号に対してパターンデータを加算して出力する。

(もっと読む)

位相同期された共振走査型ディスプレイの投影

走査プロジェクタ(100)は、二次元で走査するミラー(142)を含む。この走査ミラーは、高速走査軸上において共振周波数で振動し、低速走査軸上で、入力されるフレームレートに位相同期される。補間手段(104)は、ピクセルクロックが到達するとき、ミラーの位置に基づいて隣接する画素から画素密度のデータを補間する。入力される映像データは、バッファに保存される。完全なフレーム分よりも小さい映像データを、バッファ内に保存することができる。 (もっと読む)

画像処理装置および画像処理方法

【課題】コンピュータなどのデバイスの画面の変化を効率よく検出する。

【解決手段】

ディスプレイタイミング設定部16は画像をラスタースキャンにより描画するためのタイミングを決定する。ピクセル読出部10はディスプレイタイミング設定部が出力するタイミングに応じてピクセルを読み出す。関心領域情報入力部20は画像中に任意の関心領域を特定するための情報を入力する。関心領域特定部26はディスプレイタイミング設定部16が出力するタイミングに基づいて、前記ピクセルが関心領域に含まれるか否かを特定する。有限ビット生成部30は前記ピクセルが関心領域に含まれる場合には、前記ピクセルの情報を写像変換することにより有限ビット列を生成する。

(もっと読む)

ピクセルデータを垂直にスケーリングするための方法および装置

【課題】ピクセルデータの垂直なスケーリングに関連して、ラインストアメモリ内に格納する必要のあるピクセルデータの量を減らす。

【解決手段】イメージ処理装置112は、ピクセルのラインを、RGB色空間から、YCbCr色空間に変換するための、RGB色空間からYCbCr色空間へのコンバータモジュール144と、コンバータモジュールに結合された、クロミナンスデシメータモジュール145と、中間表現を格納するように構成された、クロミナンスデシメータモジュール145に結合されたラインストアメモリ170と、中間表現のスケーリング済みバージョンを生成するように構成された、ラインストアメモリ170に結合された垂直スケーラモジュール146とを備える。

(もっと読む)

画面表示制御装置

【課題】簡単で安価な構成で、入力画像データを構成する画素データの並べ替えを行うことで、当該入力画像データを構成する画素データの並び順と走査方向が異なる表示部に当該入力画像データに基づく画像を表示することのできる技術を提供する。

【解決手段】1フレームが240ラインのラインデータにより構成される入力画像データの4ライン分のラインデータが第1バッファまたは第2バッファに保持されている。そして、データ置換制御手段により、VRAMからの320ラインのラインデータにより構成された1フレームの画像データの圧縮データの読み出し時に、伸長部により復元された画像データのうち、第1バッファまたは第2バッファに保持された4ライン分が入力画像データに置換されて圧縮部に出力される置換処理が行われ、この置換処理が60回繰り返されることにより、VRAMの圧縮データのすべてが入力画像データに置換される。

(もっと読む)

画面表示制御装置

【課題】同じラインの圧縮データの画像メモリへの書込みと読出しとが確実に同時に行われないような技術を提供する。

【解決手段】同じラインの圧縮データのVRAM766への書込みと読出しとが競合するときに、書込むべき当該ラインの圧縮データをバッファ領域766aに保持させる制御が書込/読出制御手段763により実行されるので、同じラインの圧縮データのVRAM766への書込みと読出しとが同時に行われることを確実に防止できる。また、書込/読出制御手段763により、当該ラインの圧縮データを読出すときに、バッファ領域766aに保持されている当該ラインの圧縮データを読出す制御が実行されるため、バッファ領域766aに保持された当該ラインについての新しい圧縮データを確実に読出すことができる。

(もっと読む)

プラズマディスプレイ装置及びプラズマディスプレイパネルの駆動方法

【課題】解像度の低下を抑えつつ輝度を向上させるプラズマデシィスプレイ装置及びプラズマディスプレイパネルの駆動方法を提供することを目的とする。

【解決手段】インターレース信号を表示するプラズマディスプレイ装置であって、

前記入力信号の垂直同期信号周波数に基づいて、1フィールド内で発光可能な最大サステインパルス数を算出する最大サステインパルス数算出手段61と、

前記入力信号の前記1フィールドの表示負荷率を算出する表示負荷率算出手段50と、

該表示負荷率算出手段により算出された前記表示負荷率に基づいて、前記1フィールドの目標サステインパルス数を決定する目標サステインパルス数決定手段62と、

該目標サステインパルス数決定手段により決定された目標サステインパルス数と、前記最大サステインパルス数との関係に基づいて、前記1フィールドの前記主表示ラインに対する前記副表示ラインの発光輝度比を定める発光輝度比決定手段63とを有する。

(もっと読む)

画像表示装置

【課題】製品コストを増大させることなく、画像の表示比率を変更可能な画像表示装置を提供する。

【解決手段】表示信号処理部40においては、入力ビデオ信号の周波数計測を行い、制御部20において入力ビデオ信号が16:9フォーマットのビデオ信号であるか否かを判定する。また、制御部20においては、ユーザにより選択された画面サイズを制御用メモリ30から読み出し、例えば、アスペクト画像表示が選択されている場合は、表示信号処理部40において、垂直拡大率をフル画像表示の垂直拡大率よりも小さくして、表示パネル50の表示領域の上端および下端に黒帯(垂直ブランキング部)を表示する、あるいは、表示信号処理部40において、水平拡大率をフル画像表示の水平拡大率よりも大きくして、表示パネル50に左右オーバースキャンで表示するように制御する。

(もっと読む)

信号処理回路および方法

【課題】複数の信号処理回路を用いた場合でも、1dot単位の表示位置調整や補正処理などを容易に行うことができるようにする。

【解決手段】マスタIC112−1およびスレーブIC112−2は、内蔵するレジスタを参照して、スキャンコンバータ111から入力されるODDデータおよびEVENデータのうち、どちらか一方および他方をそれぞれ選択し、選択した映像信号に対して、倍速変換処理を行い、さらに、内蔵するレジスタを参照して、一旦蓄積したデータの読み出し順および読み出し開始位置を制御する。マスタIC112−1およびスレーブIC112−2は、倍速後の映像信号に対して、LCDパネル114用の信号補正処理を行い、S/Hドライバ113−1および113−2にそれぞれ出力する。本発明は、LCDパネルに表示させるための映像信号の信号処理を行う液晶表示システムに適用できる。

(もっと読む)

映像表示装置

【課題】動画ボケを抑制しつつフリッカ現象の発生を抑えて動画像表示の表示品位を向上させることが可能な映像表示装置を実現する。

【解決手段】本発明の映像表示装置は、複数の画素からなる、複数の水平ラインで構成されるLCDパネル11と、前記LCDパネル11の各水平ラインに対し、入力された映像情報を映像情報表示期間内に表示する第一表示処理と、非映像信号を非映像表示期間内に前記映像情報と異なる階調数で表示する第二表示処理とを所定の周期で繰り返し行うゲートドライバ13と、前記所定の周期に対する前記非映像表示期間の時間比率に応じて、第二表示処理における前記階調数を制御する制御回路15とを備える。

(もっと読む)

パネルインターフェイス装置、画像処理用LSI、デジタルカメラおよびデジタル機器

【課題】パネルインターフェイス制御装置として、パネル表示用に新たに映像データを作る必要をなくし、かつ、表示パネルの種類変更に柔軟に対応可能にする。

【解決手段】データ変換回路8およびRGBフィルタ回路12は、プログラマブルであり、表示用デジタル映像信号7に対して、表示パネルの画面サイズに合わせて、水平方向および垂直方向に、拡大または縮小処理を行う。インターフェース部16は、RGBフィルタ回路12の出力を、表示パネルに映像データ13として出力する。

(もっと読む)

表示装置の駆動回路及び画像データ変換方法

【課題】表示形式が異なる複数の表示装置を同時に駆動することができるとともに、ラインメモリのメモリ容量を低減して回路規模を小さくする。

【解決手段】ラインメモリ41は、1水平走査ラインの画素数720個に対して、1/3の画素数240個分のメモリ容量しか有していない。したがって、ラインメモリ41は720画素分の画像データを一度に記憶することができない。そこで、1水平期間に、画像データをラインメモリ41に3回に分けて書き込むようにした。これにより、1回の書き込みにより240画素分の画像データがラインメモリ41に書き込まれる。そして、ラインメモリ41からの画像データの読み出しは、例えば、120画素分の画像データの書き込みが終了した時点から開始し、その後、時系列的に読み出しを継続する。

(もっと読む)

1 - 20 / 55

[ Back to top ]