Fターム[5J055AX07]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153) | スイッチの基本性能向上 (933) | 駆動能力の増大 (68)

Fターム[5J055AX07]に分類される特許

1 - 20 / 68

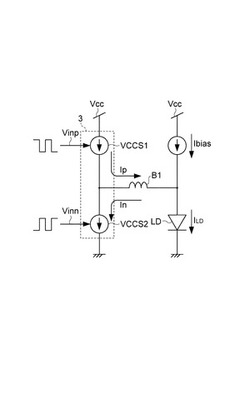

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子に接続されている逆相信号処理回路と、アノードが接続されている端子に接続されている第1及び第2の電圧制御電流源回路を備える。第1の電圧制御電流源回路には、正相信号Vinpに対応する電圧及び逆相信号Vinnの逆相に対応する電圧が入力され、第2の電圧制御電流源回路には、逆相信号Vinnに対応する電圧及び正相信号Vinpの逆相に対応する電圧が入力される。

(もっと読む)

電圧スイッチ回路

【課題】低濃度ドープのPMOSトランジスタを用いて、高電圧ストレスに耐える電圧スイッチ回路を提供する。

【解決手段】該電圧スイッチ回路は、出力回路210、第1の電圧降下制御回路220、第2の電圧降下制御回路230、第3の電圧降下制御回路240、および入力回路250を備えている。また、高電圧源HVの電圧振幅は、基準電圧源Vrefの電圧振幅よりも高く、基準電圧源Vrefの電圧振幅は、論理電圧源VDDの電圧振幅よりも高い。

(もっと読む)

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

レベルシフト回路及びそれを用いたドライバと表示装置

【課題】低振幅の入力信号を高速に高振幅信号に変換するレベルシフト回路を提供する。

【解決手段】第1及び第2の出力端子の一方を第1電圧レベルに設定する第1のレベルシフト回路10と、第2の電圧端子と、前記第1及び第2の出力端子との間に接続され、前記第1及び第2の出力端子の他方を第2電圧レベルに設定する第2のレベルシフト回路20と、第1の制御信号に基づき、第1及び第2の入力信号が第1及び第2の入力端子に入力される時点で前記第2電圧レベルとされる一つの出力端子について、前記一つの出力端子と第2の給電端子間の電流経路を、前記第1及び第2の入力信号が前記第1及び第2の入力端子に入力される時点を含む所定期間、切断し、前記所定期間の後、前記一つの出力端子と前記第2の給電端子間の電流経路の切断を解除する制御を行う手段を備え、前記第1及び第2の出力端子の出力振幅は、前記第1及び第2の入力信号の振幅よりも大きい。

(もっと読む)

半導体スイッチ及びスイッチ装置

【課題】電流変動が大きな箇所の半導体スイッチにおいて耐電流と損失を最適化する。

【解決手段】電気的特性及び種類が互いに異なるFET11とIGBT12を並列接続することで半導体スイッチ1aを形成する。端子5及び6間を接続するとき、FET11及びIGBT12は同時にオンされる。端子5及び6間の電流が小電流であるときには、FET11の内部抵抗がIGBT12よりも小さいため、FET11側に優先的に電流が流れて低損失が実現される。端子5及び6間の電流が増大するにつれて、FET11では発熱が内部抵抗増大を招くがIGBT12では内部抵抗が殆ど変化しないため、或る電流値以上では、IGBT12側に優先的に電流が流れる。結果、大電流がFET11側に流れることによるFET11の劣化又は破損が回避される。

(もっと読む)

半導体素子駆動装置及び方法

【課題】並列に駆動される複数の半導体素子の特性差によって生じる、ターンオンやターンオフ時のスイッチングにおける電流の偏りを緩和すること。

【解決手段】電圧変換器14は、IGBT13−1乃至13−3の各々のエミッタセンス電流を電圧信号に変換する。平均値演算器17や誤差演算器18等の演算器は、LPF15から出力される、IGBT13−1乃至13−3の各々に対応する電圧信号の平均値を求め、それぞれの電圧信号についての平均値に対する誤差を演算する。PWM波形生成部11は、IGBT13−1乃至13−3の各々を駆動するための駆動信号(パルス信号)を出力する。差動増幅器12の各々の駆動信号を、当該IGBT13−1乃至13−3の各々に対応する誤差に基づいて調整して、当該IGBT13−1乃至13−3の各々に供給する。

(もっと読む)

表示装置

【課題】表示装置の走査信号線の駆動回路において、走査信号線の出力波形なまりを改善し、表示品質を高めた表示装置を提供する。

【解決手段】表示装置は、複数の信号線Gnに対して、順に画素トランジスタを導通させる電位であるアクティブ電位を印加する駆動回路210を備え、前記駆動回路210は、前記複数の信号線のうちの一の信号線である出力信号線の一端に、より上位の前記出力信号線において出力されるアクティブ電位が入力されることに起因して、クロック信号を印加してアクティブ電位を出力させる主駆動回路240と、前記出力信号線の他端、及び前記クロック信号の信号線が、ソース/ドレインを介して接続されたトランジスタである補助トランジスタを含む補助駆動回路250と、を有する。

(もっと読む)

出力バッファー回路

【課題】出力バッファーの面積・体積・部品点数の増加を抑制するとともに、ドライブ能力を向上させることが可能な出力バッファー回路を提供する。

【解決手段】第一駆動信号LINを伝達する第一入力経路4a、第二駆動信号RINを伝達する第二入力経路4b、第一入力経路4aと対応する第一出力バッファー6a及び第二入力経路4bと対応する第二出力バッファー6bを備える出力バッファー回路1において、入力経路切り替え手段8が、ステレオモード及びモノラルモードのうち、モノラルモードでは、第一入力経路4aと第一出力バッファー6a及び第二出力バッファー6bとを電気的に接続させ、出力経路切り替え手段10が、第一出力バッファー6a及び第二出力バッファー6bと、第一入力経路4a及び第一出力バッファー6aと対応する第一負荷2aとを、電気的に接続させる。

(もっと読む)

高周波スイッチ

【課題】高周波スイッチの歪特性の劣化を抑止することができる高周波スイッチを提供する。

【解決手段】アンテナ110へ送信信号が出力される共通ポートCXと、送信信号が入力される送信ポートTX1、TX2と、複数の送信ポートと共通ポートとの間にそれぞれ接続され、各送信ポートから共通ポートへの送信信号を導通または遮断する複数のスイッチ部100A、100Bと、を有し、スイッチ部はシリコン基板に形成された一以上のMOSFETTSWを有し、MOSFETのうち共通ポートに接続されたもののボディ端子と共通ポートに接続された端子との間にキャパシタが接続される。

(もっと読む)

スイッチ装置および試験装置

【課題】入力電圧範囲の大きな半導体スイッチ装置を提供する。

【解決手段】外部から入力される制御電圧に応じて第1端子および第2端子間を電気的に接続または切断するスイッチ装置であって、第1端子および第2端子の間にソースおよびドレインが接続され、当該スイッチ装置に入力される入力電圧とゲート電圧との差に応じてオンまたはオフとなるメインスイッチと、制御電圧および入力電圧に応じて第1基準電圧を電圧シフトさせた駆動電圧をメインスイッチのゲートに供給する制御部と、を備えるスイッチ装置を提供する。

(もっと読む)

バッファ回路

【課題】TFT特性のばらつきにかかわらず画像ムラがなく、高精細・高解像度の良好な画像を得ることができる半導体表示装置の駆動回路および半導体表示装置を提供する。

【解決手段】半導体表示装置はソース信号線側駆動回路と、ゲイト信号線側駆動回路とを有し、駆動回路はシフトレジスタ回路からのタイミング信号をバッファする複数のインバータ回路を有するバッファ回路を有し、インバータ回路は複数のインバータ回路を並列に接続して構成される。

(もっと読む)

交流スイッチ

【課題】高耐圧の用途に適用可能な交流スイッチ(半導体リレー)を提供する。

【解決手段】交流スイッチ1は、ソース(S)同士を接続した第1化合物半導体MOSFET11および第2化合物半導体MOSFET12と、第1化合物半導体MOSFET11のドレイン(D)に接続された第1出力端子13と、第2化合物半導体MOSFET12のドレイン(D)に接続された第2出力端子14とを含む。交流スイッチ1は、オフ時の第1出力端子13および第2出力端子14の間の耐圧が400V以上(より好ましくは600V以上)であり、オン時の第1出力端子13および第2出力端子14の間の抵抗が20mΩ以下(より好ましくは10mΩ以下)である。

(もっと読む)

半導体スイッチ回路

【課題】低周波帯域において線形性劣化のない半導体スイッチ回路を提供する。

【解決手段】入出力端子間に直列にソースおよびドレインを接続した1又は2以上の電界効果トランジスタと、電界効果トランジスタのゲートに接続した抵抗を備えた半導体スイッチ回路において、電界効果トランジスタのゲート−ドレイン間およびゲート−ソース間に、キャパシタをそれぞれ接続可能とした。

【効果】FETのゲート−ドレイン間およびゲート−ソース間すべてにキャパシタを接続したことにより、従来より低い周波数帯域においてゲート電極に接続する抵抗よりFETのインピーダンスが十分低くなるため、線形性を向上させることが可能となる。

(もっと読む)

バッファリング回路および増幅回路

【課題】 回路のダイナミックレンジを圧迫しないと共に、チップサイズの増大を抑制することができるバッファリング回路及び増幅回路を提供する。

【解決手段】 入力端子及び出力端子を有するバッファリング回路でドレインが第1電圧ラインに接続され、ソースが前記出力端子に接続され、ゲートが前記入力端子に接続された第1プルアップドライバと、ソースが前記出力端子に接続され、ゲートが前記入力端子に接続された第2プルアップドライバと、前記第2プルアップドライバのドレインに定電流を供給する定電流回路と、前記出力端子と第2電圧ラインとの間に配置されたプルダウンドライバとを備え、前記プルダウンドライバは、前記定電流回路の定電流から前記第2プルアップドライバに流れる電流を減じた差電流に基づいた電流を流すように構成されている。

(もっと読む)

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

電流スイッチ回路及びそれを用いたD/Aコンバータ、半導体集積回路及び通信機器

【課題】電流加算型D/Aコンバータに用いられる電流スイッチ回路において、低電源電圧時にしきい値電圧の低いトランジスタを用いた際に課題となるダイナミックレンジの低下を改善し、出力電圧範囲を大きく取る。

【解決手段】電流スイッチ回路1は、差動スイッチ12を構成する第1及び第2のトランジスタTr121、Tr122を有する。しきい値電圧制御回路5は、その出力端子Vboutから前記差動スイッチ12を構成する2個のトランジスタTr121、Tr122のサブストレート端子に出力するサブストレート電圧を制御して、前記差動スイッチの2個のトランジスタのしきい値電圧を制御する。従って、電流スイッチ回路1の電源電圧を低減させても、特性劣化を生じることなく、差動スイッチ12内の2個のトランジスタのしきい値に依存する電流スイッチ回路1の出力電圧範囲を大きく取ることができる。

(もっと読む)

半導体集積回路、半導体集積回路の駆動方法、表示装置および電子機器

【課題】高耐圧化可能な半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路は、電源電位と接続された出力ノードと、出力ノードと電源電位より低電位である接地電位との間に直列に接続された第1のnチャネル型トランジスター、第2のnチャネル型トランジスターおよび第3のnチャネル型トランジスターを有し、第1のnチャネル型トランジスターの一端は、接地電位に接続され、他端は、第2のnチャネル型トランジスターの一端に接続され、ゲート端子は、入力ノードに接続され、第2のnチャネル型トランジスターの他端は、第3のnチャネル型トランジスターに接続され、ゲート端子は、電源電位と接地電位との間に位置する第1中間電位に接続され、第3のnチャネル型トランジスターの他端は出力ノードに接続され、ゲート端子は電源電位に接続されている。

(もっと読む)

アンテナスイッチ回路及び通信端末

【課題】許容電力と挿入損出との特性を両立させるとともに、アンテナスイッチ回路の小型化を可能とし、且つスイッチング状態の更なる安定化を図ることができるようにする。

【解決手段】本発明によるアンテナスイッチ回路は、送信ポートとアンテナポートとの間に直列に接続された直列トランジスタ回路と、前記送信ポートと前記アンテナポートとの間に並列に接続された並列トランジスタ回路と、前記送信ポートと前記並列トランジスタ回路との間に設けられ、インピーダンス変換を行うことによって、前記送信ポートから入力された送信信号の電圧振幅を所定の変換比率で縮小するインピーダンス変換回路とを備え、前記インピーダンス変換回路は、前記並列トランジスタ回路に出力される端子間電圧が当該並列トランジスタ回路の閾値以下となるように前記所定の変換比率が設定されていることを特徴とする。

(もっと読む)

スイッチ回路

【課題】シリーズFETおよびシャントFETとして4端子NMOSFETを用いるSPSTスイッチ回路では、シリーズFETがオン状態で、シャントFETがオフ状態のときに、SPSTスイッチ回路はオン状態になる。FETのバックゲートには寄生ダイオードが存在し、入力交流信号電圧が所定の閾値を超えると、寄生ダイオードがオン状態になる。その結果、SPSTスイッチ回路はスイッチ・デバイスとしての線形動作を維持できなくなり、挿入損失特性やゆがみ特性が悪化する場合がある。

【解決手段】FETのバックゲートに、バイアス電圧を印加するためのバイアス電源を設ける。このバイアス電源として、DC−DC変換回路を用いることで、SPSTスイッチ回路をシリコン半導体チップ化することが容易になる。

(もっと読む)

半導体集積回路、半導体集積回路の駆動方法、電子機器および電子機器の駆動方法

【課題】高耐圧化可能な半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路は、第1電位ノード〔VDD〕と接続された第1ノード〔VOUT〕と、第1ノード〔VOUT〕と第1電位ノードより低電位である第2電位ノード〔VSS〕との間に直列に接続された第1のnチャネル型トランジスタ〔NT1〕および第2のnチャネル型トランジスタ〔NT2〕を有し、第1のnチャネル型トランジスタ〔NT1〕の一端は、第2電位ノード〔VSS〕に接続され、他端は、第2のnチャネル型トランジスタの一端に接続され、ゲート端子は、第2ノード〔VIN〕に接続され、第2のnチャネル型トランジスタ〔NT2〕の他端は、第1ノード〔VOUT〕に接続され、ゲート端子は、第1電位ノード〔VDD〕と第2電位ノード〔VSS〕との間に位置する第1中間電位〔VM1〕に接続されている。第2のnチャネル型トランジスタにより分圧され、各トランジスタに印加される電圧を低減できる。

(もっと読む)

1 - 20 / 68

[ Back to top ]