Fターム[5J055DX59]の内容

Fターム[5J055DX59]の下位に属するFターム

H型ブリッジ (54)

Fターム[5J055DX59]に分類される特許

1 - 20 / 36

半導体装置

【課題】ハイサイド駆動回路が負バイアス駆動を行いつつ、ブートストラップコンデンサによりハイサイド駆動回路に駆動電圧を供給することができる半導体装置を得る。

【解決手段】基準電圧回路3は、ハイサイド駆動回路1の高圧端子VBの電圧と低圧端子VEの電圧との間の基準電圧を生成して、ハイサイドスイッチング素子Q1とローサイドスイッチング素子Q2の接続点に供給する。充電用スイッチング素子Q3のドレインがハイサイド駆動回路1の低圧端子VEに接続され、ソースが接地されている。

(もっと読む)

微小電気機械システム(MEMS)アレイを含む電力切替システム

【課題】微小電気機械システム(MEMS)アレイを含む電力切替システムを提供すること。

【解決手段】切替システム(4)は、ダイオードブリッジを形成する複数のダイオードと、複数のダイオードに接近して結合された微小電気機械システム(MEMS)スイッチアレイ(12)とを含む。MEMSスイッチアレイ(12)は(M×N)アレイをなして電気的に接続される。(M×N)アレイは、第2のMEMSスイッチ脚部(44)に並列に電気的に接続された第1のMEMSスイッチ脚部(40)を含む。第1のMEMSスイッチ脚部(40)は直列に電気的に接続された第1の複数のMEMSダイを含み、第2のMEMSスイッチ脚部(44)は直列に電気的に接続された第2の複数のMEMSダイを含む。

(もっと読む)

電子装置

【課題】駆動信号がスイッチング素子のオフを指示しているにもかかわらず、制御端子の電圧が低下せず、スイッチング素子をオフできない場合であっても、スイッチング素子の熱破壊を防止できる電子装置を提供する。

【解決手段】制御回路は、正常時に、オン駆動用FET121aがオフするタイミング(t6)、オフ駆動用FET122aがオンするタイミング(t7)、及び、オン保持用FET123aがオンするタイミング(t9)の後であって、駆動信号がIGBT110dのオン指示からオフ指示に切替わるタイミング(t5)から一定の時間Toffの経過後に、オン保持用FET123aをオンする(t10)。そのため、オン駆動用FET121aがオン故障し、駆動信号がIGBT110dのオフを指示しているにもかかわらずIGBT110dをオフできない異常状態であっても、IGBT110dを確実にオフできる。従って、IGBT110dの熱破壊を防止できる。

(もっと読む)

負荷駆動装置、画像形成装置、負荷駆動方法およびプログラム

【課題】共振を利用し、容量性負荷の両端に逆位相の電圧パルスを印加可能として消費電力を低減する。

【解決手段】外部容量53と、コイルL1〜L3と、負荷容量52と外部容量53とコイルL1とを接続して第3電極から外部容量53に電荷を放電し、外部容量53への放電完了後に負荷容量51と負荷容量52とコイルL3とを接続して端子1−Aから端子2−Aに電荷を放電し、端子2−Aへの放電完了後に負荷容量51と外部容量53とコイルL1とを接続して外部容量53から端子1−Bに電荷を放電することにより、逆位相のパルス電圧を印加するSW駆動部と、を備える。

(もっと読む)

スイッチングトランジスタの制御回路およびそれを用いた電力変換装置

【課題】消費電力を抑制しつつ、ハイサイドトランジスタの誤動作を防止可能な制御回路を提供する。

【解決手段】制御回路12はハイサイドトランジスタM1を制御する。負電圧回路20は、動作状態と停止状態が切りかえ可能であって、動作状態においてハイサイドトランジスタM1の低電位側端子(ソース)より低いローレベル駆動電圧V4を発生し、停止状態において消費電流が低下する。ハイサイド駆動回路14は、ハイサイドトランジスタM1のオン、オフを制御する制御信号G1を受け、制御信号G1がハイサイドトランジスタM1のオフを指示するとき、ハイサイドトランジスタM1の制御端子(ゲート)に、ローレベル駆動電圧V4に応じた駆動電圧VG1を印加する。制御装置8は、負電圧回路20の動作状態と停止状態を切りかえる。

(もっと読む)

スイッチング素子の駆動回路

【課題】ブリッジ回路を構成する高速スイッチング素子を駆動対象とする場合でも、セルフターンオンの発生を防止できる駆動回路を提供する。

【解決手段】SJ−MOSFETであるNチャネルMOSFET3H,3LによりHブリッジ回路1を構成する場合に、駆動回路21を、NチャネルMOSFET3のソースとゲートとの間に磁気結合構造22を設け、NチャネルMOSFET3Hがターンオンした際に、オフ状態に維持されるNチャネルMOSFET3Lの寄生ダイオード5Lに短絡電流が瞬間的に流れると、NチャネルMOSFET3Lのソースに発生する電圧変動に基づいてゲートに誘導される電圧変動を打ち消すため、磁気結合構造22Lを、PNPトランジスタ8LのコレクタとNチャネルMOSFET3のゲートとの間を接続する駆動側配線24Lを、NチャネルMOSFET3Lのソース配線23Lに対して同相で磁気結合させて構成する。

(もっと読む)

双方向スイッチのゲート駆動装置

【課題】インバータ等に適用される半導体デバイスとし単方向デバイスを適用した場合に、負荷からの還流電流が流れるタイミングは、還流ダイオードを通して流れるためダイオードにおける損失を取り除けないという課題があった。

【解決手段】第一ゲート端子2、第二ゲート端子3、ドレイン端子4、ソース端子5を備え、第一ゲート端子2、第二ゲート端子3を各オンオフすることで4つの動作モードを有する双方向スイッチ1を使用し、還流電流が流れるタイミングに応じて、第三モードで通電するように前記第一ゲート端子2、および第二ゲート端子3を駆動させる同期制御手段を備えるので、還流ダイオードによる損失を無くすことができ、損失が少なく効率の良いインバータを提供できる双方向スイッチの駆動方法を提供する。

(もっと読む)

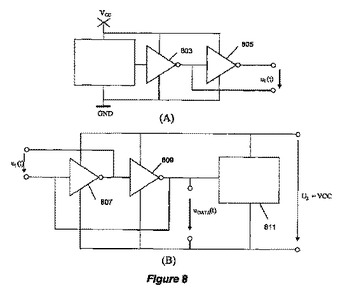

選択的にAC結合又はDC結合されるように適合される集積回路

【解決手段】

集積回路は、結合点で外部デバイスに選択的にAC結合又はDC結合されるように適合される。集積回路は、AC結合のために結合キャパシタを介して結合点に接続される第1のコネクタと、DC結合のために結合点に接続される第2のコネクタと、集積回路がデバイスにDC結合される場合に第1及び第2のコネクタ並びにそれにより結合キャパシタを選択的に短絡させるスイッチと、を含む。スイッチは、第1及び第2のコネクタの間で相互接続されるスイッチ制御MOSFETを備えるMOSFETブリッジであってよく、スイッチ制御MOSFETは、そのゲートでスイッチ制御MOSFETをオンにするためのモード状態信号を受信しそれにより、集積回路がデバイスにDC結合される場合にMOSFETブリッジを短絡させてよい。MOSFETブリッジはまた、高い外部電源電圧からスイッチ制御MOSFETを保護するためにスイッチ制御MOSFETと直列に接続される幾つかの動的にバイアスされるnMOSFETと、スイッチ制御MOSFETと並列に接続される幾つかの動的にバイアスされるpMOSFETと、を含む。

(もっと読む)

出力回路

【課題】貫通電流を防止する。

【解決手段】ローサイドオフ検出回路10は、ローサイドトランジスタM2のゲート信号SGLを所定の第1レベルTHLと比較することによって、ローサイドトランジスタM2がオフしたことを示すローサイドオフ検出信号S1を生成する。ローサイド検出トランジスタMSLは、ローサイドトランジスタM2と同型であり、そのソースが接地端子108に接続され、そのゲートにローサイドトランジスタM2のゲート信号SGLを受ける。第1抵抗R11は、ローサイド検出トランジスタMSLのドレインと電源端子106の間に設けられる。第1バイパス回路12は、第1抵抗R11と並列に設けられ、制御信号SINがローサイドトランジスタM2のオフを指示するレベルをとるときに導通し、オンを指示するレベルをとるとき遮断する。ローサイド検出トランジスタMSLのドレインの信号が、ローサイドオフ検出信号S1として出力される。

(もっと読む)

信号処理回路、出力方法、信号処理方法及び信号処理システム

信号処理回路は入力インバータ及び出力インバータを含む。インバータの各々は、入力整流信号を受信する信号入力部と、反転した出力整流信号を提供する信号出力部と、整流されたdc出力電圧を増幅する一対の電圧出力部とを有する。第1の回路入力端子は、入力インバータの出力及び出力インバータの入力に接続される。第2の回路入力端子は、入力インバータの入力及び出力インバータの出力に接続され、信号入力端子はデータの成分を有する入力信号を受信する。電源出力端子のペアがインバータの電圧出力端子に接続され、整流されたdc電源出力を提供する。第1の回路出力端子は或る電源出力端子に接続され、第2の回路出力端子は別の電源出力端子に接続され、それら回路出力端子はデータ成分を有する出力信号を提供する。  (もっと読む)

(もっと読む)

短絡検査装置、および負荷駆動装置

【課題】出力バッファ回路を構成する各出力トランジスタの破損や劣化を回避しつつ、短絡の有無を検査することを可能にする。

【解決手段】高電位電源線と低電位電源線との間に4個の出力トランジスタをブリッジ接続してなる出力段を有するアンプにて、高電位電源線と、この出力段の一方の出力端子OUTMとの間に抵抗R1およびスイッチSW1を直列に介挿するとともに、出力端子OUTMと低電位電源線との間に抵抗R2およびスイッチSW2を直列に介挿する。そして、上記各出力トランジスタをオフにして、スイッチSW1をオフに、かつスイッチSW2をオンにした場合に出力端子OUTMの電圧が閾値電圧を超えているか否かにより天絡の有無を判定し、スイッチSW1をオンに、かつスイッチSW2をオフにした場合に出力端子OUTMの電圧が閾値電圧を下回っているか否かにより地絡の有無を判定する。

(もっと読む)

PWM信号生成回路、D級増幅器及びその駆動方法

【課題】クラスD増幅器へのPWM信号の印可のオン/オフ時にポップノイズを発生させないこと。

【解決手段】パワー・オン状態になる又はアン・ミュート状態にされたことを示す第1状態を、またはパワー・オフにされ又はミュート状態にされる第2状態を検出する。第1状態検出時、それぞれ漸増する幅を有する複数のパルスとその後のデューティ50%のパルス列を含む差動PWM信号を生成してマルチプレクサ経由で増幅器に送り、オーディオ・プロセッサの出力が安定状態になるとこれを増幅器にマルチプレクサ経由で送る。第2状態検出時、オーディオ・プロセッサの出力が安定状態の場合に、それぞれ漸減する幅を有する複数のパルスとその後の無信号のパルス列を含む差動PWM信号を生成し、同時に、この生成したパルスをマルチプレクサを介して増幅器に送る。ここで、漸増/漸減するパルスのパルス数と各幅は本発明に開示した方程式を満足する関係にある。

(もっと読む)

駆動回路

【課題】電力ロスを低減しつつセンサ回路に供給される電圧の安定化を図ることができるセンサ駆動回路を安価に提供する。

【解決手段】電圧検出回路12が、ブリッジ回路Bに供給される交流電圧を分圧した電圧を基準電圧Vrefだけシフトアップした電圧を出力する。第1比較回路13が、電圧検出回路12により出力された電圧と第1比較電圧Vc1とを比較して、ブリッジ回路Bに供給される正の交流電圧の大きさが電圧Vthを越えないように第1トランジスタQ1を制御する。第2比較回路14が、電圧検出回路12により出力された電圧と第2比較電圧Vc2とを比較して、ブリッジ回路Bに供給される負の交流電圧の大きさが電圧Vthを越えないように第2トランジスタQ2を制御する。

(もっと読む)

スイッチング制御回路

【課題】ハーフブリッジ回路を構成する2つのスイッチング素子を共にオンさせるような2つのパルス信号が入力された場合であっても、2つのスイッチング素子が同時にオンすることを確実に防止すること。

【解決手段】第1パルス信号と第2パルス信号に基づいて、第1出力端子(DRV1)4からP型MOSFET(MOS1)10に第1駆動信号が出力され、第1パルス信号と第2パルス信号に基づいて、第2出力端子(DRV2)5から第2スイッチング素子であるN型MOSFET(MOS2)11に第2駆動信号が出力されるように構成され、保護回路20によりP型MOSFET(MOS1)10及びN型MOSFET(MOS2)11のうちの少なくとも一方がオフされるようにした。

(もっと読む)

ハーフブリッジ回路

【課題】ハイサイドFETスイッチとローサイドFETスイッチを備えたハーフブリッジ回路において、ゲート容量によるエネルギーロスを低減する。

【解決手段】ハーフブリッジ回路10は、直列接続されたハイサイドFETスイッチFET1及びローサイドFETスイッチFET2と、両FETスイッチの各ゲート容量を充放電して交互にオンオフするためのハーフブリッジドライバ12とを備え、両FETスイッチの接続点111に出力を発生する。ハーフブリッジドライバ12は、FETスイッチのゲート容量を充電するための電源VGと、FETスイッチがターンオフするとき、そのFETスイッチのゲート容量に充電されている電荷を放電し、そのエネルギーを電源VGに回生するためのトランスTR2、TR3とを備えた。これにより、ゲート容量によるエネルギーロスが低減され、FETスイッチのスイッチング周波数が高周波であっても、発熱が防止され高効率となる。

(もっと読む)

ハーフブリッジ回路

【課題】ハイサイドFETスイッチとローサイドFETスイッチを備えたハーフブリッジ回路において、ゲート容量によるエネルギーロスを低減する。

【解決手段】ハーフブリッジ回路10は、直列接続されたハイサイドFETスイッチFET1及びローサイドFETスイッチFET2と、両FETスイッチの各ゲート容量を充放電して交互にオンオフするためのハーフブリッジドライバ12とを備え、両FETスイッチの接続点111に出力を発生する。ハーフブリッジドライバ12は、一方のFET1がターンオフするとき、FET1のゲート容量に充電されている電荷を、トランスTR3を介して、ターンオンする他方のFET2のゲート容量に回生する。これにより、ゲート容量によるエネルギーロスが低減され、FETスイッチのスイッチング周波数が高周波であっても、発熱が防止され高効率となる。

(もっと読む)

アナログ/ディジタル変換装置

【課題】低オフセットで高価な電圧源を不要にし、低コスト化を可能にした高精度のアナログ/ディジタル変換装置を提供する。

【解決手段】3相交流電圧または交流電流の第1〜第3のアナログ検出値にそれぞれ同一の直流量を加算する手段と、前記直流量加算後の第1〜第3のアナログ検出値を第1〜第3のディジタル検出値に変換する片極性のA/D変換器33と、第1のA/D変換値を(2×第1のディジタル検出値−第2のディジタル検出値−第3のディジタル検出値)/3により演算し、第3のA/D変換値を(2×第3のディジタル検出値−第1のディジタル検出値−第2のディジタル検出値)/3により演算し、第2のA/D変換値を(−第1のアナログ/ディジタル変換値−第3のアナログ/ディジタル変換値)により演算する手段(ソフトウェア)と、を備える。

(もっと読む)

半導体集積回路、PWM信号出力装置、および電力変換制御装置

【課題】主にスイッチング素子での電圧降下による電圧誤差の補償と同時にPWM信号のスイッチングタイミングを管理でき、ソフト演算負荷の増減及びハード回路の追加部分を最小限に抑えることができるPWM変調形電力変換器の制御技術を提供する。

【解決手段】PWM信号を発生するPWM信号発生手段を有する半導体集積回路に、PWMタイマユニット100として、外部からPWM信号より遅延して入力するパルス信号のパルス幅をカウントするカウンタ103Aと、カウンタ103Aのカウンタ値をPWM信号に同期して取り込むレジスタ103Bと、外部から入力するパルス信号の源信号となるアナログ信号をデジタル信号に変換するA/D変換手段104とを備える。

(もっと読む)

過電流保護回路及び電力変換システム

【課題】スイッチング素子SWを流れる電流と相関を有する電気的な状態量(センス電圧)の検出に基づき、上記電流が閾値以上であると判断される場合に、スイッチング素子SWに過度の電流が流れる旨のフェール信号を生成するものにあって、ノイズの影響により誤ってフェール処理がなされること。

【解決手段】センス電圧が第1の閾値電圧vref1以上となる期間が規定時間Delay1以上となる場合、OR回路47の出力信号が論理「H」となることで、フェール信号生成回路53からフェール信号FLが出力される。ただし、スイッチング素子SWの駆動信号がオフである場合には、AND回路52の出力信号が論理「L」となるために、センス電圧が第1の閾値電圧vref1以上となる期間が規定時間Delay1以上となっても、フェール信号FLの生成が禁止される。

(もっと読む)

他励式インバータ回路及び液晶テレビジョン

【課題】スイッチ回路に複数のスイッチング素子を有しており、これら複数のスイッチング素子の何れかが短絡破壊された場合であっても、他のスイッチング素子の破壊を最小限に食い止める。

【解決手段】つまり、昇圧トランス26eの一次巻線にフルブリッジ回路により交流を印加するスイッチ回路26bと、発振のオンオフを指令する指令信号の伝送ラインから発振オンの指令信号が入力されると、スイッチ回路26bのスイッチ制御を行う制御回路C1と、スイッチ回路26bを構成するMOS−FETのゲートの端子電圧を監視し、ゲート電圧が所定の閾値を超えると参照電圧を出力する端子電圧監視回路51,52と、指令信号の伝送ラインに接続され、参照電圧をゲートに入力されるとゲート電流が流れてターンオンして、伝送ラインの指令信号を発振オフの状態にして、制御回路C1の発振を停止させるサイリスタ回路53と、を備えさせる。

(もっと読む)

1 - 20 / 36

[ Back to top ]