国際特許分類[H03K17/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698)

国際特許分類[H03K17/00]の下位に属する分類

スイッチ動作の高速化のための変形 (141)

完全導通状態を確保するための変形 (176)

過電流または過電圧に対するスイッチ回路の保護のための変形 (526)

最大許容被開閉電圧を増大させるための変形 (45)

最大許容被開閉電流を増大させるための変形 (21)

零交叉でスイッチ動作するための変形 (11)

物理量,例.温度,の変化を補償するための変形 (96)

混信電圧または混信電流を消去するための変形 (505)

スイッチの状態を表示するための変形 (2)

磁心スイッチ素子を所定の状態にリセットするための変形

供給電圧の投入時に所定の初期状態を確保するための変形 (300)

制御パルス受信後に一時的な阻止動作を行わせるための変形 (1)

スイッチ動作の前に時間遅延を導入するための変形 (58)

2以上のスイッチング動作を実行するために時間間隔の選択ができ,かつ,プログラムが完了された後,自動的に動作を終わらせるための変形 (24)

スイッチ動作の前に所定のしきい値を設けるための変形 (99)

特定の構成要素の使用によって特徴づけられたもの (2,578)

制御信号が発生される方法により特徴づけられるもの (510)

国際特許分類[H03K17/00]に分類される特許

21 - 30 / 605

2線式交流スイッチ

【課題】2線式交流スイッチの低消費電力化を実現する。

【解決手段】

交流電源と負荷とを結ぶ電路に挿入される2線式交流スイッチであって、スイッチ端子S1、S2と、スイッチ端子間のオンオフを制御するためのゲート端子G1、G2と、基板端子Subとを有し、スイッチ端子間に双方向に電流を流すことができ、スイッチ端子S1が交流電源1に接続され、スイッチ端子S2が負荷2に接続される半導体スイッチからなるメインスイッチ3と、メインスイッチの基板端子Subを接地するかフローティングにするかを切り替えるサブスイッチ9と、を備える。

(もっと読む)

接点入力回路

【課題】閾値電圧設定回路の抵抗器の開放故障に対するフェールセーフ性を確保し、且つ、検査信号がオフ制御されたときの消費電力を低減できる接点入力回路の実現。

【解決手段】接点入力回路10は、接点の開閉状態を示す入力信号が入力される正入力端子11と負入力端子12との間に、第1抵抗器R1、第3抵抗器R3及び第4抵抗器R4が直列接続されている。そして、直列接続された第3抵抗器R3及び第4抵抗器R4に対して、第2抵抗器R2、第1フォトカプラP1のフォトダイオードPd1及び第2フォトカプラP2のフォトトランジスタPt2が順方向に直列接続されてなる第2回路部16が並列接続されている。また、第4抵抗器R4に対して、第2フォトカプラP2のフォトダイオードPd2及び第3フォトカプラP3のフォトトランジスタPt3が順方向に直列接続されてなる第1回路部15が並列接続されている。

(もっと読む)

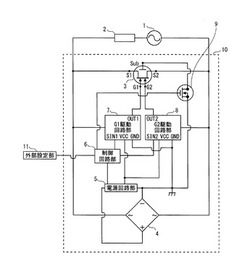

半導体スイッチの制御装置

【課題】半導体スイッチ素子に並列に接続される保護回路の異常を検出できる半導体スイッチ素子の制御回路を得る。

【解決手段】半導体スイッチに印加される電圧を抑制するために半導体スイッチに並列に接続された保護回路と、駆動回路の出力ゲート電圧が予め設定された電圧以上あることを検出し、半導体スイッチのオン・オフ状態を判別するゲート電圧検出手段と、半導体スイッチの主端子電圧を検出する主電圧検出手段と、駆動回路に与えられた駆動信号により、駆動指令がオン指令の場合はゲート電圧状態を選択し、駆動指令がオフ指令の場合は主電圧状態を選択する選択手段と、選択手段の出力を絶縁して低圧回路に伝達する第一の信号絶縁手段と、選択手段が選択して出力したゲート電圧状態・主電圧状態と半導体スイッチの駆動指令とを比較し、半導体スイッチの正常又は異常を判別する判別手段とを備える。

(もっと読む)

RFアンテナスイッチ回路、高周波アンテナ部品及び移動通信機器

【課題】スイッチング素子の個数を減らし、スイッチング素子を送受信時共有して、RFアンテナスイッチのサイズを減らすと共に、小型化及びワンチップ化にさらに応じるRFアンテナスイッチ回路、高周波アンテナ部品及び移動通信機器を提供する。

【解決手段】アンテナ1と、少なくとも一つの送信段2及び少なくとも一つの受信段3を備える複数の入出力段と、少なくとも一つの送信段2とアンテナ1側の共通ノード4、5との間の送信経路上に配置され、制御信号によって信号を伝達する少なくとも一つの送信スイッチブロック10と、受信段3と共通ノード4、5との間の受信経路上に配置され、制御信号によって伝達する少なくとも一つの受信スイッチブロック30、30a、30bと、スイッチング素子を共有して各々の送信及び受信動作と同期してオン動作する共用送受信スイッチブロック50とを含む。

(もっと読む)

スイッチモジュールおよびそれを用いた試験装置

【課題】半導体スイッチの低周波数領域での歪み特性を改善する。

【解決手段】制御ポートP3には、制御電圧VCが入力される。伝送路10は、入力ポートP1と出力ポートP2の間を接続する。シャントスイッチ20は、伝送路10と接地端子の間に設けられる。シャントスイッチ20は、そのドレイン、ソースの一方が伝送路10と接続され、そのドレイン、ソースの他方が接地端子に接続されるFET22を備える。第1抵抗R1は、FET22のゲートと制御ポートP3の間に設けられる。第2抵抗R2は、FET22のゲートと伝送路10の間に設けられる。

(もっと読む)

半導体スイッチ及び無線機器

【課題】高周波特性を改善した半導体スイッチ及び無線機器を提供する。

【解決手段】スイッチ部と、駆動回路と、電源回路と、を備えた半導体スイッチが供給される。前記スイッチ部は、共通端子と複数の高周波端子との接続を切り替える。前記駆動回路は、端子切替信号に基づいて前記スイッチ部に制御信号を出力する。前記電源回路は、温度に応じて変化する基準電位基づいて、前記制御信号の電位であって温度制御された第1の電位を生成して前記駆動回路に出力する。

(もっと読む)

電源回路

【課題】カレントミラー回路によって、複数の回路を電流駆動させる場合に、各回路の動作に対するばらつきを低減することができる電源回路を提供する。

【解決手段】FET1、2、3と、スイッチング素子であるスイッチ6〜9とで電源回路を構成している。FET1、2、3でカレントミラー回路を構成している。スイッチ6、7、8、9によって選択回路50が構成される。選択回路50は、スイッチ6〜9の切り替えにより、ミラー電流Ib2をオペアンプ4又はオペアンプ5のいずれかに供給し、さらに、ミラー電流Ib1をオペアンプ4又はオペアンプ5のいずれかに供給する。すなわち、ミラー電流Ib1とミラー電流Ib2とを入れ替えて交互に、オペアンプ4、5にそれぞれ供給する。

(もっと読む)

半導体スイッチ及びスイッチ装置

【課題】電流変動が大きな箇所の半導体スイッチにおいて耐電流と損失を最適化する。

【解決手段】電気的特性及び種類が互いに異なるFET11とIGBT12を並列接続することで半導体スイッチ1aを形成する。端子5及び6間を接続するとき、FET11及びIGBT12は同時にオンされる。端子5及び6間の電流が小電流であるときには、FET11の内部抵抗がIGBT12よりも小さいため、FET11側に優先的に電流が流れて低損失が実現される。端子5及び6間の電流が増大するにつれて、FET11では発熱が内部抵抗増大を招くがIGBT12では内部抵抗が殆ど変化しないため、或る電流値以上では、IGBT12側に優先的に電流が流れる。結果、大電流がFET11側に流れることによるFET11の劣化又は破損が回避される。

(もっと読む)

負荷駆動回路

【課題】簡単な構成で負荷オープン状態を検出することができる負荷駆動回路を提供する。

【解決手段】電源端子T1に入力される入力電圧Vinよりも低い基準電圧V1と出力端子T2の電圧Voutとを比較する第1のコンパレータ8と、スイッチング素子2がオフ状態で、且つ負荷オープン状態である場合に、出力端子T2の電圧Voutを基準電圧V1よりも高く、且つ入力電圧Vinよりも低いclamp電圧にクランプするクランプ回路7とを備えることにより、第1のコンパレータの出力によって、負荷オープン状態を検出する。また、入力電圧Vinよりも低く且つclamp電圧よりも高い基準電圧V2と出力端子T2の電圧Voutとを比較する第2のコンパレータ9を備えることにより、第1のコンパレータ及び第2のコンパレータ9の出力によって、負荷オープン状態と出力天絡状態とを検出する。

(もっと読む)

半導体装置及びそれを備えた半導体リレー装置

【課題】半導体装置及び半導体リレー装置において、製造コストを抑えつつ、CR積の値を小さくする。

【解決手段】双方向スイッチ1を構成する2つのMOSFETのうち、一方のMOSFET2に、化合物半導体で構成されたユニポーラ型化合物半導体装置を用い、他方のMOSFET3に、シリコンで構成されたSi−MOSFETを用いる。ここで、ユニポーラ型化合物半導体装置の中には、Si−MOSFETよりもCR積の値が小さいものが多く存在する。従って、一方のMOSFET2にユニポーラ型化合物半導体装置を用いたことにより、両方のMOSFET2、3にSi−MOSFETを用いた場合に比べて、装置全体のCR積の値を小さくできる蓋然性が高まる。また、Si−MOSFETよりも製造コストの高いユニポーラ型化合物半導体装置を2つ用いた場合に比べて、製造コストを抑えられる。

(もっと読む)

21 - 30 / 605

[ Back to top ]