Fターム[2G132AA00]の内容

電子回路の試験 (32,879) | 試験対象 (5,171)

Fターム[2G132AA00]の下位に属するFターム

論理回路 (2,000)

アナログデジタル混在回路(AD変換器等) (239)

アナログ回路 (164)

ASIC (97)

マルチチップモジュール (163)

機能ブロック(マクロセル)を有するもの (200)

バッファ (73)

ICカード等 (26)

実装基板 (349)

Fターム[2G132AA00]に分類される特許

1,841 - 1,860 / 1,860

試験装置及び試験方法

本発明の試験装置は、被試験デバイス15を試験する試験装置であって、被試験デバイス15に試験信号を印加するドライバ122と、印加された試験信号に対応して被試験デバイス15が出力した結果信号を、予め定められた基準電圧と比較するコンパレータ128と、被試験デバイス15に対して読込動作を行う場合に、試験信号の電圧を予め定められた電圧値に設定することにより、結果信号の伝送路をドライバ122に終端させる設定電圧出力部110とを備える。 (もっと読む)

回路性能の特性化

集積回路(IC)は、多数の埋込型テスト回路を含み、それらはすべて、テスト負荷に結合されたリング発振器を含んでいる。テスト負荷は、リング発振器における直接短絡か、または、ICの配線層のうちの1つを表わす配線負荷である。各埋込型テスト回路についてモデル方程式が定義され、各モデル方程式は、その関連する埋込型テスト回路の出力遅延を、フロントエンドオブライン(FEOL)パラメータおよびバックエンドオブライン(BEOL)パラメータの関数として特定する。次に、テスト回路出力遅延の関数としてのさまざまなFEOLパラメータおよびBEOLパラメータについて、モデル方程式を解く。最後に、測定された出力遅延値をこれらのパラメータ方程式に代入して、さまざまなFEOLパラメータおよびBEOLパラメータについての実際の値を生成し、それにより、懸念されるどの区域も迅速かつ正確に識別されるようにする。  (もっと読む)

(もっと読む)

集積回路、試験システム、および、集積回路からエラーデータを読み出すための方法

【課題】各集積回路を試験する場合に試験機の各接続チャネル数を低減できて、エラーの発生や、コストを抑制できる集積回路、試験システムおよび試験方法を提供する。

【解決手段】エラーデータが試験モードに応じて読み出され、上記エラーデータを、第1および第2データ出力部を介してそれぞれ出力できる集積回路を設ける。集積回路に試験回路を、第1読み込み命令が印加されるとき、エラーデータを第1データ出力部に出力し、第2データ出力部を高インピーダンスに切り替え、第2読み込み命令が印加されるとき、エラーデータを第2データ出力部に出力し、第1データ出力部を高インピーダンスに切り替えるように設ける。  (もっと読む)

(もっと読む)

試験装置及びケーブルガイドユニット

複数の光ファイバケーブルの曲率制限を満足させることができるケーブル布設技術を提供するを目的とする試験装置100は、被試験デバイスにテストパターンを印加する複数のテストボードを有するテストヘッド102と、テストヘッド102によるテストシーケンスを制御するメインフレーム104と、テストヘッド102とメインフレーム104とを光接続する複数のフラット型ケーブル200を有する光ファイバケーブルユニット106及び複数の光ファイバケーブル108と、光ファイバケーブルユニット106と複数の光ファイバケーブル108とを接続するダム107と、光ファイバケーブルユニット106が有する複数のフラット型ケーブル200間の周長差を吸収する周長差吸収装置110と、メインフレーム104が有するテストボード612に接続される光ファイバケーブル108を湾曲させて保持するケーブルガイドユニット112とを備える。 (もっと読む)

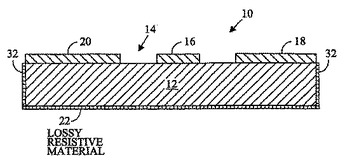

プローブテスト構造

デバイス検査用のキャリブレーション構造。  (もっと読む)

(もっと読む)

磁場測定プローブ

磁場を測定するプローブは、所定の選択された測定軸に沿う磁場を感知する少なくとも一個の磁気抵抗センサ(102,104、106)を備える。そのプローブは、一つの場所においてお互いが固定して接続された少なくとも二個の磁気抵抗センサ(102,104、106)であって、それらの選択された測定軸の角度がずらされるような前記の磁気抵抗センサを備え、かつそのプローブは、それらの選択された測定軸に沿う各センサにより測定された磁場を表わす信号を提供するために、各磁気抵抗センサ(102,104、106)に固有な出力端子を備える。  (もっと読む)

(もっと読む)

磁場測定プローブ

磁場を測定するプローブは、選択された測定軸に沿う磁場を感知する少なくとも一個の磁気抵抗または磁気誘導センサを備える。プローブは、その選択された測定軸が平行かつ、選択された測定軸に関して横方向に、互いにオフセットされるように、一つの場所において互いが固定して接続された少なくとも二個の磁気抵抗センサ14、16を備え、プローブは、その選択された測定軸に沿う各センサにより測定された磁場を表わす信号を提供するために、各磁気抵抗または磁気誘導センサに固有な出力端子を備える。  (もっと読む)

(もっと読む)

試験応答を選択的にマスクするための方法およびシステム

集積回路(10)を試験するための装置であって、集積回路(10)の一部である試験中の回路(14)からの試験応答を圧縮する圧縮器(22)と、試験中の回路と圧縮器(22)の間に結合される、試験中の回路(14)からの1つまたは複数の試験応答をマスクするためのマスキング回路(18)とを備える装置。マスキング回路(18)はさらに、圧縮済マスクデータを受信し、復元済マスクデータを供給するための復元回路を含む。  (もっと読む)

(もっと読む)

電流測定装置及び試験装置と、これに用いる同軸ケーブル及び集合ケーブル

測定第1端子と、測定第2端子との間を流れる被測定電流を測定する電流測定装置であって、一端が測定第1端子と電気的に接続され、他端が測定第2端子と電気的に接続された複数の1次コイルと、複数の1次コイルに流れる被測定電流に応じて、被測定電流を示す電圧を生じる2次コイルと、それぞれが複数の1次コイルのそれぞれに対応し、対応する1次コイルの一端と測定第1端子とを電気的に接続する信号線と、シールドとを有する複数の同軸ケーブルとを備え、同軸ケーブルのそれぞれは、信号線と、信号線を被覆する絶縁層と、絶縁層の外周に巻き付けられたテープ状の導電体を有する第1のシールドと、第1のシールドの外周に設けられた導電体により構成される第2のシールドとを有することを特徴とする電流測定装置を提供する。 (もっと読む)

温度制御装置及び温度制御方法

テストパターンによる被試験電子部品(2)の温度変化特性と等しいか又は似する温度変化特性を有するヒータ(112)を被試験電子部品に接触させながら被試験電子部品をコンタクト端子(132a,132b)へ押し付け、この状態で被試験電子部品にテストパターンを送出するとともに、当該テストパターンによる被試験電子部品の消費電力とヒータの消費電力との総和が一定値になるようにヒータの消費電力を制御する。 (もっと読む)

ゴールデンサンプルによるテスタ及びテストボードの較正

自動試験機器(ATE)における試験の実施において、RF(無線周波数)電力を正確に生成する及び測定することは、難題である。例示的な一実施例においては、増幅器(140)の入力及び出力特性を測定するのに使用される試験装置(100)において、試験プログラムパラメータを決定する方法が提供される。前記方法(200)は、前記試験装置の電源から増幅器(220)の入力までの入力損失を計算するステップと、入力損失補正係数を規定するステップとを有する。前記増幅器(220)の出力から前記試験装置の電力計までの出力損失が計算され、出力損失補正係数が規定される。前記入力損失補正係数(230)を使用して、実際の入力電力レベルが決定され、前記出力損失補正係数(230)を使用して、実際の出力レベルが決定される。  (もっと読む)

(もっと読む)

試験方法、通信デバイス、及び試験システム

本発明の通信デバイスの試験方法は、基準クロックに基づいて生成された試験信号を送信して受信する段階と、試験信号の期待値を基準クロックに基づいて発生する段階と、試験信号を遅延させる段階と、遅延された試験信号を期待値と比較して比較結果を出力する段階と、遅延時間を変化させながら、上記段階を繰り返し行い、遅延時間毎に比較結果を格納する段階と、遅延時間毎の比較結果に基づいて試験信号のアイ開口度を検出する段階と、検出したアイ開口度に基づいて通信デバイスの良否判定を行う段階とを備える。 (もっと読む)

電子部品の基準電圧の自己診断を行う方法及び回路装置

電子部品における基準電圧の自己診断方法を提供するため、この方法により、オンチップセットの形態で実施可能な、すなわち外部基準電圧源の必要のない基準電圧の自己診断のための回路装置が規定される。基準電圧(Uref)は、基準電圧(Uref)の被選択公称値(Uref.test)が設定されたポイントに極値を有する関数f(Uref)の変数とされ、自己診断において、基準電圧(Uref)及びそれぞれ正及び負の少量だけ基準電圧(Uref)と異なる他の2つのテスト電圧(Uref+ΔUref;Uref−ΔUref)に対して連続して関数の値が決定される。これらの値は、互いに比較され、テスト電圧(Uref+ΔUref;Uref−ΔUref)に対する関数の値が同じ方向性において基準電圧(Uref)に対する関数の値と異なる場合に合格信号を発生し、そうでない場合は不合格信号を発生する。  (もっと読む)

(もっと読む)

電子部品における基準電圧の自己診断方法及び装置

電子部品における基準電圧の自己テストの方法を提供し、この方法により、オンチップテストの形態で実現可能な、すなわち外部基準電圧源を不要とする基準電圧の自己テストの回路装置が規定される。基準電圧(Uref)は、電圧制御型発振器に供給される。この発振器の出力は、ウィーン−ロビンソンブリッジの入力を形成する。このブリッジの出力信号は、そのブリッジの平衡状態をチェックするために当該ブリッジへの入力に対するその位相シフトに関する位相検出器においてチェックされる。ウィーン−ロビンソンブリッジは、基準電圧(Uref)のために選択された公称値(Uref.tes)で発振器において発生される周波数(Ωref.test)で平衡を保つように設定され、ブリッジが平衡を保つと合格信号が発生され、それ以外は不合格信号が発生される。  (もっと読む)

(もっと読む)

欠陥解析を実行するための方法及びそのシステム

回路欠陥解析及びプロセス問題識別を実行するための方法は、テスト信号を回路に印加するステップと、テスト信号に応答して生成された応答信号を得るステップと、応答信号を参照情報と比較するステップと、比較するステップの結果に基づいて回路内の欠陥を分類するステップと、欠陥分類に基づいて、欠陥を引き起こした製造プロセスにおける問題を識別するステップとを有している。参照情報は、製造プロセス中に発生する可能性がある予め定義されたタイプの欠陥に対応する1つ又は複数の信号プロフィルを含むことができる。欠陥の分類は、応答信号が、信号プロフィルのうちの1つ又は複数内に入るかどうか判定することによって実行されることが好ましい。応答信号が2つ以上の信号プロフィル内に入る場合には、各プロフィルについて確率を決定することができる。次いで、欠陥は、その信号プロフィルがより高い確率を有する欠陥タイプに対応するものとして分類することができる。処理システムは、同様の方法を使用して、欠陥の分類及びプロセス問題識別を実行する。 (もっと読む)

半導体集積回路を試験するための試験機アーキテクチャ

モジュール式試験機アーキテクチャ(100)により、エンド・ユーザがスキャン・チェーン・モジュールおよびクロック・ドライバ・モジュールを組み合わせることができる。各モジュールは、同期バス(118)を介して相互接続され、それによって試験モジュール同士が互いに同期するのが可能であり、したがって、各モジュールは、試験全体におけるそのモジュールの部分を、他のモジュールによって行われる試験に対して適切な時間に実行することができる。このモジュールには、BISTドライバ・モジュール、データ取得モジュール(208)、ネットワーク化インターフェース・モジュール(202)、コントローラ・モジュール(204)、電流測定モジュール(210)、およびDCパラメトリクス・モジュールを含めることができる。

(もっと読む)

(もっと読む)

テストヘッド位置決めシステムと方法

負荷を支持するための装置は、空気装置と負荷の対向側面に連結される連結器を備える。連結器は、空気装置の作動に応答して、第1の軸と平行に負荷を移動させる。少なくとも1つの連結器は、第1の軸と直角の第2の軸を回転支点として負荷を回転させる。負荷は第1の軸方向に沿って移動するとともに第2の軸の回りにコンプライアント動作する。少なくとも1つの空気装置が第1の軸方向に沿った移動とともに第2の軸の回りのコンプライアンスを提供する。

(もっと読む)

(もっと読む)

検査用プローブ基板及びその製造方法

【課題】製造効率が良く、且つ半導体チップとの接触抵抗をより小さくして正確な検査を行なうことが可能である検査用プローブ基板及びその製造方法を提供すること。

【解決手段】銅箔を備えた基板に突起と該突起に接続する配線パターンとを形成する検査用プローブ基板の製造方法において、前記突起の形成は、Auボールをボンディングした後にAuワイヤをクランプしたキャピラリを移動することにより行ない、その後前記突起の上に第1のめっき及び第2のめっきを施したことにある。

(もっと読む)

スキャン多重化

【課題】DUT内のIC部品のテストのコスト効果及び時間効率を向上させる。

【解決手段】複数の状態データを各テスタメモリ位置(42及び44)に多重化することによって、スキャン動作の実効周波数を高くし、同時にメモリ容量を大きくすることができる。システム(10)は、テスト対象装置(DUT)(18)への入力刺激としての状態データのスキャンインシーケンス(14)と予測された状態データのスキャンアウトシーケンス(16)を提供するためのソースを含む。ベクトルプロセッサ(30)が、スキャンインシーケンス(14)と予測されたスキャンアウトシーケンス(16)を受け取り、多重化された状態データの交換を可能にする。多重化係数がmの場合には、装置サイクルレートをテスタサイクルレートのm倍にすることができる。多重化係数は、個々のテスタメモリ位置(42及び44)の記憶容量と、実効ベクトル交換レートをテスタサイクルレートのm倍にすることができるということに基づいて選択される。

(もっと読む)

ミリ波伝送線路の入出力端部接続構造

【課題】マイクロストリップ線路をコプレーナ線路に変換する、線路変換部を備えるミリ波伝送線路において、当該部位での伝送ロスを低減可能とするミリ波伝送線路の入出力端部接続構造を提供する。

【解決手段】コプレーナ線路構造体は信号線路と信号線路の両側に2本の接地線路とを備え、3本の線路の先端には押圧して電気的に接続できる先端電極を各々備え、ミリ波伝送線路の入出力端部接続構造には、マイクロストリップ線路の信号線路10と同一導体幅で延長して備えられる信号接触電極と必要最小限の接地線路用接触電極を形成する第1と第2のプローブ専用電極8と、第1、第2のプローブ専用電極へ電気的接続され、且つ信号線路10とは等価容量が小さくなるように所定に離れて配設され、且つマイクロストリップ線路の下面側のアース面と電気的に接続する第1、第2のバイアホールを備えるミリ波伝送線路の入出力端部接続構造。

(もっと読む)

1,841 - 1,860 / 1,860

[ Back to top ]