Fターム[4M104FF13]の内容

Fターム[4M104FF13]の下位に属するFターム

Fターム[4M104FF13]に分類される特許

21 - 40 / 2,637

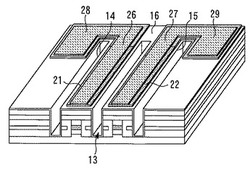

光半導体装置の製造方法

【課題】信頼性を向上させることができる光半導体装置の製造方法を得る。

【解決手段】n−InP基板1上に、分離溝13で互いに分離された光半導体素子14,15を形成する。光半導体素子14,15の上面に、Ptを含む電極21,22をそれぞれ形成する。電極21,22に電気的に接続された電極24を形成する。電極24を給電層とした電解メッキ法により電極21,22上にAuメッキ層26,27をそれぞれ形成する。Auメッキ層26,27を覆うレジスト23をフォトリソグラフィにより形成する。レジスト23をマスクとして電極24をエッチングして電極21と電極22を電気的に分離する。電極24を形成する際に、分離溝13内に電極24が形成されないようにする。

(もっと読む)

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、電流駆動能力の高い半導体基板およびその製造方法を提供することである。

【解決手段】本実施形態による半導体装置は、半導体基板を備える。第1導電型のFin型半導体層は、半導体基板上に形成されている。第1導電型のソース層および第1導電型のドレイン層は、Fin型半導体層の長手方向の両端に設けられている。ゲート絶縁膜は、Fin型半導体層の両側面に設けられている。ゲート電極は、Fin型半導体層の両側面にゲート絶縁膜を介して設けられている。第2導電型のパンチスルーストッパ層は、ゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は、ソース層およびドレイン層の下にある半導体基板の不純物濃度よりも高い。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】II族酸化物半導体を用いた半導体素子における新規な絶縁層形成技術を提供する。

【解決手段】半導体素子の製造方法は、(a)基板上方に、II族酸化物半導体層を成長させる工程と、(b)II族酸化物半導体層上に、窒素をドープしつつOリッチ条件での成長を行い抵抗率が105Ωcm以上のII族酸化物絶縁層を成長させる工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグに接続される配線間隔の縮小を可能にする半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板に第1の領域と第2の領域とを定義し、第1の領域に第1のサイズを持つ第1の素子を形成し、第2の領域に、第1のサイズとは異なる第2のサイズを持つ第2の素子を形成し、第1の素子及び第2の素子を覆うように半導体基板上に第1の層間絶縁膜を形成し、第1の領域上の第1の層間絶縁膜を貫通し第1の素子の一部を露出させる第1のコンタクトホールを形成し、第2の領域上の第1の層間絶縁膜を貫通し第2の素子の一部を露出させる第2のコンタクトホールを形成し、第1のコンタクトホール及び第2のコンタクトホールをそれぞれ埋める第1のコンタクトプラグ及び第2のコンタクトプラグを同時に形成する。

(もっと読む)

ポリメタルゲート電極を持つ半導体素子の製造方法

【課題】TiN膜及びバッファ層から形成されるバリアー膜を備えるポリメタルゲート電極を持つ半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に半導体基板側から順に積層された導電性ポリシリコン膜、第1金属シリサイド膜、バリアー膜、及び金属膜から形成されるポリメタルゲート電極と、を備える半導体素子である。バリアー膜は、第1金属シリサイド膜上に形成されるTiN膜と、TiN膜と金属膜との間に介在されるバッファ層と、を備える。

(もっと読む)

スーパージャンクション構造を有する半導体装置

【課題】高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることのない、スーパージャンクション構造を有する半導体装置を提供する。

【解決手段】n−型半導体層(第1導電型の半導体層)114と、活性領域R1に形成された複数の柱状埋込層118と、活性領域R1に形成されたショットキーバリアメタル層(第1電極層)132と、耐圧領域R2に形成された複数のガードリング層(環状柱状埋込層)124と、耐圧領域R2及び周辺領域R3に形成された絶縁層130とを備える、スーパージャンクション構造を有する半導体装置であって、周辺領域R3に形成された第2ガードリング層(第2環状柱状埋込層)136と、周辺領域R3に形成された環状導電層142とをさらに備える、スーパージャンクション構造を有する半導体装置100。

(もっと読む)

紫外線透過ゲート電極を有する電界効果トランジスタ

【課題】基板の自由度があり、待機時(光非照射時)の電力消費が小さく、また光照射時のS/Nが大きい受光素子を提供することである。

【解決手段】紫外線が透過する材料をFETの電極として用い、また、電子走行領域をAlGaNとGaNとのヘテロ界面等のGaN系膜同士のヘテロ界面とする。

(もっと読む)

保護素子、半導体装置及び半導体装置の製造方法

【課題】ヘテロ接合を利用した新規な保護素子を提供すること。

【解決手段】 半導体装置10の保護部36は、配線下層11Bと、配線下層11Bとは異なるバンドギャップを有する配線上層13を有している。配線上層13は、第1部位41と中間部位43と第2部位45を含んでいる。配線上層13と配線下層11Bの接合面に形成される2次元電子ガス層が、第1部位41と中間部位43の間で分離されており、第2部位45と中間部位43の間で分離されている。第1部位41と配線下層11Bの接合面に形成される2次元電子ガスが、ドレイン電極21に電気的に接続されている。第2部位45と配線下層11Bの接合面に形成される2次元電子ガスが、ソース電極28に電気的に接続されている。中間部位43と配線下層11Bの接合面に形成される2次元電子ガスが、ゲート電極25に電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体発光装置および半導体発光装置の製造方法

【課題】半導体膜に対するコンタクト層として機能するITO膜を有する半導体発光装置において、ITO膜と半導体膜との接触の増大を抑制することができる半導体発光装置およびその製造方法を提供する。

【解決手段】

半導体発光装置1は、発光層を含む半導体膜20と、半導体膜上に設けられたITO膜30と、ITO膜30の上面の一部および側面を覆う酸素吸着性を有する酸素吸着部80と、ITO膜30の上面に設けられた光反射性を有する反射電極40と、ITO膜30、酸素吸着部80および反射電極40からなる積層体を覆うキャップ層50と、キャップ層50上に接合層61を介して接合された支持基板60と、を含む。

(もっと読む)

半導体装置

【課題】複数のチャネルを有する窒化物半導体装置において、ノーマリオフかつ低オン抵抗を実現する技術を提供する。

【解決手段】第1の窒化物半導体層3,5,7と、第1の窒化物半導体層よりも禁制帯幅が大きい第2の窒化物半導体層5,6,8とが積層されたヘテロ接合体を少なくとも2つ以上有する窒化物半導体積層体10を備え、窒化物半導体積層体10に設けられたドレイン電極14と、ソース電極13と、ドレイン電極14とソース電極13の両者に対向して設けられたゲート電極15,16とを有し、ドレイン電極14とソース電極13は、窒化物半導体積層体10の表面または側面に配置され、ゲート電極15,16は、窒化物半導体積層体10の深さ方向に設けられた第1ゲート電極15と、該第1ゲート電極15と窒化物半導体積層体10の深さ方向の配置深さが異なる第2ゲート電極16とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク不良の発生を抑制でき、かつ薄型基板を用いることができる半導体装置およびその製造方法を提供する。

【解決手段】半導体チップ30を、半導体基板35の表層部に形成された第1導電型層34と、第1導電型層34の表面に形成されたゲート絶縁膜37と、ゲート絶縁膜37上に形成されたゲート電極38と、半導体基板35の主表面35a上に配置され、主表面35aの一部を露出させるコンタクトホール42が形成された層間絶縁膜41と、層間絶縁膜41上に配置され、コンタクトホール42を介して半導体基板35と接続されるアルミニウムを有する材料で構成される上部電極43と、上部電極43上に形成されたニッケルを有する材料で構成されるメッキ膜44と、半導体基板35の裏面35bに形成された下部電極46とを有する構成とする。そして、上部電極43のうちコンタクトホール42に形成されている部分の膜厚tを2μm以上にする。

(もっと読む)

半導体装置の製造方法

【課題】X線検出用フォトダイオード等においては、初期結晶材料として、裏面側に高濃度の不純物がドープされた単結晶ウエハ等を使用する場合がある。このような場合、裏面側不純物の外方拡散によるクロスコンタミネーション等を防止するために、予め、ウエハの裏面に、酸化シリコン膜等の不純物外方拡散防止膜等を形成しておく等の対策が講じられる。しかし、裏面に不純物外方拡散防止膜を形成する際に、ウエハの表面を損傷する等の問題が有る。

【解決手段】本願発明は、裏面に高濃度の不純物ドープ層を有する半導体ウエハの裏面に、不純物防止膜を形成するに当たり、まず、前記半導体ウエハの表面に酸化シリコン系絶縁膜等の表面保護膜を形成し、その状態で、前記裏面に、前記不純物防止膜を形成し、その後、ウエットエッチングにより、前記不純物防止膜を残した状態で、前記表面保護膜をほぼ全面的に除去するものである。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体装置

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良

を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設

けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い

表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度

が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギ

ャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キ

ャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノ

ーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

窒化物半導体装置の製造方法

【課題】低温の加熱処理によって、コンタクト抵抗の低いオーミック電極を形成することができる方法を提供する。

【解決手段】窒化物半導体層のオーミック電極形成領域に、インジウムあるいはゲルマニウムのような低融点金属7を積層し、低融点金属の融点近傍の低温で加熱処理することにより、窒化物半導体層中に低融点金属が拡散させ、合金層8を形成することによりオーミック接触を形成する。窒化物半導体層表面に残るインジウムあるいはゲルマニウムを除去した後、配線のための金属層9を形成する。

(もっと読む)

銅層および/または銅合金層を含む金属膜用エッチング液組成物およびそれを用いたエッチング方法

【課題】 本発明の課題は、銅層および/または銅合金層を有する金属膜や、該層と他の金属からなる層との積層膜を精度良くエッチングでき、液寿命が長いエッチング液組成物を提供することにある。

【解決手段】 本発明は、銅層および/または銅合金層を含む金属膜をエッチングするためのエッチング液組成物であって、銅(II)イオン、β−アラニンおよび水を含む、前記エッチング液組成物、ならびに、該エッチング液組成物を用いたエッチング方法に関する。

(もっと読む)

第III族金属窒化物−絶縁半導体ヘテロ構造電界効果トランジスタ

【課題】ヘテロ構造電界効果トランジスタに関して、電流崩壊、ゲートリークおよび高温信頼性などの課題を解消する。

【解決手段】高電子移動度トランジスタ(HEMT)、金属−絶縁半導体電界効果トランジスタ(MISFET)あるいはこれらの組み合わせなどの集積回路(IC)デバイスの装置、方法およびシステムであって、該ICデバイスは、基板102上で形成されたバッファ層104と、アルミニウム(Al)と窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つを含み、バッファ層104上に形成されたバリア層106と、窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含み、バリア層106上に形成されたキャップ108層と、キャップ層108に直接連結され、その層上に形成されたゲート118と、を含む。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】表面電極にめっき層を形成する際に、裏面電極に不必要なめっき層が形成されることによる裏面電極の電気抵抗の影響を抑制しつつ、表面電極にめっき層を欠陥無く形成できる半導体装置の製造方法を提供する。

【解決手段】表面1aに半導体素子の表面電極2が形成され、裏面1bに半導体素子の裏面電極が形成された半導体ウェハ1を用意する工程と、半導体ウェハ1の表面電極2にめっき層3を形成するめっき工程とを有する半導体装置の製造方法において、めっき工程では、表面電極2と半導体ウェハ1の側面1cとを露出した状態とし、かつ、半導体ウェハの裏面1bの全域を被覆した状態として、半導体ウェハ1をめっき液に浸してめっき層を形成する。

(もっと読む)

21 - 40 / 2,637

[ Back to top ]