Fターム[5F003BH93]の内容

バイポーラトランジスタ (11,930) | 電極、配線 (1,046) | 層間絶縁 (42)

Fターム[5F003BH93]の下位に属するFターム

多層オーバーレイ (16)

Fターム[5F003BH93]に分類される特許

1 - 20 / 26

半導体装置

【課題】 放熱性を改善したバイポーラトランジスタを有する半導体装置を提供することにある。

【解決手段】 複数のバイポーラトランジスタQuが配列される半導体装置であって、エミッタ配線L3は幅広部と細長部とを有し、細長部におけるバイポーラトランジスタ素子数が、幅広部が配置された配列の外縁に沿う方向に配列されたバイポーラトランジスタ素子数よりも少なくなるように配置する。

【効果】エミッタ配線の寄生抵抗によるエミッタ−ベース間電圧ばらつきを低減する。

(もっと読む)

ヘテロ接合バイポーラ・トランジスタ及びその製造方法

【課題】 ヘテロ接合バイポーラ・トランジスタ及びその製造方法を提供する。

【解決手段】 ヘテロ接合バイポーラ・トランジスタに関連する、半導体構造体及び半導体の製造方法が提供される。この方法は、同じ配線レベルにある金属導線によって接続される2つのデバイスを形成することを含む。2つのデバイスの第1のものの金属導線は、銅配線構造体上に金属キャップ層を選択的に形成することによって形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

半導体装置

【課題】GaAsチップの耐湿性を向上させることができる半導体装置を得る。

【解決手段】GaAsチップ14は樹脂26で封止されている。GaAsチップ14は、p型GaAsベース層34(p型GaAs層)と、その上に形成されたn型GaAsエミッタ層36(n型GaAs層)を有する。GaAsチップ14の外周部においてn型GaAsエミッタ層36上に金属電極18が形成されている。この金属電極18には正電圧が印加される。GaAsチップ14の中央部に形成された素子領域20と金属電極18との間において、p型GaAsベース層34とn型GaAsエミッタ層36に半絶縁性領域38が形成されている。半絶縁性領域38よりも外側において、p型GaAsベース層34と金属電極18は接続部40により電気的に接続されている。

(もっと読む)

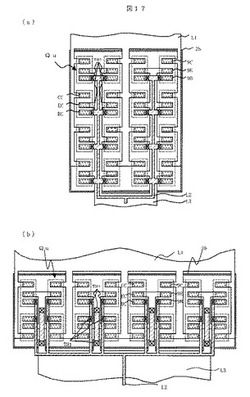

電力増幅器

【課題】集積回路チップと実装基板との接続の容易性や、放熱性の良好さを維持したままで、各単位セル動作の均一性を確保し、出力段トランジスタの総合的な動作特性を改善する。

【解決手段】

コレクタ電極配線101は、平行する2つの単位セル列用コレクタ電極配線1,2が、その一方の端部で、出力用配線3によって接続されてなり、この出力端とされる一方、単位セル列用コレクタ電極配線1,2の他方の端部は、セル列間接続配線4により相互に接続されたものとなっており、これによって、各単位セルの動作の均一性の改善がなされるものとなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】 高温時のウェーハ反りを抑制し、チッピングや欠けを回避した自己発熱を半導体基板裏面から放熱できる放熱特性改善がされた薄型半導体装置及び製造が容易なその製造方法を提供する。

【解決手段】 複数の素子領域及び当該素子領域を区画する素子分離領域14を有する半導体基板9と、素子領域に形成された半導体素子とを有する。素子分離領域は、DTI(Deep Trench Isolation) 構造であり、その底面は半導体基板9裏面に露出し、その内部は空洞になっている。この半導体基板は半導体素子を形成後に半導体基板裏面を素子分離領域14の底面が露出するまで研磨もしくはエッチングして半導体基板9を薄くすると共に素子分離領域14内部を空洞にする。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの電極形成時に、MOSトランジスタを覆う層間絶縁膜上のポリシリコン膜のエッチング残りの発生を低減可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)バイポーラトランジスタ5とMOSトランジスタ6a、6bとが形成された半導体基板51を覆うように層間絶縁膜65を形成する工程と、(b)層間絶縁膜65を平坦化する工程と、(c)層間絶縁膜66におけるバイポーラトランジスタ5の電極70用の開口部68を形成する工程と、(d)層間絶縁膜66及び開口部68を覆うようにポリシリコン膜69を形成する工程と、(e)層間絶縁膜66上のポリシリコン膜69をエッチバックして、開口部68内に電極70を形成する工程とを具備する。

(もっと読む)

絶縁膜層分離IC製造

【課題】二酸化ケイ素や窒化ケイ素など非常に薄い低応力誘電体材料と半導体層とで

形成された可とう性の膜で集積回路(24、26、28、...30)を製造する汎用手

法を提供する。

【解決手段】膜(36)の半導体層中に半導体デバイス(24、26、28...3

0)を形成する。最初に、標準厚さの基板(18)から半導体膜層(36)を形成し、次

いで、基板の薄い表面層をエッチングまたは研磨する。他のバージョンでは、ボンディン

グされた従来の集積回路ダイ用の支持および電気的相互接続として可とう性膜を使用し、

膜中の複数の層に相互接続部を形成する。1つのそのような膜に複数のダイを接続するこ

とができ、膜は次いでマルチチップ・モジュールとしてパッケージされる。

(もっと読む)

半導体装置

【課題】エミッタ電極に対するコンタクト部を容易に形成しながら、エミッタ層の幅を小さくすることが可能な半導体装置を提供する。

【解決手段】このバイポーラトランジスタ(半導体装置)100は、シリコン層7と、シリコン層7の表面に形成された不純物領域8と、不純物領域8上に形成されたポリシリコン層からなるエミッタ電極10aと、不純物領域8とエミッタ電極10aとの間に形成され、エミッタ電極10aの幅W3よりも小さい幅W2を有するSiGe層9とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】従来の方法では、アノードの拡散層とカソードの拡散層との間に蓄積されたマイノリティキャリアの再結合速度を高めることができない。

【解決手段】半導体基板10上には、層間絶縁膜20が形成されている。層間絶縁膜20には、開口22(第1の開口)、開口24(第2の開口)および開口26が形成されている。開口22および開口26は、それぞれP型拡散層16およびN型拡散層18の上部に形成されている。開口24は、P型拡散層16とN型拡散層18との間の領域である間隔領域の上部に形成されている。これらの開口22、開口24および開口26中には、それぞれ、コンタクトプラグ32、コンタクトプラグ34およびコンタクトプラグ36が埋め込まれている。半導体基板10のうち開口22の下部に位置する領域および開口24の下部に位置する領域の双方に、IV価の不純物が注入されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】トレンチ構造のトランジスタの形状及び電極構造に関して自由に設計を行なうことができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】シリコン基板10の表面には複数の凹部10a,10a,…が設けられ、各凹部10aには、表面からエミッタ領域REとベース領域RBとがこの順序で配置されている。その他の領域がコレクタ領域RCとなってトランジスタを構成する。基板全面に電極としての導電体を設ける場合、凹部10aによる段差のため、ベース領域RB上のベース電極12Bとエミッタ領域RE上のエミッタ電極12Eとは分離された状態で形成される。そして、エミッタ電極12E及びベース電極12Bを被覆する層間絶縁膜13を形成し、層間絶縁膜13を介してエミッタ電極12E及びベース電極12Bとそれぞれコンタクトを取るためのボンディングパッド14E及び14Bをデバイスの上層に形成する。

(もっと読む)

半導体デバイスおよびこのようなデバイスの製造方法

本発明は、基板(11)および半導体本体(1)を有する半導体デバイス(10)であって、この半導体本体(1)は、順にコレクタ領域(2)、ベース領域(3)、およびエミッタ領域(4)を有するバイポーラトランジスタを備える該半導体デバイス(10)に関し、半導体本体は、コレクタ領域(2)およびベース領域(3)の少なくとも一部分を有する、突出するメサ(5)を備え、このメサを絶縁分離領域(6)によって包囲する。本発明によれば、半導体デバイス(10)は、さらに、ソース領域、ドレイン領域、介在させたチャネル領域、積層させたゲート誘電体(7)、およびゲート領域(8)を有する電界効果型トランジスタを備え、ゲート領域(8)は電界効果型トランジスタの最も高い部分を形成し、メサ(5)の高さはゲート領域(8)の高さより大きくする。このデバイスは本発明による方法によって安価かつ容易に製造することができ、このバイポーラトランジスタは優れた高周波数特性を有することができる。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】庇部を有する電極の庇部下の空洞を絶縁膜で埋め込むことで、層間絶縁膜や配線の段切れ、配線の短絡等を防止することを可能とする。

【解決手段】基板10に形成された導電層(エミッタキャップ層15)に接続されるもので庇部20a有するコンタクト電極(エミッタ電極)20と、エミッタ電極20の庇部20a下の空洞28部分に埋め込まれた絶縁膜31と、エミッタ電極20および絶縁膜31側部を被覆する層間絶縁膜21と、層間絶縁膜21に形成された接続孔24を通じてエミッタ電極20に接続されるとともに、層間絶縁膜21上をエミッタ電極20上より電極周辺部に配設されている配線27とを備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタにおける高利得化および低雑音化を同時に実現できる技術を提供する。

【解決手段】ベースパッド31およびコレクタパッド32の下部にエミッタ(基準(接地)電位)と電気的に接続された配線24が設けられた基板シールド構造とすることにより、ベースパッド31およびコレクタパッド32と配線24との間では容量が設けられた構造として電力消費をなくし、基板1からの熱雑音は、配線24を介して基準(接地)電位へと逃がし、ベースパッド31およびコレクタパッド32へは届かないようにする。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法およびヘテロ接合バイポーラトランジスタ

【課題】特にGaAsSb系ベース層を有するHBTにおいて、HBT素子の特性を劣化させることなく、素子表面を部分的に不活性化するHBTを提供する。

【解決手段】所定の材質の基板1上に形成したコレクタ層3、ベース層4、エミッタ層5を含む層構造の少なくとも側壁をAl酸化膜8で覆っている構造とする。基板1としてInPを、ベース層4に、少なくとも一層はAl(x)Ga(1−x)As(y)Sb(1−y)を用いる(x,y:組成比、0.0≦x≦0.2,0.2≦y≦0.8)。すなわち、基板1上に、エミッタ層5、ベース層4、コレクタ層3を含むHBTの層構造を結晶成長により作製した後、エッチングによりメサ状に加工し、さらに、表面に堆積させた前記Al化合物を酸化させることによりAl酸化膜8を形成し、電極形成領域に堆積させたAl酸化膜8をエッチングにより除去して電極9を形成する。

(もっと読む)

縦型バイポーラトランジスタおよびその製造方法

【課題】高い直流電流増幅率、特に小電流領域で高い直流電流増幅率を得ることができる縦型バイポーラトランジスタを提供する。

【解決手段】n型半導体基板1の下層に高濃度n型半導体層2を形成し、上層にp型半導体層3を形成し、p型半導体層3に表面から層内へ延在する高濃度n型半導体層4を形成し、p型半導体層3および高濃度n型半導体層4に二酸化珪素膜5を形成してなり、所定の水分を添加した酸素、または所定の水分を添加した酸素を含むガスからなる雰囲気下で熱処理することにより、二酸化珪素膜5の表面電荷密度を低くして、高い直流電流増幅率、特に小電流領域に於いて高い直流電流増幅率を得る。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップ面積の増大を抑制しつつ、アナログ回路とデジタル回路とを同一基板上に混載する。

【解決手段】半導体基板11上にアナログ回路を形成した後、凹部32が形成された絶縁膜31をアナログ回路上に形成し、凹部32内が埋め込まれるようにして非晶質半導体層33を絶縁膜31上に形成し、非晶質半導体層33にレーザを照射することにより、非晶質半導体層33の溶融結晶化を行い、凹部32の周囲に略単結晶半導体粒34を形成し、略単結晶半導体粒34にデジタル回路を形成する。

(もっと読む)

電子装置およびその製造方法

【課題】 電力増幅モジュールやそれに用いる集積受動部品または半導体チップの低コスト化および高性能化を図る。

【解決手段】 集積受動部品5において、シード膜51、銅膜53およびニッケル膜54の積層膜からなる配線55により、RFパワーモジュールのローパスフィルタ回路を構成するインダクタ素子が形成される。ニッケル膜54は、銅膜53の全面上に形成され、表面保護膜としての絶縁膜61の開口部62から露出するニッケル膜54上に、金膜63およびバンプ電極64が形成されている。ニッケル膜54は、無電解Ni−Pめっき膜であり、リンを10重量%以上含有し、非磁性状態とされている。

(もっと読む)

半導体装置

【課題】 半導体装置において、反転領域対策を、既存の製造工程の条件を変えないで実現することを課題とする。

【解決手段】 N型エピタキシャル層4上にP型拡散層よりなる抵抗素子5が形成してあり、N型エピタキシャル層4上にシリコン酸化膜40が形成してあり、抵抗素子5の端から出ているアルミニウム配線8,9がシリコン酸化膜40上を延在している。シリコン酸化膜40は、N型エピタキシャル層4内に食い込んで厚みが増してある厚み付加部分42を枠状に有する。厚み付加部分42は、シリコン酸化膜40の反転電圧を上げる。厚み付加部分42は酸素イオンの注入及びアニール処理によって形成される。

(もっと読む)

バイポーラトランジスタの製造方法

第一のトレンチ(11)内でバイポーラトランジスタを製造する方法で、一つのフォトリソグラフィマスクのみを適用して第一のトレンチ(11)及び第二のトレンチ(12)を形成する。コレクタ領域(21)を第一のトレンチ(11)及び第二のトレンチ(12)内に自己整合して形成する。ベース領域(31)を第一のトレンチ(11)内にあるコレクタ領域(21)の一部分に自己整合して形成する。エミッタ領域(41)をベース領域(31)の一部分に自己整合して形成する。コレクタ領域(21)に対する接点を第二のトレンチ(12)内に形成し、ベース領域(31)に対する接点を第一のトレンチ(11)内に形成する。バイポーラトランジスタの製造を標準CMOSプロセスに組み入れることができる。  (もっと読む)

(もっと読む)

1 - 20 / 26

[ Back to top ]