Fターム[5F003BP01]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | 拡散 (273)

Fターム[5F003BP01]の下位に属するFターム

同一開口部を用いる二重拡散 (16)

複数の物質による同時拡散 (4)

複数の領域を同時に形成する拡散 (26)

拡散源 (104)

ドーピング物質 (42)

外方拡散、アウトディフュージョン (11)

不均一なマスク能力を利用するもの (3)

Fターム[5F003BP01]に分類される特許

1 - 20 / 67

半導体装置

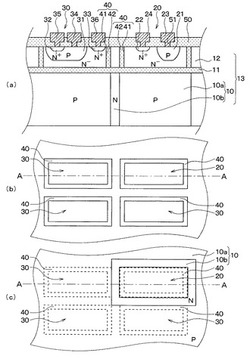

【課題】支持基板に接地電極を備えることなく、第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供する。

【解決手段】支持基板10を、第1導電型領域10aと第2導電型領域10bとを有し、第1素子形成領域20にノイズが印加されてノイズが伝播されたときの当該ノイズの伝播経路中に、第1、第2導電型領域10a、10bで構成されるPNP接合またはNPN接合を有するものとする。このような半導体装置では、PNP接合またはNPN接合の間に構成される空乏層により、第1、第2素子形成領域20、30の間でノイズが伝播することを抑制することができる。

(もっと読む)

電流増幅素子

【課題】なだれ増倍を利用して電流を直接増幅することが可能であると共に、リニアモード動作において、高感度と応答速度の速さとを両立させることができる電流増幅素子を提供する。

【解決手段】電流増幅素子は、半導体基板の表面に平面視が円形となるように中心軸の周りに対称に形成されたn型半導体ウエル(n−ウエル)104、n−ウエル内に同心円状に形成されたp型半導体領域112、p型半導体領域内に同心円状に形成されたn型半導体領域112、及び順バイアス電圧と逆バイアス電圧とを印加するための複数の電極を備えている。n−ウエルの内側の面は、中心軸から予め定めた距離の範囲内では基板裏面に向って半径が小さくなると共に、範囲より外側では基板裏面に向って半径が大きくなるように形成されている。

(もっと読む)

ヘテロ接合バイポーラトランジスタ、及び、ヘテロ接合バイポーラトランジスタの製造方法

【課題】良好なIn組成比及び結晶性を有するヘテロ接合バイポーラトランジスタ、及び、ヘテロ接合バイポーラトランジスタの製造方法を提供する。

【解決手段】六方晶系窒化ガリウム系半導体からなりn型窒化ガリウム系半導体層5bを有するコレクタ層5と、Inを含むp型窒化ガリウム系半導体層からなり、コレクタ層5の主面S4に設けられたベース層7と、他のn型窒化ガリウム系半導体層からなり、ベース層7の主面S5に設けられたエミッタ層9と、を備えるヘテロ接合バイポーラトランジスタ1であって、コレクタ層5の主面S4は、コレクタ層5の六方晶系窒化ガリウム系半導体のc軸に対して60度以上80度以下の角度で傾斜している。

(もっと読む)

半導体基板の製造方法

【課題】イオン注入後のアニール後に生じる残留欠陥を除去することができ、その後シリコンエピタキシャル層を形成しても積層欠陥を生じない、高品質な半導体基板の製造方法を提供する。

【解決手段】半導体基板の製造方法であって、少なくとも、シリコン単結晶基板に選択的にイオン注入を行う工程と、該イオン注入後に、前記シリコン単結晶基板の結晶性を回復させる回復熱処理と前記注入イオンを拡散させる拡散熱処理を行う熱処理工程と、該熱処理後に、前記イオン注入工程によって前記シリコン単結晶基板の表面層に形成されたアモルファス層の全部を取り込む厚さの熱酸化膜を形成する熱酸化膜形成工程と、該形成された熱酸化膜を除去する工程と、該熱酸化膜を除去した表面上にエピタキシャル層を形成する工程と、を有することを特徴とする半導体基板の製造方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バイポーラトランジスタが動作する際に、ベース領域のうちコレクタ側の端部が破壊されることを抑制する。

【解決手段】ベース領域150は、ウェル110内に形成されている。エミッタ領域170はベース領域150の中に形成され、ベース領域150より浅い。コレクタ領域140はウェル110内に形成され、ベース領域150の外側に位置している。第1埋込領域180は、少なくとも一部がベース領域150の中に位置しており、ベース領域150よりも不純物濃度が高い。そして第1埋込領域180は、平面視において、エミッタ領域170とコレクタ領域140の間に少なくとも一部が位置している。また第1埋込領域180は、エミッタ領域170の縁のうち少なくとも一辺と重なっており、かつエミッタ領域170の全面には重なっていない。

(もっと読む)

バイポーラトランジスタ

【課題】表面酸化膜下の界面近傍で発生する降伏を防ぎ、ツェナー降伏によるブレークダウン電圧の経時変動を防ぐバイポーラトランジスタを提供することを目的としている。

【解決手段】第一導電型半導体基体3内に不純物濃度が第一導電型半導体基体3より高い第一導電型の電流経路領域4と、電流経路領域4内に第二導電型の表面降伏防止領域5と、第一導電型半導体基体3表面に電流経路領域4と表面降伏防止領域5に接し不純物濃度が表面降伏防止領域5より高い第二導電型のベース領域6と、第一導電型半導体基体3表面に電流経路領域4と表面降伏防止領域5に接する第一導電型コレクタ領域7と、第一導電型半導体基体3表面かつ表面降伏防止領域5内に不純物濃度が電流経路領域4より高い第一導電型のエミッタ領域8と、表面降伏防止領域5内かつエミッタ領域8に接する不純物濃度が表面降伏防止領域5より高い第一導電型内部降伏誘導領域9を備える。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、寄生Trのオン電流が半導体層表面を流れることで、素子が熱破壊するという問題があった。

【解決手段】本発明の半導体装置では、分離領域2とN型の埋込層7、9を利用し、保護素子1が形成される。保護素子1内のPN接合領域11は分離領域2のP型の埋込層2A側に形成され、PN接合領域11の接合耐圧は保護される素子内のPN接合領域の接合耐圧よりも低い。この構造により、寄生Tr1のオン電流I1は保護素子1へと流れ込み、素子は保護される。また、寄生Tr1のオン電流I1が、エピタキシャル層4の深部側を流れることで、保護素子1の熱破壊が防止される。

(もっと読む)

バイポーラ型半導体装置およびその製造方法

【課題】高速化されたバイポーラ型半導体装置およびその製造方法を提供する。

【解決手段】

コレクタ領域10と、コレクタ領域10上に配置されたベース領域12と、ベース領域12上に配置されたエミッタ領域14と、ベース領域12上に配置され、エミッタ領域14と共通に形成されたエミッタパッド領域34と、ベース領域12上に配置され、複数のベースコンタクトCBを介してベース領域12と接続されたベース電極20と、エミッタ領域14上に配置されたエミッタ電極18と、ベース領域12近傍のエミッタパッド領域34上に配置されたエミッタパッド電極24とを備えるバイポーラ型半導体装置およびその製造方法であり、さらにエミッタパッド領域34上に配置された絶縁層26を備えていても良く、その際、エミッタパッド電極24は、絶縁層26上に配置される。

(もっと読む)

半導体装置、光ディスク装置

【課題】電流利得のばらつきを低減することができる半導体装置を提供する。

【解決手段】第1導電型の半導体基体1と、この半導体基体1の表面の一部に形成された、バイポーラトランジスタの第2導電型のコレクタ層2と、このコレクタ層2の一部に形成された、バイポーラトランジスタの第1導電型のベース層6と、このベース層6の一部に形成された、バイポーラトランジスタの第2導電型のエミッタ層7と、このエミッタ層7の直下の領域を除いた部分の半導体基体1に形成された、第1導電型の半導体層9とを含む半導体装置を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、半導体装置及びその製造方法等に関し、バイポーラトランジスタの面積を縮小してトランジスタの高集積化が可能な半導体装置及びその製造方法等提供する。

【解決手段】本発明に係る半導体装置及びその製造方法は、第1導電型半導体にベース領域6を形成後、第1のシリコン窒化膜8及びシリコン酸化膜9を形成する。シリコン酸化膜に溝を形成し、第2のシリコン窒化膜10を形成する。第1及び第2のシリコン窒化膜をエッチバックすることでカバー膜10aを形成する。溝の底面上及びカバー膜の内側にポリシリコンエミッタを形成し、第3のシリコン窒化膜13を形成する。第3のシリコン窒化膜及びカバー膜をマスクとして自己整合的にシリコン酸化膜をエッチングすることで、カバー膜の周囲に位置し且つ前記ベース領域上に位置する開口部を形成し、ベース領域を露出させ、導電膜17aを形成する工程とを具備することを特徴とする。

(もっと読む)

半導体ウエハのエッチング方法及びそのエッチング装置

【課題】半導体装置の製造方法に関し、特に半導体ウエハの枚葉処理における湿式エッチング装置のクリーンルーム占有床面積の拡大を防止し、生産性の向上を図ること、並びにそれに伴う歩留改善、間接材料の使用量低減可能な作業方法の確立を図る。

【解決手段】本発明の半導体ウエハ1のエッチング方法は、半導体ウエハ1を床面に対して垂直に保持した状態でエッチングするもので、吸着チャック10に垂直に保持された半導体ウエハ1と垂直状態で相対するエッチング機構13の正面部17並びに凸部18の間に、上から下に流れる落ちるエッチング液による薬液層19を形成しつつ、半導体ウエハ1を低速回転させながらエッチングする。

(もっと読む)

縦型バイポーラトランジスタ及びその製造方法

【課題】 サリサイドオフセット領域の形成により、ベース側の空乏層が十分に広がり、リーク電流や接合耐圧低下の問題を防ぐサリサイド処理を行った縦型バイポーラトランジスタを提供する。

【解決手段】 縦型バイポーラトランジスタは、半導体基板1に形成された第一導電型(N型)のコレクタ領域2と、コレクタ領域2内に形成された第二導電型(P型)のベース領域5と、ベース領域5内に形成された第一導電型のエミッタ領域6と、ベース領域5を囲むようにコレクタ領域2の表面部に形成されたフィールド酸化膜4と、ベース領域5上に形成されたサリサイド層14とを具備する。ベース領域5の表面は、サリサイド層14が形成されたサリサイド領域と、フィールド酸化膜4の端部とサリサイド領域の端部との間にサリサイド層が形成されていないサリサイドオフセット領域15とが設けられている。

(もっと読む)

半導体装置

【課題】 2層の電極構造を有するディスクリート型バイポーラトランジスタでは、2層目のベース電極下方に1層目のエミッタ電極が配置され、2層目のエミッタ電極下方に1層目のベース電極が配置される。このため電極の引き回しによる水平方向の配線抵抗がチップ内で不均一となり、電流容量が大きくできない問題があった。

【解決手段】 ベース領域を第1コンタクトホールを介して1層目の第1ベース電極と接続させ、第1ベース電極を第1スルーホールまたは第2スルーホールを介して2層目の第2ベース電極16と接続させる。エミッタ領域を第2コンタクトホールを介して1層目の第1エミッタ電極と接続させ、第1エミッタ電極を、第2ベース電極の第2開口部、第3スルーホールを介して、3層目の第2エミッタ電極と接続させる構成とする。これにより各セルの配線抵抗のばらつきを略均一軽減できる。

(もっと読む)

半導体装置

【課題】 2層の電極構造を有するディスクリート型バイポーラトランジスタでは、2層目のベース電極下方に1層目のエミッタ電極が配置され、2層目のエミッタ電極下方に1層目のベース電極が配置される。このため電極の引き回しによる水平方向の配線抵抗がチップ内で不均一となり、電流容量が大きくできない問題があった。

【解決手段】 1層目の第1エミッタ電極を島状に設け、第1ベース電極をこれらの周りを囲む平板状とする。2層目の第2エミッタ電極は、全ての第1エミッタ電極を覆う平板状に設け、第2ベース電極は第2エミッタ電極の周囲に枠状に設ける。第1エミッタ電極はその直下に設けた第2コンタクトホールを介してエミッタ領域とコンタクトし、直上に設けた第2スルーホールを介して第2エミッタ電極とコンタクトする。これにより電極の引き回しによる水平方向の配線抵抗を均一にできる。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、製造条件のばらつきにより、保護素子よりも先に被保護素子がオン動作し、過電圧から被保護素子が保護し難いという問題があった。

【解決手段】本発明の半導体装置では、保護素子1とNPNトランジスタ11との構成の一部を共用する。そして、保護素子1では、N型の拡散層10とP型の拡散層6との離間距離W1が、N型の拡散層9とP型の拡散層6との離間距離W2よりも短くなる。この構造により、出力端子に過電圧が印加された際に、NPNトランジスタ11よりも保護素子1の方が先にオン動作し、過電圧からNPNトランジスタ11が保護される。

(もっと読む)

ポリエミッタ型バイポーラトランジスタ、BCD素子、ポリエミッタ型バイポーラトランジスタの製造方法及びBCD素子の製造方法

【課題】複合高電圧素子工程を用いたポリエミッタ型バイポーラトランジスタ及びその製造方法、BCD(複合高圧)素子及びその製造方法を提供する。

【解決手段】実施の形態に係るポリエミッタ型バイポーラトランジスタは、半導体基板100の上側の一部に形成された埋込層110と、上記半導体基板の上に形成されたエピ層120と、上記エピ層に形成され、上記埋込層と連結されるコレクタ領域130と、上記エピ層の上側の一部に形成されたベース領域140と、上記ベース領域の基板の表面に形成され、ポリシリコン材質からなるポリエミッタ領域170と、を含む。実施の形態に係るBCD素子は、ポリシリコン材質からなるポリエミッタ領域を含むポリエミッタ型バイポーラトランジスタを含み、上記バイポーラトランジスタと同一な単一ウエハ上に形成されたCMOSとDMOSのうちの1つ以上のMOSを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、エミッタ拡散層等を形成する際のマスクずれにより、デバイスサイズが縮小され難く、高耐圧化が達成され難いという問題があった。

【解決手段】本発明の半導体装置では、エミッタ領域としてのP型の拡散層18の周囲には、LOCOS酸化膜14、15、N型の拡散層22、23が形成される。N型の拡散層22、23の周囲には、コレクタ領域としてのP型の拡散層19、20が、N型の拡散層22、23と離間して形成される。この構造により、P型の拡散層18〜20、N型の拡散層22、23が位置精度良く形成され、ベース領域幅Wb1が狭められ、高耐圧の横型PNPトランジスタが形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】同一基板上に形成された縦型PNPトランジスタとNPNトランジスタの両方の特性向上が図られた半導体装置を提供する。

【解決手段】半導体装置はPNPトランジスタ50を備えている。PNPトランジスタ50は、第1のP型コレクタ領域3bと、第1のP型コレクタ領域3bの底面を覆い、第1のP型コレクタ領域3bの不純物濃度のピークよりも深い位置に不純物濃度のピークを有する第1のN型埋め込み領域2と、第1のP型コレクタ領域3b上に形成された第2のP型コレクタ領域5bとを備えている。第1のP型コレクタ領域3bの側面もN型領域に囲まれている。このため、PNPトランジスタ50におけるパンチスルーの発生が抑えられるとともに、コレクタ領域内のキャリア通過経路を短くしてコレクタ抵抗の低減を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】非選択エピタキシャル法により半導体層を形成しても、エミッタとベースとを確実に接続して高い信頼性を確保することができる半導体装置及びその製造方法を提供する。

【解決手段】非選択エピタキシャル成長法により、ベース開口部8の内壁を覆うようにシリコン酸化膜7の全面にSiGe膜9を成長させる。このときの成膜条件としては、ベース開口部8内において、底部9aが単結晶からなり、側壁部9b等のその他の部位が多結晶となると共に、側壁部9bの膜厚が底部9aの膜厚の1.5倍以下になる成膜条件を選択する。このような非選択エピタキシャル成長では、原料ガスとして、モノシラン、水素、ジボラン及びゲルマンを用いる。このとき、モノシラン及び水素の各流量は、夫々20sccm、20slmとする。また、成長温度を650℃、ジボランの流量を75sccmに設定し、ゲルマンの流量を35sccmに設定する。

(もっと読む)

半導体双方向スイッチング装置

【課題】本発明は、スーパージャンクション構造を有し双方向スイッチングが可能な半導体双方向スイッチング装置を提供する。

【解決手段】二つの主電極の両方に電子とホールの制御部を設け、スーパージャンクションを構成するn形半導体層とp形半導体層における電流を制御する。

(もっと読む)

1 - 20 / 67

[ Back to top ]