Fターム[5F003BP21]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | イオン注入 (274)

Fターム[5F003BP21]の下位に属するFターム

斜方向 (19)

ドーピング物質 (42)

同一開口部を用いる二重イオン注入 (30)

不均一なマスク能力を利用するもの (12)

Fターム[5F003BP21]に分類される特許

1 - 20 / 171

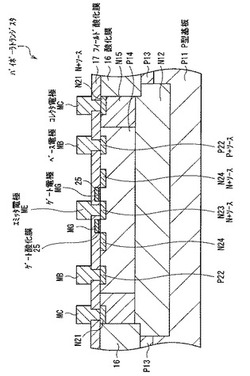

半導体デバイス

【課題】高い電流増幅率と高いアーリー電圧を両立することができ、CMOSトランジスタとともに製造する場合でもより少ない製造工程により製造することができる半導体デバイスを提供する。

【解決手段】基板P11の表面に形成された第1導電型のベースP14と、ベースの表面に形成された第2導電型のエミッタN23と、ベースの表面においてエミッタと離間して配置され、エミッタから第1の種類のキャリアを受け取るとともに、その第1の種類のキャリアをベースへ注入する、第2導電型のドープ領域N24と、ベースを挟んで、エミッタおよびドープ領域の反対側に形成された、第2導電型のコレクタN15とを備える。

(もっと読む)

半導体素子の製造方法、ESD保護素子の製造方法

【課題】半導体ウエハに厚みばらつきがある前提で、コストアップをすることなく高品質の半導体素子を提供すること。

【解決手段】第1導電型の活性層の下に第1導電型の埋込拡散層を有する半導体基板を準備するステップと、活性層と埋込拡散層の総厚を測定し、測定した総厚から前記活性層の厚さを求めるステップと、活性層に、埋込拡散層との間で電流が流れる第1導電型のコレクタ領域をイオン注入によって形成するステップと、活性層に、埋込拡散層との間で電流が流れる第2導電型のベース領域をイオン注入によって形成するステップと、ベース領域内に、ベース領域との間で電流が流れる第1導電型のエミッタ領域をイオン注入によって形成するステップとを備え、ベース領域を形成するステップは、活性層の厚さに応じてイオン加速エネルギーを変化させるステップであることを特徴とする。

(もっと読む)

エピレス基板における分離型の相補型MOS装置

【課題】高い実装密度を得ることが可能な半導体装置の製造プロセスを提供する。

【解決手段】半導体装置を電気的に分離するための構造は、エピタキシャル層を含まない半導体基板240内にドーパントを打込むことにより形成される。この打込みに続き、極めて限られた熱収支に上記構造を晒すことでドーパントが顕著に拡散しないようにする。その結果として、上記分離構造の寸法が制限かつ規定され、こうして、エピタキシャル層を成長させる工程とドーパントを拡散させる工程とを含む従来のプロセスを用いて得られるよりも高い実装密度を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】良好な電気特性を有する半導体装置の製造方法を提供する。

【解決手段】電極層の上に希土類金属シリサイド膜とアモルファスシリコン膜とを形成し、希土類金属シリサイド膜とアモルファスシリコン膜とをマイクロ波を用いて加熱することにより、希土類金属シリサイド膜の結晶構造に応じた結晶配向を持つように、アモルファスシリコン膜を結晶化させる。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

電流増幅素子

【課題】なだれ増倍を利用して電流を直接増幅することが可能であると共に、リニアモード動作において、高感度と応答速度の速さとを両立させることができる電流増幅素子を提供する。

【解決手段】電流増幅素子は、半導体基板の表面に平面視が円形となるように中心軸の周りに対称に形成されたn型半導体ウエル(n−ウエル)104、n−ウエル内に同心円状に形成されたp型半導体領域112、p型半導体領域内に同心円状に形成されたn型半導体領域112、及び順バイアス電圧と逆バイアス電圧とを印加するための複数の電極を備えている。n−ウエルの内側の面は、中心軸から予め定めた距離の範囲内では基板裏面に向って半径が小さくなると共に、範囲より外側では基板裏面に向って半径が大きくなるように形成されている。

(もっと読む)

バイポーラ半導体素子

【課題】高温や電流密度が高い条件下でも基板へ少数キャリアが到達するのを防いで、順方向電圧の増大を防ぐことができるバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20では、n型SiC基板21とn型バッファ層22との間に形成したn型少数キャリア消滅層31は、n型バッファ層22よりも炭素空孔欠陥の濃度が高く、少数キャリア消滅層31の炭素空孔欠陥はp型のアノード層24,25からの正孔のトラップとして働く。よって、小数キャリア消滅層31に達した正孔(少数キャリア)がトラップされ、小数キャリア消滅層31において正孔密度K2が急激に減衰する。これにより、正孔(少数キャリア)が基板21へ到達することを防いで、基板21から積層欠陥が拡大するのを防いで、順方向電圧の増大を防止できる。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波帯域で動作する半導体装置の特性の低下を抑制しつつ、製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、電界効果型トランジスタと、ヘテロ接合バイポーラトランジスタと、ヘテロ接合バイポーラトランジスタのGaAsベース層7を用いて形成されたベースエピ抵抗素子28と、電界効果型トランジスタのInGaAsチャネル層4を用いて形成された配線部26と、配線部26とベースエピ抵抗素子28とを絶縁する高抵抗化領域27と、配線部26の水平方向の周囲を囲う絶縁性の素子分離領域24とを含む。また、ベースエピ抵抗素子28は、半絶縁性GaAs基板1の主面に垂直な方向から見て、配線部26と交差しているベースエピ抵抗素子領域29を有する。

(もっと読む)

静電破壊保護回路

【課題】静電破壊保護回路の大きさを変えることなく、保持電圧を向上させることができ、保持電圧の制御を可能とする静電破壊保護回路を提供する。

【解決手段】ベース領域12の表面に、エミッタ領域6近傍からコレクタ端子側1へベース領域より不純物濃度が高いP型拡散領域20を備える構造とすることで、保持電圧を増加させることができ、P型拡散領域の長さにより保持電圧の値を設定することができる。

(もっと読む)

パワー半導体素子

【課題】小電流領域から大電流領域までの広範な負荷電流の電流値において、従来例に比較して、電力の変換効率を向上させることが可能なパワー半導体装置を提供する。

【解決手段】本発明のパワー半導体素子は、第1ゲート電極によりスイッチングの制御が行われるパワー半導体素子であり、IGBT動作とMOSトランジスタ動作との切替を行う第2ゲートを有し、第1ゲート電極により、スイッチング動作をさせる際、負荷に流れる負荷電流の電流値に応じて、第2ゲート電極に対して制御信号を印加し、MOSトランジスタにて動作させるか、またはバイポーラトランジスタとして動作させるかのいずれかを選択する。

(もっと読む)

半導体装置及びその製造方法

【課題】バイポーラトランジスタの高速化に伴うMOSトランジスタの分離特性の低下を抑制する半導体装置を提供する。

【解決手段】半導体装置1000aは、第一導電型のバイポーラトランジスタ100及びMOSトランジスタ200を備え、MOSトランジスタ200は、第二導電型の半導体基板1と半導体基板1上に形成された第一導電型のエピタキシャル層2との界面付近に形成された、半導体基板1上面から第一の深さに不純物濃度のピークを持つ第一導電型埋込層16と、第一導電型埋込層16上に形成された第二導電型埋込層17及びウェル層18と、第二導電型ウェル層18に形成された第一導電型のソース層19及びドレイン層20と、第一の深さより浅い第二の深さに不純物濃度のピークを持つ第一導電型埋込層27とを有し、第一導電型埋込層27は、第一導電型埋込層16と接し、かつ、第二導電型埋込層17の外縁部を囲むように形成されている。

(もっと読む)

バイポーラ型半導体装置およびその製造方法

【課題】高速化されたバイポーラ型半導体装置およびその製造方法を提供する。

【解決手段】

コレクタ領域10と、コレクタ領域10上に配置されたベース領域12と、ベース領域12上に配置されたエミッタ領域14と、ベース領域12上に配置され、エミッタ領域14と共通に形成されたエミッタパッド領域34と、ベース領域12上に配置され、複数のベースコンタクトCBを介してベース領域12と接続されたベース電極20と、エミッタ領域14上に配置されたエミッタ電極18と、ベース領域12近傍のエミッタパッド領域34上に配置されたエミッタパッド電極24とを備えるバイポーラ型半導体装置およびその製造方法であり、さらにエミッタパッド領域34上に配置された絶縁層26を備えていても良く、その際、エミッタパッド電極24は、絶縁層26上に配置される。

(もっと読む)

BiCDMOS構造及びその製造方法

【課題】DMOS電力回路、CMOSデジタル論理回路、及びコンプリメンタリバイポーラアナログ回路の全てを単一の集積化された回路チップ上に実現するBiCDMOS構造及びその製造方法を提供する。

【解決手段】基層10内に下向きに延出し、且つ基層の上に配置されたエピタキシャル層40内に上向きに延出し、かつエピタキシャル層の上側主面の下に配置された埋め込み絶縁領域21Bと、エピタキシャル層内のみに配置され、かつ埋め込み絶縁領域の上側主面から上向きに延出した埋め込みウェル領域44Bと、エピタキシャル層内に配置され、かつエピタキシャル層の上側主面からエピタキシャル層内に下向きに延出し、かつ埋め込みウェル領域の上側主面に接触する下側主面を備えたウェル領域51Bとを有し、バイポーラトランジスタがウェル領域内に形成され、MOSトランジスタがウェル領域外のエピタキシャル層の上側主面に形成される。

(もっと読む)

静電破壊保護回路

【課題】 静電破壊保護回路の動作開始電圧を下げるためトリガ素子を接続した場合であっても、静電破壊保護回路の静電破壊耐量を向上させることができる静電破壊保護回路を提供する。

【解決手段】 トリガ素子が接続される別のベース電極部拡散領域の周囲に、ベース領域より不純物濃度が低く、かつベース領域より深く形成されたP型拡散領域11を備える構造とすることで、別のベース電極部拡散領域近傍で生じる高電界を緩和し、またコレクタの一部を構成する埋め込み領域近傍で、ベース電流供給に必要な高電界を生じさせることができ、静電破壊耐量を向上させている。

(もっと読む)

縦型のバイポーラトランジスタとその製造方法

【課題】 ダイシングラインに沿って深部に至る深い不純物拡散領域を形成することによって必要な耐圧を確保する技術において、深い不純物拡散領域8を短時間の熱処理で製造可能な技術を提供する。

【解決手段】半導体基板4に不純物拡散領域を形成する際に、注入エネルギーを変えながら複数回に亘って不純物を注入する工程と、その後に半導体基板4を熱処理する工程を備えている。複数の深さL1〜L5に不純物を注入しておいてから熱処理をするので、深い不純物拡散領域8を短時間の熱処理で形成することができる。このバイポーラトランジスタ2の場合、複数の深さL1〜L5において不純物濃度のピークが観測される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の特性を向上できると共に、製造コストを低減できる。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1上に順次積層されたコレクタ層2A、ベース層3A及びエミッタ層4Aと、コレクタ層2Aの側面上に設けられ、コレクタ層に対して歪み応力を与える第1ストレスソース膜15Aと、ベース層3Aの側面上に設けられ、ベース層3Aに対して歪み応力を与える第2ストレスソース膜17と、を具備し、第1ストレスソース膜15A上端及び前記ベース層上端は、半導体基板表面から同じ高さに位置し、第2ストレスソース膜17は、ベース層3Aの側面と第1ストレスソース膜15Aの側面との間に設けられる。

(もっと読む)

半導体装置、光ディスク装置

【課題】電流利得のばらつきを低減することができる半導体装置を提供する。

【解決手段】第1導電型の半導体基体1と、この半導体基体1の表面の一部に形成された、バイポーラトランジスタの第2導電型のコレクタ層2と、このコレクタ層2の一部に形成された、バイポーラトランジスタの第1導電型のベース層6と、このベース層6の一部に形成された、バイポーラトランジスタの第2導電型のエミッタ層7と、このエミッタ層7の直下の領域を除いた部分の半導体基体1に形成された、第1導電型の半導体層9とを含む半導体装置を構成する。

(もっと読む)

トランジスタ型保護素子および半導体集積回路

【課題】保護素子のターンオン電圧を決める制約を少なくする。

【解決手段】半導体基板1、Pウェル2、ゲート電極4、ソース領域5、第1ドレイン領域6、第2ドレイン領域8および抵抗性接続領域9を有する。第1および第2ドレイン領域6,8は、ゲート電極4直下のウェル部分と所定の距離だけ離れたN型半導体領域からなる。第1および第2ドレイン領域6,8も互いに離れており、その間が抵抗性接続領域9によって接続されている。抵抗性接続領域9は薄膜抵抗層によって代替できる。

(もっと読む)

電流シフト領域を有する半導体デバイスおよび関連方法

半導体デバイスは、第1の伝導形を有する半導体バッファ層と、バッファ層の表面上にあって第1の伝導形を有する半導体メサとを含む。さらに第2の伝導形を有する電流シフト領域が半導体メサと半導体バッファ層との間の隅に隣接して設けられ、第1と第2の伝導形が互いに異なる伝導形である。関連する方法も開示される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、半導体装置及びその製造方法等に関し、バイポーラトランジスタの面積を縮小してトランジスタの高集積化が可能な半導体装置及びその製造方法等提供する。

【解決手段】本発明に係る半導体装置及びその製造方法は、第1導電型半導体にベース領域6を形成後、第1のシリコン窒化膜8及びシリコン酸化膜9を形成する。シリコン酸化膜に溝を形成し、第2のシリコン窒化膜10を形成する。第1及び第2のシリコン窒化膜をエッチバックすることでカバー膜10aを形成する。溝の底面上及びカバー膜の内側にポリシリコンエミッタを形成し、第3のシリコン窒化膜13を形成する。第3のシリコン窒化膜及びカバー膜をマスクとして自己整合的にシリコン酸化膜をエッチングすることで、カバー膜の周囲に位置し且つ前記ベース領域上に位置する開口部を形成し、ベース領域を露出させ、導電膜17aを形成する工程とを具備することを特徴とする。

(もっと読む)

1 - 20 / 171

[ Back to top ]