国際特許分類[H01L21/331]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | バイポーラ型の装置,例.ダイオード,トランジスタ,サイリスタ,の製造のための多段階工程 (1,363) | 装置が3つ以上の電極からなるもの (988) | トランジスタ (980)

国際特許分類[H01L21/331]に分類される特許

61 - 70 / 980

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

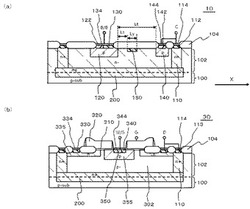

化合物半導体装置及びその製造方法

【課題】セルフアライメントにより容易に電極を形成することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】エッチングストッパ層2の上方に、Sbを含み、所定の溶液に対するエッチング耐性がエッチングストッパ層2よりも低いSb含有層3bを形成し、Sb含有化合物半導体層3b上に、Asを含み、前記所定の溶液に対するエッチング耐性がエッチングストッパ層2よりも低いAs含有層3cを形成する。そして、前記所定の溶液を用いて、導電膜4をエッチングマスクとし、Sb含有層3b及びAs含有層3cをメサ状にウェットエッチングし、平面視でSb含有層3b及びAs含有層3cから離間した位置において化合物半導体層1の上方に導電膜5aを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を増加させることなく、ESD保護素子としてのLDMOSトランジスタのスナップバック電圧をESD被保護素子としてのLDMOSトランジスタのスナップバック電圧より低くし、且つESD保護素子としてのLDMOSトランジスタの熱破壊電流値をスナップバック電圧の改善前より大きくする。

【解決手段】 ESD保護素子としてのLDMOSトランジスタ32は、N型エピタキシャル層3と、N+型埋め込み層2と、N型エピタキシャル層3の表面に形成されたドリフト層11と、エピタキシャル層3の表面に形成されたP型のボディ層10と、Pボディ層10の表面に形成されたN+型ソース層14と、エピタキシャル層3の表面上に形成されたゲート絶縁膜5、6と、ゲート絶縁膜5、6上に形成されたゲート電極8と、を具備し、N+型ソース層14の下方のボディ層10の底部にP型ボディ層窪み部10aが形成されている。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

エピレス基板における分離型の相補型MOS装置

【課題】高い実装密度を得ることが可能な半導体装置の製造プロセスを提供する。

【解決手段】半導体装置を電気的に分離するための構造は、エピタキシャル層を含まない半導体基板240内にドーパントを打込むことにより形成される。この打込みに続き、極めて限られた熱収支に上記構造を晒すことでドーパントが顕著に拡散しないようにする。その結果として、上記分離構造の寸法が制限かつ規定され、こうして、エピタキシャル層を成長させる工程とドーパントを拡散させる工程とを含む従来のプロセスを用いて得られるよりも高い実装密度を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】金属半導体化合物電極の界面抵抗を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態によればn型半導体上に硫黄を含有する硫黄含有膜を堆積し、硫黄含有膜上に第1の金属を含有する第1の金属膜を堆積し、熱処理によりn型半導体と第1の金属膜を反応させて金属半導体化合物膜を形成するとともに、n型半導体と金属半導体化合物膜との界面に硫黄を導入することを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】良好な電気特性を有する半導体装置の製造方法を提供する。

【解決手段】電極層の上に希土類金属シリサイド膜とアモルファスシリコン膜とを形成し、希土類金属シリサイド膜とアモルファスシリコン膜とをマイクロ波を用いて加熱することにより、希土類金属シリサイド膜の結晶構造に応じた結晶配向を持つように、アモルファスシリコン膜を結晶化させる。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体素子

【課題】 GaN基板上に結晶成長する各半導体層の平坦性向上した半導体基板を実現し、この半導体基板を基礎として、特性の高性能化された半導体素子を提供する。

【解決手段】n型基板11と、n型基板11上に積層された窒化物系III−V族化合物半導体単結晶からなるn型ドリフト層24と、n型ドリフト層24上に設けられた窒化物系III−V族化合物からなるp型ベース層25と、p型ベース層25上に設けられた窒化物系III−V族化合物からなるn型エミッタ層26と、n型基板11とn型ドリフト層24との間に設けられた、Siを5x1017cm-3以上2x1019cm-3以下含有する層とを備える。

(もっと読む)

バイポーラ接合トランジスタ

【課題】アナログアプリケーションの性能向上と共に、DCゲインおよび効率の増加を提供する。

【解決手段】バイポーラ接合トランジスタは、絶縁基板上の島状半導体と、島状半導体内に、第1伝導性型であるエミッタ、並びに第1伝導性型であるコレクタおよび/またはサブコレクタと、島状半導体内に、エミッタと、コレクタおよび/またはサブコレクタとを分離する、第2伝導性型であるベースと、島状半導体内に、第2伝導性型であるベース接触領域と、島状半導体内に、ベースに隣接するとともに、ベースをベース接触領域に接続する一方で、エミッタとは直接接触していない接続ベース領域と、を備え、接続ベース領域は、第2伝導性型であり、ベース接触領域のドーピング濃度未満のドーピング濃度を有する。

(もっと読む)

61 - 70 / 980

[ Back to top ]