国際特許分類[H01L21/331]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | バイポーラ型の装置,例.ダイオード,トランジスタ,サイリスタ,の製造のための多段階工程 (1,363) | 装置が3つ以上の電極からなるもの (988) | トランジスタ (980)

国際特許分類[H01L21/331]に分類される特許

41 - 50 / 980

ヘテロ接合バイポーラトランジスタ

【課題】GaAsSb系の化合物半導体のベース層を有するInP系HBTで、大きな電流利得が得られるようにする。

【解決手段】コレクタ層102の上に形成されてGa,As,およびSbから構成された化合物半導体からなるベース層103と、ベース層103の上に接して形成されたスペーサ層104と、スペーサ層104の上に接して形成されてInおよびPから構成された化合物半導体からなるエミッタ層105とを備える。スペーサ層104は、ベース層103の伝導帯端のエネルギー準位よりも低く、エミッタ層105の伝導帯端よりも高い伝導帯端のエネルギー準位を有し、ベース層103の価電子帯端のエネルギー準位よりも低く、エミッタ層105の価電子帯端よりも高い価電子帯端のエネルギー準位を有した状態で、ベース層103およびエミッタ層105に接して形成されている。

(もっと読む)

半導体装置及び電力増幅器

【課題】トランジスタの占有面積をほとんど増やすことなく、かつ、HBTとHFETとを接続する配線による悪影響を受けないBi−HFET(半導体装置)を提供する。

【解決手段】基板101上に形成されたHFET160と、HFET160上に形成されたHBT170とを備え、HFET160は、チャネル層102と、コンタクト層104とを有し、HBT170は、HFET160のコンタクト層104と接続、又は、一体化されたサブコレクタ層107と、コレクタ層108と、ベース層109と、エミッタ層110と、エミッタキャップ層111と、エミッタコンタクト層112とを有し、コレクタ層108、ベース層109及びエミッタ層110は、メサ形状の構造体であるベースメサ領域830を構成し、ゲート電極202は、第一のコレクタ電極203とベースメサ領域830との平面的な間に設けられたリセス領域820内に形成されている。

(もっと読む)

バイポーラ半導体素子

【課題】表面欠陥の発生を低減できて積層欠陥の発生を抑制でき、オン電圧ドリフトを抑制できるSiCバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20は、六方晶構造の炭化珪素半導体で作製され、メサ状の半導体層31が六角柱形状で6つの側面(メサ面)31Aをすべて{0m−m0}面(m,nは整数)とした。これにより、メサ面31Aに対する〈11−20〉方向のバーガーズベクトルBV1,BV2の角度θ1,θ2(図4)が、{11−20}面の素子表面(メサ面)に対するバーガーズベクトルBV101,BV102の角度θ101,θ102(図12)に比べて小さくなると共に表面欠陥が発生するのに必要なバーガーズベクトルBV1,BV2の長さが長くなる。これにより、メサ面31Aに表面欠陥SDが入り難くなり、メサ状の半導体層31の各メサ面31Aでの表面欠陥を低減できて、積層欠陥の発生を抑制できる。

(もっと読む)

半導体集積回路のESD保護回路およびそのESD保護素子

【課題】従来構造に比べて、レイアウト面積の増加を抑え、保護能力の大幅な低下を招くことなく、保持電圧Vhを電源電圧以上の適正な電圧に制御する。

【解決手段】ESD保護素子21は、スナップバック特性を有するスナップバック特性素子としてのSCR素子と、このSCR素子に接続されて、スナップバック開始電圧Vt1を素子電圧分だけ加算すると共に保持電圧Vhを該素子電圧の2倍高くするための電圧加算素子としてのダイオード13とを有して、ダイオード13の素子電圧を調整して、保持電圧Vhを電源電圧Vcc以上で被保護素子の耐電圧以下に調整する。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

トランジスタ用エピタキシャルウェハ

【課題】配管パージ等の作業を行うことなく、電気的特性等に影響を与える残留したTeやSeのエピタキシャル層中への混入を防止できるトランジスタ用エピタキシャルウェハを提供する。

【解決手段】基板100と化合物半導体層200とコンタクト層300とを有し、コンタクト層300は、n型不純物としてTe又はSeがドーピングされたIn組成比xが0.3≦x≦0.6で一定のn型InGaAs層からなり、n型InGaAs層は、n型不純物濃度が1.0×1019cm-3以上5.0×1019cm-3以下で、且つ、炭素濃度が1.0×1016cm-3以上3.0×1018cm-3以下であり、化合物半導体層200は、バッファ層400を備え、バッファ層400は、アンドープAlAs層からなる第1バッファ層401と、Al組成比yが0<y<1のアンドープAlGaAs層からなる第2バッファ層402とからなるものである。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】HEMTの移動度の低下を抑制することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】高電子移動度トランジスタ構造層3を、気相成長法により成長温度600℃以上750℃以下、V/III比150以下の条件で成長し、バイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下、V/III比75以下の条件で成長し、さらにノンアロイ層18を、380℃以上450℃以下の成長温度で成長する。

(もっと読む)

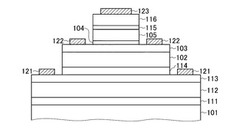

半導体装置

【課題】デバイスサイズの縮小、シリーズ抵抗の低減、及びリーク電流の抑制を可能とする半導体装置を提供することを目的とする。

【解決手段】本発明は、デバイス動作にとって、本来は不要な電位段差を発生させる層をデバイスの構造内にあえて挿入したものである。この電位段差は、バンドギャップの小さな半導体がメサ側面に露出しても、その部分の電位降下量を抑制し、デバイス動作に不都合なリーク電流を低減できる、という機能をもたらす。この効果は、ヘテロ構造バイポーラトランジスタ、フォトダイオード、及び電界吸収形光変調器などに共通して得られる。また、フォトダイオードにおいては、リーク電流が緩和されるのでデバイスのサイズを縮小することが可能となり、シリーズ抵抗の低減による動作速度の改善のみならず、デバイスを高密度にアレイ状に配置できるという利点も生まれる。

(もっと読む)

窒化物半導体素子の製造方法

【課題】ドレインリーク電流を低減することが可能な窒化物半導体素子の製造方法を提供する。

【解決手段】ヘテロ電界効果トランジスタ1の製造方法は、ドリフト層20aを支持基板10上にエピタキシャル成長させる工程と、水素ガスをキャリアガスとして用いて、p型半導体層である電流ブロック層20bをドリフト層20a上に1000℃以上でエピタキシャル成長させる工程と、窒素ガス、アルゴンガス、ヘリウムガス及びネオンガスからなる群より選ばれる少なくとも一種のガスをキャリアガスとして用いて、コンタクト層20cを電流ブロック層20b上にエピタキシャル成長させる工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】パターン形成不良が発生することを抑制する。

【解決手段】まず、N型コレクタとなる基板110上に、第1開口部(不図示)を有するシリコン酸化膜120を形成する。次いで、シリコン酸化膜120及び第1開口部に露出した基板110の表面上に第1絶縁膜を形成する。次いで、第1絶縁膜をエッチバックすることにより、シリコン酸化膜120の第1開口部における側壁のみに、第1絶縁膜を残存させて、側壁部を形成する。次いで、シリコン酸化膜120等の上に、ベース引出部144となるポリシリコン膜を形成する。次いで、ポリシリコン膜上に、第2開口部(不図示)を有する第2絶縁膜を形成する。次いで、第2絶縁膜をマスクとして、ポリシリコン膜のうち、第2開口部により露出している部分を酸化してシリコン酸化膜に変化させる。次いで、シリコン酸化膜に変化させた部分を選択的に除去する。次いで、側壁部と第2絶縁膜を選択的に除去する。

(もっと読む)

41 - 50 / 980

[ Back to top ]