国際特許分類[H01L21/331]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | バイポーラ型の装置,例.ダイオード,トランジスタ,サイリスタ,の製造のための多段階工程 (1,363) | 装置が3つ以上の電極からなるもの (988) | トランジスタ (980)

国際特許分類[H01L21/331]に分類される特許

81 - 90 / 980

半導体装置の製造方法

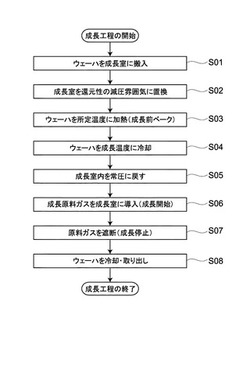

【課題】本発明の実施形態は、ベース層の幅を狭く形成しエミッタ層の不純物濃度を高くした低雑音特性を有する半導体装置の製造方法を提供することを目的とする。

【解決手段】一実施形態に係る半導体装置の製造方法は、第1導電型の第1半導体層の上に第2導電型の第2半導体層を成長する半導体装置の製造方法であって、前記第1半導体層の表面を常圧よりも低い圧力の還元性雰囲気に曝して熱処理する工程(S02〜S04)と、前記第1半導体層の表面上に、前記第2半導体層を常圧の雰囲気でエピタキシャル成長する工程(S05〜S07)と、を備えたことを特徴とする。

(もっと読む)

半導体素子及び該半導体素子を備える半導体素子構造

【課題】本発明は、かかる事情に鑑み、トランジスタの遮断状態を自然に実現し、半導体領域に金属領域との界面近傍の空乏層の形成を抑制しつつ、ショットキー障壁を実質的に下げることができるようにソース領域のフェルミ準位を選択することにより、駆動電流を増加させる半導体素子及び該半導体素子を備える半導体素子構造を提供することを課題とする。

【解決手段】ソース領域6及びドレイン領域7は、フェルミ準位が異なる第1金属領域10及び第2金属領域11を有し、第1金属領域10は、半導体領域5の価電子帯の頂上のエネルギーレベル以上で且つ半導体領域5の真性フェルミ準位以下のフェルミ準位を有する金属であり、第2金属領域11は、第1金属領域10のフェルミ準位以上で且つ伝導帯の底のエネルギーレベル以下のフェルミ準位を有する金属であることを特徴とする。

(もっと読む)

半導体装置

【課題】第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供することを目的とする。

【解決手段】第1、第2素子形成領域20、30に形成された半導体素子のうち、第1素子形成領域20に形成された半導体素子を外部機器と接続し、第1素子形成領域20と第2素子形成領域30との間に、第1導電型層60と、当該第1導電型層60に挟まれる第2導電型層61とを配置し、第1、第2導電型層60、61の間に、オフ時に半導体層12の表面から埋込絶縁膜11に達し、第1、第2素子形成領域20、30との間を仕切る空乏層63、64を構成する。

(もっと読む)

バイポーラトランジスタ

【課題】高速動作性・高電流駆動力を有するヘテロ接合バイポーラトランジスタ及びその製造方法を提供する。

【解決手段】バイポーラトランジスタは、コレクタとして機能するSi単結晶層3と、Si単結晶層3の上に形成された単結晶のSi/SiGeC層30a及び多結晶のSi/SiGeC層30bと、エミッタ開口部を有する酸化膜31と、エミッタ電極50と、エミッタ層35とを備えている。単結晶のSi/SiGeC層30aに真性ベース層52が形成され、単結晶のSi/SiGeC層30aの一部と多結晶のSi/SiGeC層30bとCoシリサイド層37bとにより、外部ベース層51が構成されている。エミッタ電極の厚みは、エミッタ電極50に注入されたボロンがエミッタ電極50内を拡散して、エミッタ−ベース接合部まで達しないように設定されている。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタをより高速に動作させることができるようにする。

【解決手段】リン酸および過酸化水素水を用いたウェットエッチングにより選択的にInGaAsをエッチングすることで、n−InGaAs層102をパターニングしてソースコンタクト層(第1半導体層)112を形成するとともに、チャネル層114の側部をエッチングして幅が狭くされたチャネル層114aを形成する。このウェットエッチングにより、所望のメサ幅(例えば15nm)としたチャネル層114aを形成する。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】室温(300K)以上において正孔濃度が1.0×1015cm‐3以上で、かつ、ドーパント原子濃度が1.0×1021cm‐3以下である実用的なp型ダイヤモンド半導体デバイスとその製造方法を提供すること。

【解決手段】単結晶ダイヤモンド基板1−1の上に形成された単結晶ダイヤモンド薄膜1−2の中には、二次元の正孔または電子チャンネル1−3が形成される。基板1−1の面方位と基板1−1の結晶軸「001」方向との成す角度をαs、ダイヤモンド薄膜1−2の面方位と単結晶ダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαd、チャンネル1−3の面方位とダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαcとする。単結晶ダイヤモンド薄膜1−2の表面上には、ソース電極1−4、ゲート電極1−5、ドレイン電極1−6が形成される。

(もっと読む)

半導体装置

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

半導体装置

【課題】 立ち上がり電圧低減と高耐圧実現の両立を可能とする構造を提案する。

【解決手段】 SiC縦型ダイオードにおいて、カソード電極21と、n++カソード層10と、n++カソード層上のn−ドリフト層11と、一対のp+領域12と、n−ドリフト層11とp+領域12の間に形成され、且つ一対のp+領域12に挟まれたn+チャネル領域16と、n++アノード領域14と、n++アノード領域14とp+領域12に形成されたアノード電極22を備える。

(もっと読む)

半導体集積回路装置

【課題】絶縁素子分離型のバイポーラトランジスタの放熱性を改善する。

【解決手段】薄い半導体層の第1のエリアに配置された第1のトランジスタと、薄い半導体層の第2のエリアに配置された第2のトランジスタで構成される回路部と、を備え、第1のトランジスタは、並列接続された複数のバイポーラトランジスタ素子を構成する複数の単位能動領域の配列全体を囲って配置された素子分離溝を含み、素子分離溝を能動領域から少なくとも1μm離間して設け、能動領域で生成される熱を単位能動領域を囲んで存在する半導体領域から外方に放熱させる構成を備えてなり、第2のトランジスタは、バイポーラトランジスタ動作を行う単位能動領域と、単位能動領域を取り囲んで形成され単位能動領域から1μm以下の位置に配置された素子分離溝を含む。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製造方法

【課題】ヘテロ接合バイポーラトランジスタのエミッタメサがより正確に形成できるようにする。

【解決手段】第1エミッタ電極107bの側部には、例えば酸化シリコンからなる庇部108が形成され、また、少なくともキャップ層106を含んで構成されたエミッタメサの露出している側面から庇部108の下部の領域のレッジ構造部105aにかけて形成された、例えば窒化シリコンからなる被覆層109が形成されている。被覆層109が、庇部108の側面,庇部108の下面,エミッタメサの側部,およびレッジ構造部105aの上にかけて形成されている。

(もっと読む)

81 - 90 / 980

[ Back to top ]