Fターム[5E346EE16]の内容

多層プリント配線板の製造 (97,916) | 多層形成の方法 (8,890) | 積層型のもの(主に加熱圧着による) (4,763) | 位置合わせに関するもの (179) | 位置合わせ用基準穴に関するもの (42)

Fターム[5E346EE16]に分類される特許

1 - 20 / 42

配線板の製造方法

【課題】より簡易な方法で、配線板におけるビア導体の位置精度を高める。

【解決手段】配線板の製造方法が、第1絶縁層を準備することと、第1絶縁層上に導体層を形成することと、導体層上に第2絶縁層を形成することと、第2絶縁層上に導体膜を形成することと、レーザ光を照射することによって、導体膜に第1開口部を形成することと、第1開口部を通じて、導体層に含まれる位置決めマークの位置を光学的に検出することと、位置決めマークを基準にして、導体層に含まれる導体パッドを露出させる第2開口部を第2絶縁層に形成することと、を含む。

(もっと読む)

プリント基板製造方法およびプリント基板

【課題】 プリント基板製造方法およびプリント基板に関し、ガラス繊維の糸の配列位置を考慮した信号配線を形成する。

【解決手段】 縦糸と横糸とを有し少なくとも一部領域における縦糸および横糸の少なくとも各一部の本数について縦糸と横糸との間で視覚的に互いに識別可能な糸を採用したガラス繊維に樹脂を含浸させた板状の基材やプリプレグを作成し、ガラス繊維の縦糸や横糸を識別して縦糸や横糸の配置位置を考慮して信号配線を形成する。

(もっと読む)

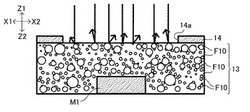

電子部品内蔵基板及びその製造方法

【課題】狭ピッチで形成された端子を有する電子部品の接続信頼性を十分に向上させることが可能な電子部品内蔵基板及びその製造方法を提供する。

【解決手段】電子部品50,51が内蔵された電子部品内蔵基板2の製造方法は、未硬化状態の第1樹脂層21上に、コア部材6を載置する工程と、電子部品50,51の端子52が未硬化状態の第1樹脂層21に接するように、該電子部品50,51を該未硬化状態の第1樹脂層21上に載置する工程と、未硬化状態の第1樹脂層21を硬化する工程と、硬化した第1樹脂層21、コア部材6、及び電子部品50,51上に、未硬化状態の第2樹脂層31を設ける工程と、未硬化状態の第2樹脂層31を硬化する工程と、を含むものである。

(もっと読む)

多層基板およびその製造方法

【課題】配線層同士の相対的な位置精度が向上された多層基板およびその製造方法を提供する。

【解決手段】多層基板10は、厚い金属コア層11と、金属コア層11の上面に絶縁層を介して積層された配線層(第1配線層16A、第3配線層16C)と、金属コア層11の下面に絶縁層を介して積層された配線層(第2配線層16B、第4配線層16D)と、金属コア層11等を貫通して形成された確認孔28とを主要に具備している。確認孔28は、上方および下方の両方から位置認識を行うことが可能であるので、同一の確認孔28を基準として各配線層を形成することにより、配線層同士の位置精度が向上される。

(もっと読む)

プリント配線板とその製造方法、および位置ズレ検出方法

【課題】プリント配線板の配線パターン形成直後に、バイアホールと配線パターン間の位置ズレを全数確認することが可能で、異常を早期発見して連続不良の場合には工程にフィードバックし、是正処置を取ることができるプリント配線板とその製造方法を提供する。

【解決手段】プリント配線板に備わるバイアホールと配線パターン間の位置ズレを検出する検査パターンを備え、前記検査パターンが、検出バイアホールおよび前記検出バイアホールに隣接する検出導体からなり、前記検出導体の形状を判定することによりプリント配線板のバイアホールと配線パターンとの位置ズレを検出することを特徴とするプリント配線板。

(もっと読む)

凹型コネクタ用基板及びその製造方法、測定用キット、センサ基板、並びにセンサ基板内挿シリンダ

【課題】高い嵌合精度と低コスト化と設計の自由度を有し、安定的な繰り返し使用を確保するとともに、使いやすさを飛躍的に向上させ得る凹型コネクタ用基板の製造方法を提供する。

【解決手段】板状コネクタを接続位置まで案内、保持するガイド保持領域と、その領域に対応する形状の切片を切除するための切り込み部とを少なくとも一端側に有するガイド用基板を準備する工程、ガイド用基板の両面に、配線と、配線と導通するスルーホール接続部とを有する2枚の配線基板を配置して位置合わせをし、ガイド用基板の所定の領域に接着剤を付与して貼り合わせる工程、配線基板の一部をガイド用基板の切り込み部の内側部分に向けて屈曲し、屈曲部分に位置する配線を切り込み部の内側に圧接させる工程、及び切り込み部の内側の切片を除去しガイド保持領域を形成する工程、を含む凹型コネクタ用基板の製造方法である。

(もっと読む)

多層回路基板の製造方法

【課題】多層回路基板の各層の配線パターンを位置精度よく容易に製造すること。

【解決手段】A.内層材の導体配線回路形成と同時に積層体と内層基板を電気的に接続するためのビアホール形成用のアライメントマークを少なくとも1つ形成する工程、B.導体配線回路上に積層体を積層する際、アライメントマークが露出するよう積層体を積層する工程と、C.内層材に形成されたアライメントマークの少なくとも1つをアライメントとして使用し、積層体にビアホールを形成する工程、D.積層体に形成されたビアホールの少なくとも1つをアライメントとして使用し、導体配線回路を形成し、さらに導体配線回路形成と同時に、その導体配線回路上にさらに積層される積層体と電気的に接続するためのビアホール形成用のアライメントマークを内層基板上に少なくとも1つ形成する工程、E.B〜Dの工程を必要な配線の層数となるまで繰り返す工程とを含む。

(もっと読む)

多層プリント配線板の製造方法

【課題】内層の配線パターン及び小径スルーホールの位置ずれを極めて小さくし、これらの接続信頼性が損なわれることのない多層プリント配線板の製造方法を得る。

【解決手段】下記のAからCの工程を少なくとも含む多層プリント配線板の製造方法である。

(A)絶縁基材に銅箔が被覆されなる内層コア基材に信号配線104及び基準マーク105を形成する工程。

(B)内層コア基材の上に絶縁層を介して銅箔を積層した後、基準マーク105に該当する位置の銅を除去して、基準マーク105を露出させる工程。

(C)基準マーク105を基準として、上層の銅箔に信号配線を形成する工程。

(もっと読む)

配線基板の製造方法

【課題】両主面に配線基板用の積層体が形成された支持基板およびその上の配線基板用の積層体を支持基板内に配置した分離フィルム同士の間で良好に分離することができ、薄型で高密度な配線基板を効率よく製造することが可能な配線基板の製造方法を提供することである。

【解決手段】中央部に幅W1および長さL1で設定された支持基板用領域Aを有する第1および第2のプリプレグ1a,1bの間にL1より短い長さL2を有する第1の分離フィルム2aおよびW2よ狭い幅W3を有する第2の分離フィルム2bを重ねて積層することにより支持基板10を形成するにあたり、プリプレグ1a,1bにガイド孔H1,H2を形成するとともに分離フィルム2aの幅方向の両端部にガイド孔H3を、分離フィルム2bの長さ方向の両端部にガイド孔H4を形成し、これらのガイド孔H1〜H4を積層治具のガイドピンに嵌合させて積層する。

(もっと読む)

電子部品の製造方法と熱プレス装置

【課題】セラミック基板含む異種積層構成において、アライメント積層の煩雑さおよび設備付加を軽減する。

【解決手段】ピンに、セラミック基板や樹脂材料部材などに設けられた各基準穴を通すことで位置合わせを簡便に行い、積層後、熱プレスの昇温プロファイルにて制御を行い、所定の樹脂粘度領域において、前記ピンを抜くと共に高圧プレスに切り替え、絶縁樹脂シートを熱硬化して硬化物を作り、その後、最終的に分割して電子部品を作製する。

(もっと読む)

多層配線基板の製造方法

【課題】製造工程を煩雑化することなく、外層配線パターンを正確に形成できるようにした多層配線基板の製造方法を提供する。

【解決手段】内層回路基板10又は該内層回路基板に積層された中間外層回路基板上に、外層絶縁層30を積層した後、内層回路基板又は中間外層回路基板に形成されたアライメントマーク22を基準にして、前記外層絶縁層にビア47用の穴を形成すると共に、外層アライメントマーク57用の穴を形成し、前記穴からなる外層アライメントマークを基準にして、外層配線パターンを形成する。

(もっと読む)

多層配線基板の製造装置及び製造方法

【課題】多層配線基板を、より効率的に、かつより高精度に製造することが可能な多層配線基板の製造装置及び製造方法を提供する。

【解決手段】製造装置1は、所定の枚数積み重ねられた配線基板A及びプリプレグBからなる積層体について仮溶着を行う仮溶着部12と、前記積層体に穴開け及び本溶着を施す穴開け部14とをもつ。このうち、仮溶着部12では、いったん仮溶着が済んだ積層体に新たな配線基板が加えられた積層体に対する更なる仮溶着が行われうる。このような処理は基本的には何回でも繰り返し可能である。そして、この繰り返し処理の間に、穴開け部14における穴開けが並行して行われる。

(もっと読む)

印刷回路基板及びその製造方法及びビアホールの穿孔装置

【課題】印刷回路基板及びその製造方法及びビアホールの穿孔装置を提供する。

【解決手段】本発明による印刷回路基板の製造方法は、絶縁基板の一面に基準マーク及びビア用ランドを含む第1回路パターンを形成する段階と、絶縁基板の一面に絶縁層を積層する段階と、絶縁層上に金属層を積層する段階と、金属層に基準マークに対応する第1ウィンドウを開口する段階と、絶縁基板の他面を介して一面側に向かって光を照射し、第1ウィンドウを介して基準マークを認知し、ビア用ランドと金属層とを電気的に接続するビアを形成する段階とを含む。印刷回路基板の回路パターン間を電気的に導通するためのビアの形成において、回路間の短絡が発生しなく、絶縁層間の偏心による基板の廃棄率を減らすことができ、原価低減に寄与できる。

(もっと読む)

多層プリント基板の製造方法

【課題】プリプレグの位置合わせを低コストで高精度に実施できる多層プリント基板の製造方法を提供することを目的とする。

【解決手段】少なくとも1枚以上の配線パターンが形成された内層基板と、プリプレグとを、加熱加圧によって積層成形する工程を有し、前記内層基板と前記プリプレグには位置合わせのためのガイド穴が設けられており、ガイド穴にガイドピンを挿入することで位置合わせを行う工程を有する多層プリント基板の製造方法において、

プリプレグ21のガイド穴91をドリル加工で穴明け加工する際、ドリル加工によって発生する摩擦熱にてガイド穴周囲101のプリプレグを熱硬化させる工程を有することを特徴とする多層プリント基板の製造方法である

(もっと読む)

プリント配線板の製造装置

【課題】部品を内蔵するプリント配線板の製造効率を向上することが可能なプリント配線板の製造装置を提供すること。

【解決手段】面内一部切り出しがある第1の配線板素材の切り出しの空間部分に第2の配線板素材を嵌め込むべく、第1の配線板素材に対して第2の配線板素材を位置合わせする位置合わせ装置と、第1の配線板素材に対して第2の配線板素材が位置合わせされた状態を固定すべく固定部材を第1の配線板素材と第2の配線板素材との境界部位に供給する部材供給機器とを具備する。

(もっと読む)

多層プリント配線板の製造方法

【課題】 プリント配線板の高位置精度スルーホール穴明け加工において、外層に形成されるスルーホールのランド位置に対して、内層回路に形成されているランド位置とのずれが生じることを防止する。

【解決手段】 内層回路形成から寸法補正値を把握し露光マスク作成、また積層する際に内層のずれを補正し、また外層スルーホール穴明け時に、内層の伸縮及びずれを補正し、その座標値を把握し穴明け作業を行うことにより、多層プリント配線板の伸縮及びずれに対して品質向上を得る。

(もっと読む)

配線基板及びその製造方法

【課題】配線基板の各層と電子部品との位置精度を向上させることにより、小型化を可能とし、さらに、一括で半導体素子、キャパシタ、抵抗体、及びインダクタ等の電子部品を配線基板内に内蔵させることより、製造時間及びコストを低減させる。

【解決手段】半導体素子、キャパシタ、抵抗、及びインダクタ等の電子部品が内蔵される配線基板において、各層の積層の際に、電子部品が実装されているフィルムキャリアのスプロケットホール等により位置合せを行うことで、配線基板の各層と電子部品との位置精度を向上させることにより、また、技術的に確立されたILB接続技術を用いることにより、半導体素子の狭ピッチ化への対応、接続の信頼性確保、さらには、上層に最短距離で配線を引き出しが可能となり、小型化を実現する。

(もっと読む)

多層配線基板の製造方法

【課題】専用の下治具を用いなくても加工装置に対する位置決めができ、しかも生産性やコスト性の低下を回避できる多層配線基板の製造方法を提供すること。

【解決手段】まず、絶縁層33,34,35,40,41,42を形成する絶縁層形成工程を行う。次に、めっきレジスト材53を用いて絶縁層33,34,35,40,41,42上にめっきレジスト54を形成するレジスト形成工程を行う。次に、閉塞体55にて第1ピン止め用孔51を閉塞した状態でめっきを行い、絶縁層33,34,35,40,41,42上に導体層36を選択的に形成する導体層形成工程を行う。積層配線部31,32の完成後に第1ピン止め用孔51を位置基準とする穴明け加工を行い、製品形成領域15に貫通孔30を透設する貫通孔形成工程を行い、多層配線基板10を完成させる。

(もっと読む)

キー接点内蔵型多層回路基板およびその製造方法

【課題】低コスト化を図ることができると共に、薄型化および軽量化ならびに実装作業を容易にしたキー接点内蔵型の多層回路基板を提供すること。

【解決手段】キー接点の一方となる導体部15を形成した第1基材11と、キー接点の他方となる導体部24を形成した第2基材21と、前記第1基材と第2基材との間に介在されて両基材を積層形成させる層間接着層41とを少なくとも備えた多層回路基板が構成される。前記層間接着層41を構成する素材の一部には開口部61が形成され、前記第1基材のキー接点の一方となる導体部15と前記第2基材のキー接点の他方となる導体部24とが、前記開口部61により形成された内層中空部内において対向するようにして配置される。

(もっと読む)

プリント配線板のVia位置ずれ検査パターン構造

【課題】多層プリント配線板においてVia位置ずれ量が許容値内にあるかの確認を容易

に実現出来るテストパターンの提供。また、製品に対して全数検査可能な手法。

【解決手段】プリント基板製品領域内の外層に検査のパッドを有し、各内層に設けられた

導体ベタパターンと貫通Viaおよび導体ベタパターンと貫通Viaを絶縁するために設

けたクリアランスから構成されるテストクーポンを配置する事により、電気的導通の有無

によりVia位置ずれ量が許容値内にあるかを容易に確認出来る。

(もっと読む)

1 - 20 / 42

[ Back to top ]