Fターム[5F003BF06]の内容

バイポーラトランジスタ (11,930) | エミッタ・ベース接合 (716) | JE接合 (461) | ヘテロJE (433)

Fターム[5F003BF06]に分類される特許

21 - 40 / 433

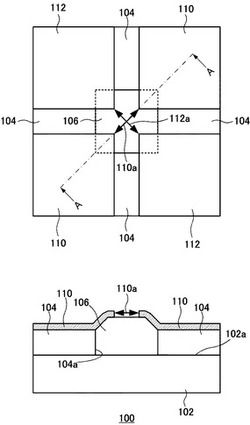

半導体基板、半導体装置および半導体基板の製造方法

【課題】十分な感度を有したp型キャリアのホール素子の製造に適した半導体基板を提供する。

【解決手段】表面の全部または一部がシリコン結晶面であるベース基板と、前記ベース基板の上に位置し、前記シリコン結晶面に達する開口を有し、結晶の成長を阻害する阻害体と、前記開口の底部の前記シリコン結晶面の上に位置する第1結晶層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第1金属層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第2金属層と、を有し、前記一対の第1金属層のそれぞれを結ぶ第1最短線と、前記一対の第2金属層のそれぞれを結ぶ第2最短線とが、交わる関係、または、ねじれの位置関係にある半導体基板を提供する。

(もっと読む)

半導体装置及び電力増幅器

【課題】トランジスタの占有面積をほとんど増やすことなく、かつ、HBTとHFETとを接続する配線による悪影響を受けないBi−HFET(半導体装置)を提供する。

【解決手段】基板101上に形成されたHFET160と、HFET160上に形成されたHBT170とを備え、HFET160は、チャネル層102と、コンタクト層104とを有し、HBT170は、HFET160のコンタクト層104と接続、又は、一体化されたサブコレクタ層107と、コレクタ層108と、ベース層109と、エミッタ層110と、エミッタキャップ層111と、エミッタコンタクト層112とを有し、コレクタ層108、ベース層109及びエミッタ層110は、メサ形状の構造体であるベースメサ領域830を構成し、ゲート電極202は、第一のコレクタ電極203とベースメサ領域830との平面的な間に設けられたリセス領域820内に形成されている。

(もっと読む)

トランジスタ用エピタキシャルウェハ

【課題】配管パージ等の作業を行うことなく、電気的特性等に影響を与える残留したTeやSeのエピタキシャル層中への混入を防止できるトランジスタ用エピタキシャルウェハを提供する。

【解決手段】基板100と化合物半導体層200とコンタクト層300とを有し、コンタクト層300は、n型不純物としてTe又はSeがドーピングされたIn組成比xが0.3≦x≦0.6で一定のn型InGaAs層からなり、n型InGaAs層は、n型不純物濃度が1.0×1019cm-3以上5.0×1019cm-3以下で、且つ、炭素濃度が1.0×1016cm-3以上3.0×1018cm-3以下であり、化合物半導体層200は、バッファ層400を備え、バッファ層400は、アンドープAlAs層からなる第1バッファ層401と、Al組成比yが0<y<1のアンドープAlGaAs層からなる第2バッファ層402とからなるものである。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】HEMTの移動度の低下を抑制することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】高電子移動度トランジスタ構造層3を、気相成長法により成長温度600℃以上750℃以下、V/III比150以下の条件で成長し、バイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下、V/III比75以下の条件で成長し、さらにノンアロイ層18を、380℃以上450℃以下の成長温度で成長する。

(もっと読む)

窒化物半導体素子の製造方法

【課題】ドレインリーク電流を低減することが可能な窒化物半導体素子の製造方法を提供する。

【解決手段】ヘテロ電界効果トランジスタ1の製造方法は、ドリフト層20aを支持基板10上にエピタキシャル成長させる工程と、水素ガスをキャリアガスとして用いて、p型半導体層である電流ブロック層20bをドリフト層20a上に1000℃以上でエピタキシャル成長させる工程と、窒素ガス、アルゴンガス、ヘリウムガス及びネオンガスからなる群より選ばれる少なくとも一種のガスをキャリアガスとして用いて、コンタクト層20cを電流ブロック層20b上にエピタキシャル成長させる工程と、を備える。

(もっと読む)

半導体装置

【課題】デバイスサイズの縮小、シリーズ抵抗の低減、及びリーク電流の抑制を可能とする半導体装置を提供することを目的とする。

【解決手段】本発明は、デバイス動作にとって、本来は不要な電位段差を発生させる層をデバイスの構造内にあえて挿入したものである。この電位段差は、バンドギャップの小さな半導体がメサ側面に露出しても、その部分の電位降下量を抑制し、デバイス動作に不都合なリーク電流を低減できる、という機能をもたらす。この効果は、ヘテロ構造バイポーラトランジスタ、フォトダイオード、及び電界吸収形光変調器などに共通して得られる。また、フォトダイオードにおいては、リーク電流が緩和されるのでデバイスのサイズを縮小することが可能となり、シリーズ抵抗の低減による動作速度の改善のみならず、デバイスを高密度にアレイ状に配置できるという利点も生まれる。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】電流利得や電流利得遮断周波数などの他の素子性能を劣化させることなく、ヘテロ接合バイポーラトランジスタのオン電圧が効果的に低減できるようにする。

【解決手段】基板101の上に、サブコレクタ層102、コレクタ層103、ベース層104、第1エミッタ層105、第2エミッタ層106、および、キャップ層107が順次積層されており、第2エミッタ層106は、第1エミッタ層105に対してウェットエッチング法により選択的に除去される半導体材料によって形成され、かつ、第2エミッタ層106を構成する半導体が不純物添加によって縮退している。加えて、このHBTの第1エミッタ層105は、ベース層104の側に配置されて不純物が添加された第1半導体層151と、第2エミッタ層106の側に第1半導体層151に接して配置されて不純物が無添加の第2半導体層152とから構成されている。

(もっと読む)

半導体装置の製造方法

【課題】パターン形成不良が発生することを抑制する。

【解決手段】まず、N型コレクタとなる基板110上に、第1開口部(不図示)を有するシリコン酸化膜120を形成する。次いで、シリコン酸化膜120及び第1開口部に露出した基板110の表面上に第1絶縁膜を形成する。次いで、第1絶縁膜をエッチバックすることにより、シリコン酸化膜120の第1開口部における側壁のみに、第1絶縁膜を残存させて、側壁部を形成する。次いで、シリコン酸化膜120等の上に、ベース引出部144となるポリシリコン膜を形成する。次いで、ポリシリコン膜上に、第2開口部(不図示)を有する第2絶縁膜を形成する。次いで、第2絶縁膜をマスクとして、ポリシリコン膜のうち、第2開口部により露出している部分を酸化してシリコン酸化膜に変化させる。次いで、シリコン酸化膜に変化させた部分を選択的に除去する。次いで、側壁部と第2絶縁膜を選択的に除去する。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの動作速度を高速化できるようにした半導体装置の製造方法を提供する。

【解決手段】単結晶Si基板1に設けられたn型のコレクタ層20と、コレクタ層20の表面の周辺部上に設けられたSiO2膜21と、SiO2膜21を覆ってコレクタ層20の表面の中央部に接合するp型のベース層30と、を有し、ベース層30は、コレクタ層20の表面の中央部上に設けられた単結晶SiGe膜31aと、SiO2膜21を覆うように単結晶SiGe膜21上に積層された単結晶Si膜35aとを含む。ベース層30とコレクタ層20との接合領域60がコレクタ層20の表面の中央部に限定されるため、接合面積を小さくすることができ、ベース層とコレクタ層との間の容量CBCを低減することができる。

(もっと読む)

トランジスタ素子及びトランジスタ用エピタキシャルウェハの製造方法

【課題】GaAs基板からHBT構造層に伝搬する転位を抑制したトランジスタ素子及びトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】GaAs基板2上に高電子移動度トランジスタ構造層3が形成され、高電子移動度トランジスタ構造層3上にヘテロバイポーラトランジスタ構造層4が形成されたトランジスタ素子において、GaAs基板2の転位密度が10,000/cm2以上100,000/cm2以下であり、高電子移動度トランジスタ構造層3とヘテロバイポーラトランジスタ構造層4との間に、InGaPからなるエッチングストッパ層12と、エッチングストッパ層12上に設けられたGaAsからなる安定化層21と、を設けたものである。

(もっと読む)

不純物濃度プロファイルの測定方法、その方法に用いられるウェーハ、および、その方法を用いる半導体装置の製造方法

【課題】半導体層の不純物濃度およびプロファイルを正確に制御することを可能とする不純物濃度プロファイルの測定方法、その方法に用いられるウェーハ、および、それを用いた半導体装置の製造方法を提供する。

【解決手段】基板10と、前記基板10の主面上に設けられた半導体層12,17であって、前記主面上において互いに面積の異なる複数の第1領域17a,17bに形成された第1の部分と、前記主面上で前記第1領域17a,17bを取り囲む第2領域17cに形成され前記第1の部分とは異なる構造を有する第2の部分と、を有する半導体層12,17と、を有するウェーハを用いる。そして、前記半導体層のうちの複数の前記第1の部分の表面から深さ方向の不純物濃度プロファイルを測定し、前記第1の部分の面積に依存する前記不純物濃度プロファイルの変化を求める。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】BiFETデバイスに含まれるFETのオン抵抗の悪化を抑制する。

【解決手段】共通基板1上に第1SL10及び第2SL20積層体が順に形成された半導体装置であって、第2積層体が除去されて残存する第1積層体は、電界効果型トランジスタを構成し、第1積層体上に積層された第2積層体は、電界効果型トランジスタとは異なる素子(バイポーラトランジスタ)を構成し、電界効果型トランジスタを構成する第1積層体は、第1積層体に形成されるリセスの停止位置を規定し、かつInGaPから成るエッチング停止層10と、リセス内に配置されるゲート電極25の下方に配置され、かつAlGaAsから成る下部化合物半導体層8と、エッチング停止層10と下部化合物半導体層8との間に挿入され、エッチング停止層に含まれるリンが下部化合物半導体層まで熱拡散し、下部化合物半導体層を構成する元素と化合することを抑止するスペーサ層9とを含む。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】セルフアライメントにより容易に電極を形成することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】エッチングストッパ層2の上方に、Sbを含み、所定の溶液に対するエッチング耐性がエッチングストッパ層2よりも低いSb含有層3bを形成し、Sb含有化合物半導体層3b上に、Asを含み、前記所定の溶液に対するエッチング耐性がエッチングストッパ層2よりも低いAs含有層3cを形成する。そして、前記所定の溶液を用いて、導電膜4をエッチングマスクとし、Sb含有層3b及びAs含有層3cをメサ状にウェットエッチングし、平面視でSb含有層3b及びAs含有層3cから離間した位置において化合物半導体層1の上方に導電膜5aを形成する。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体素子

【課題】 GaN基板上に結晶成長する各半導体層の平坦性向上した半導体基板を実現し、この半導体基板を基礎として、特性の高性能化された半導体素子を提供する。

【解決手段】n型基板11と、n型基板11上に積層された窒化物系III−V族化合物半導体単結晶からなるn型ドリフト層24と、n型ドリフト層24上に設けられた窒化物系III−V族化合物からなるp型ベース層25と、p型ベース層25上に設けられた窒化物系III−V族化合物からなるn型エミッタ層26と、n型基板11とn型ドリフト層24との間に設けられた、Siを5x1017cm-3以上2x1019cm-3以下含有する層とを備える。

(もっと読む)

半導体装置、半導体回路基板および半導体回路基板の製造方法

【課題】化合物半導体材料を節減しつつ化合物半導体を用いた高性能な半導体素子を得ることができる半導体装置、半導体回路基板および半導体回路基板の製造方法を提供する。

【解決手段】半導体回路基板が、トランジスタ形成基板10と回路形成基板50とを有する。トランジスタ形成基板10は、GaN基板であり、表面にBJT40が形成されている。トランジスタ形成基板10の裏面は平滑であり、かつ裏面にコンタクト領域を有する。回路形成基板50は、化合物半導体以外の材料で形成され、半導体能動素子を有さない。回路形成基板50は、平滑な表面、表面に露出するように埋め込まれたコンタクト領域52、54、および受動回路(図示せず)を有する。トランジスタ形成基板10と回路形成基板50は、絶縁膜等の他の膜を介在させずに直接に接合している。

(もっと読む)

半導体装置

【課題】同一基板上にヘテロ接合バイポーラトランジスタ(HBT)と電界効果トランジスタ(FET)とが形成され、HBTのコレクタ抵抗が低減されてHBTの特性が向上され、かつFETのゲートリセスのエッチング精度が良好で、FETのオン抵抗が低い半導体装置を安定的に提供する。

【解決手段】HBT101Aにおいては、サブコレクタ層が複数の半導体層13〜15の積層構造からなり、かつ、サブコレクタ層においてコレクタ層17より張り出した部分上にコレクタ電極28が形成されている。FET101B、101Cにおいては、HBT101Aのサブコレクタ層をなす複数の半導体層のうち半導体基板1側の少なくとも1層の半導体層13が、キャップ層の少なくとも一部の層を兼ねている。HBTサブコレクタ層の総膜厚が500nm以上であり、FETキャップ層の総膜厚が50nm以上300nm以下である。

(もっと読む)

半導体装置の製造方法

【課題】本発明の実施形態は、ベース層の幅を狭く形成しエミッタ層の不純物濃度を高くした低雑音特性を有する半導体装置の製造方法を提供することを目的とする。

【解決手段】一実施形態に係る半導体装置の製造方法は、第1導電型の第1半導体層の上に第2導電型の第2半導体層を成長する半導体装置の製造方法であって、前記第1半導体層の表面を常圧よりも低い圧力の還元性雰囲気に曝して熱処理する工程(S02〜S04)と、前記第1半導体層の表面上に、前記第2半導体層を常圧の雰囲気でエピタキシャル成長する工程(S05〜S07)と、を備えたことを特徴とする。

(もっと読む)

バイポーラトランジスタ

【課題】高速動作性・高電流駆動力を有するヘテロ接合バイポーラトランジスタ及びその製造方法を提供する。

【解決手段】バイポーラトランジスタは、コレクタとして機能するSi単結晶層3と、Si単結晶層3の上に形成された単結晶のSi/SiGeC層30a及び多結晶のSi/SiGeC層30bと、エミッタ開口部を有する酸化膜31と、エミッタ電極50と、エミッタ層35とを備えている。単結晶のSi/SiGeC層30aに真性ベース層52が形成され、単結晶のSi/SiGeC層30aの一部と多結晶のSi/SiGeC層30bとCoシリサイド層37bとにより、外部ベース層51が構成されている。エミッタ電極の厚みは、エミッタ電極50に注入されたボロンがエミッタ電極50内を拡散して、エミッタ−ベース接合部まで達しないように設定されている。

(もっと読む)

21 - 40 / 433

[ Back to top ]