Fターム[5F033PP14]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | PVD(物理的気相成長法) (5,261)

Fターム[5F033PP14]の下位に属するFターム

スパッタ (4,083)

真空蒸着 (553)

イオンビーム蒸着、イオンプレーティング (95)

Fターム[5F033PP14]に分類される特許

61 - 80 / 530

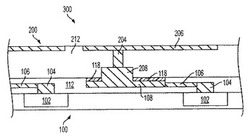

半導体構造同士を直接結合する方法、およびこの方法を使用して形成された結合された半導体構造

【課題】半導体構造同士を直接結合する方法を提供すること。

【解決手段】本発明の実施形態は、半導体構造同士を直接結合する方法を含む。いくつかの実施形態では、半導体構造の直接結合された金属フィーチャ間の境界面に、キャップ層を提供することができる。いくつかの実施形態では、半導体構造の直接結合された金属フィーチャ内に、不純物が提供される。そのような方法を使用して、結合された半導体構造が形成される。

(もっと読む)

分離トレンチの形成方法

【課題】隣接デバイスの特性への悪影響を低減するTSV相互接続構造の製造方法を提供する。

【解決手段】第1の主面S1を有する基板を設け、少なくとも一つのTSV穴部と、TSV穴部を囲み残りの基板材料によって分離されるトレンチ状構造3、とをエッチングにより同時に作製する。基板の第1の主面でトレンチ状構造の開口をピンチオフするためと、TSV穴部側壁を平滑にするために、誘電性のライナー2a、2bを堆積し、トレンチ状構造にエアギャップ4を作製する。TSV相互接続10を生成するためにTSV穴部に導体材料を堆積する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル部に印加される応力を増加させて、電流増加効果を高めることを可能とする。

【解決手段】半導体基板上にダミーゲートを形成した後、該ダミーゲートの側壁に側壁絶縁膜を形成し、該ダミーゲートの両側の前記半導体基板にソース・ドレイン領域を形成する工程と、前記ダミーゲートおよび前記ソース・ドレイン領域の上に応力印加膜を形成する工程と、前記ダミーゲートの上の領域に形成された前記応力印加膜と前記ダミーゲートを除去して溝を形成する工程と、前記溝内の前記半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、を備えた半導体装置の製造方法。

(もっと読む)

半導体装置、その製造方法、および半導体装置を含む半導体パッケージ

【課題】装置特性の低下を防止するとともに、半導体基板と貫通電極の短絡を防止する半導体装置を提供する。

【解決手段】第1面と、第1面と対向してトレンチが形成された第2面とを有する基板と、基板内に形成されたビアホールを充填し、ビアホールの内壁から順にビアホール絶縁膜、障壁膜、および導電性接続部を有してなる貫通ビアと、第2面上に形成されて貫通ビアの一部領域を露出する開口部を有する絶縁膜と、トレンチ内に埋め込まれ、貫通ビアと電気的に接続される再配線と、を有し、絶縁膜は導電性接続部の一部領域と重複する。

(もっと読む)

パターン化金属膜及びその形成方法

【課題】ドライエッチングが困難な遷移金属の膜を、サイドエッチングが極力生じないようにパターニングする。

【解決手段】絶縁膜の上にバリア層・密着層を形成し(S1)、その上に遷移金属からなるシード層を形成する(S2)。シード層の上にSiO2膜及びフォトレジスト膜を順次形成し(S3、S4)、フォトレジスト膜、SiO2膜をパターニングして開口を形成し(S5,S6)、開口内にCu膜及びマスクAl膜を積層する(S7、S8)。次に、SiO2膜をエッチング(S9)、露出したシード層をその膜厚方向に異方的に改質し(S10)、改質されたシード層、露出したバリア・密着層、及びマスクAl膜を順次エッチングにより除去することにより(S10〜S13)、パターン化金属膜を得る。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

エアブリッジの製造方法

【課題】エアブリッジの強度低下抑制、半導体素子の特性悪化抑制およびスペーサ材料残りの問題の回避を達成しつつ、被覆面積の大きなエアブリッジを製造することができるエアブリッジの製造方法を提供する。

【解決手段】レジスト層100の上に、二層目のレジスト層であるレジスト層102を塗布する。レジスト層102についても、一層目(レジスト層100)と同様に、所定の寸法W2を残すように露光現像を行い、その後、三層目のレジスト(レジスト層104)を塗布する。三層目(レジスト層104)においても所定の寸法W3を残すように露光現像を行う。形作られたレジスト層102、104、106の積層構造上に、エアブリッジ10を形成する材料の層106を積層することにより、エアブリッジ10の形成を行う。レジスト除去を行うことにより、断面形状が階段形状であるエアブリッジ10が完成する。

(もっと読む)

成膜方法、成膜装置及び半導体装置の製造方法

【課題】熱CVD法によって、M(BH4)4(Mは、Zr又はHfを意味する)を原料としてM/Zr比が適正範囲内で良質なMBx膜(Mは前記と同じ意味を有し、xは1.8〜2.5の数を意味する)を成膜する。

【解決手段】ガス供給源19から、ガス供給配管15aを介してH2ガスを原料容器21内に供給する。原料容器21内では、導入されたH2ガスとの接触によって、固体原料のZr(BH4)4が気化する。そして、成膜ガスとしてのH2ガスとZr(BH4)4ガスの混合ガスが、ガス供給配管15c,15c1、シャワーヘッド11のガス拡散空間12及びガス吐出孔13を介して処理容器1内に導入され、ウエハW上の絶縁膜の表面を覆うように、ZrBx膜の薄膜が形成される。

(もっと読む)

半導体装置及び電源装置

【課題】半導体装置において、抵抗が増大して変換効率が低下してしまうのを防止する。

【解決手段】半導体装置を、基板2上に形成されたGaN系半導体積層構造3を有する第1トランジスタQ1と、GaN系半導体積層構造を有する第2トランジスタQ2とを備え、第1トランジスタが、複数の第1フィンガ8AXを有する第1ゲート電極8Aと、複数の第1ドレイン電極9Aと、複数の第1ソース電極10Aとを備え、第2トランジスタが、複数の第2フィンガ8BXを有する第2ゲート電極8Bと、複数の第2ドレイン電極9Bと、複数の第2ソース電極10Bとを備え、複数の第1ドレイン電極の上方又は下方に接続されたドレインパッド15と、複数の第2ソース電極の上方又は下方に接続されたソースパッド25と、複数の第1ソース電極及び複数の第2ドレイン電極に接続された共通パッド35とを備えるものとする。

(もっと読む)

装置

【課題】ボイドが存在しても高い信頼性を確保可能な配線構造を提案する。

【解決手段】実施形態に係わる装置は、第1の溝10を有する絶縁層13と、第1の溝10内に形成され、上部に凹部16を有する銅を含む第1の配線層15と、第1の配線層15の凹部16の内面上に形成され、少なくとも1つのグラフェンシートから構成されるグラフェン層17とを備える。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線は、配線溝を有する絶縁膜13と、前記配線溝内の両側面の前記絶縁膜上に形成された第1触媒膜15と、前記配線溝内の両側面の前記第1触媒膜上に形成され、両側面に対して垂直方向に積層された複数のグラフェンシートで構成された第1グラフェン層16と、を具備する。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線の製造方法は、絶縁膜13内に、配線溝30を形成し、前記配線溝内の全面に、触媒膜14を形成し、前記配線溝内の前記触媒膜上に、前記配線溝の底面に対して垂直方向に積層された複数のグラフェンシート16a〜16eで構成されるグラフェン層16を形成することを具備する。

(もっと読む)

重合体、膜形成用組成物、絶縁膜、半導体装置および重合体の製造方法

【課題】エッチング工程によってもダメージを受けにくい絶縁膜を形成し得る重合体を含む膜形成用組成物、前記絶縁膜、該絶縁膜を備える半導体装置、さらには前記重合体の製造方法を提供すること。

【解決手段】本発明の膜形成用組成物は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する化合物Cを含む重合性化合物を重合することにより得られる、分散比が1.0以上2.5以下の重合体を含むものである。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタル層の金属配線に対する密着性を向上させつつ、金属配線の低抵抗化を図った半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜15に形成された凹部16、17内にバリアメタル層20を形成した後、凹部16、17内にCu配線層23を形成する。バリアメタル層20の形成工程は、凹部16、17内にTi含有量が50原子%を超える第1のTiNx膜18を形成した後、側壁部上と比較して底部上に相対的に多く形成されるように、Ti含有量が第1のTiNx膜18より多い第2のTiNx膜(またはTi膜)19を形成する。

(もっと読む)

半導体装置の製造方法

【課題】異方的にエッチングされた銅膜に、簡単で実用的にCuバリア膜を形成できる半導体装置の製造方法を提供すること。

【解決手段】Cuバリア膜100上に、銅膜101を形成する工程と、銅膜101上に、マスク材102を形成する工程と、マスク材102をマスクに用いて、銅膜101をCuバリア膜100が露出するまで異方的にエッチングする工程と、マスク材102を除去した後、異方的にエッチングされた銅膜101上に、銅膜101に対して触媒作用があり、Cuバリア膜100には触媒作用がない選択析出現象を利用した無電解めっき法を用いて、銅の拡散を抑制する物質を含むめっき膜104を形成する工程と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】異方性エッチングを利用して、1つの銅膜に配線パターンとビアパターンとを同時に形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】バリア膜100上に、銅膜101を形成する工程と、銅膜101上に、第1のマスク材を形成する工程と、第1のマスク材をマスクに用いて、銅膜101をバリア膜100が露出するまで異方的にエッチングする工程と、第1のマスク材を除去した後、異方的にエッチングされた銅膜101上に、第2のマスク材を形成する工程と、第2のマスク材をマスクに用いて、銅膜101をその途中まで異方的にエッチングする工程と、前記第2のマスク材を除去した後、異方的にエッチングされた銅膜101上に、絶縁物を堆積させ、異方的にエッチングされた銅膜101周囲に、層間絶縁膜106を形成する工程と、を具備する。

(もっと読む)

ヒータ配線付き半導体チップ

【課題】半導体チップの高信頼実装技術を提供。

【解決手段】半導体チップ4は、基板100と、前記基板の一方の面に形成されたデバイス層80と、電磁波の輻射により発熱するヒータ配線302と、前記デバイス層と電気的に接続される電極103とを備えることを特徴とする。半導体チップ4を実装基板に実装する際には、ヒータとしての金属配線膜302を発熱させることにより、固着材料を溶かして半導体チップを実装基板と接続させる。

(もっと読む)

カーボンナノチューブ配線の製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】カーボンナノチューブ配線の製造方法は、第1導電層200上に、絶縁膜18を形成し、前記絶縁膜内に、前記絶縁膜を貫通するホール40を形成し、前記ホール内の底面の前記第1導電層上および前記ホール内の側面の前記絶縁膜上に、触媒下地膜19を形成し、前記ホール内の側面の前記触媒下地膜上に、触媒不活性膜20を形成し、前記ホール内の底面の前記触媒下地膜上および前記ホール内の側面の前記触媒不活性膜上に、触媒膜21を形成し、前記ホール内の底面の前記触媒膜上から複数のカーボンナノチューブ22を成長させる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

半導体装置およびその製造方法

【課題】ダマシン構造を有するCu配線において、バリア膜の拡散防止機能を低下させずにCu配線内のCuの埋め込み性を改善し、半導体装置の歩留まりおよび信頼性を向上する。

【解決手段】ダマシン配線を有する半導体装置において、第2層間絶縁膜6に形成した配線溝G2およびビアホールV2のそれぞれの内壁にバリア膜としてTaN膜7およびCuと濡れ性の良いTiからなるTi膜8とを順に形成することにより、Ti膜8上に均一にCuシード膜9aを形成することを可能とする。これにより、Cuシード膜9aを電極として電界メッキ法によりCu膜9を形成した際に、配線溝G2およびビアホールV2内に空隙が形成されることを防ぐ。

(もっと読む)

61 - 80 / 530

[ Back to top ]