Fターム[5F033PP14]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | PVD(物理的気相成長法) (5,261)

Fターム[5F033PP14]の下位に属するFターム

スパッタ (4,083)

真空蒸着 (553)

イオンビーム蒸着、イオンプレーティング (95)

Fターム[5F033PP14]に分類される特許

101 - 120 / 530

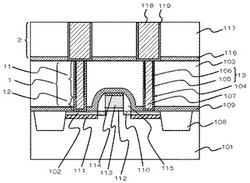

半導体装置及びその製造方法

【課題】ボイドやシームが発生しにくい構造体とする。

【解決手段】本発明の半導体装置は、半導体基板101に形成された層間絶縁膜103と、層間絶縁膜103に形成されたコンタクト孔104と、コンタクト孔104を埋め込むCu膜107と、コンタクト孔104の内部の側壁に形成され、Cu膜107の下地となる金属含有下地膜13と、を備える。コンタクト孔104の開口に接続している側壁の一部を含む第一の領域11において、金属含有下地膜13は、Cu膜107との界面に金属窒化層106を有する。第一の領域11よりも半導体基板101側の側壁を含む第二の領域12において、金属含有下地膜13は、Cu膜107との界面に金属層105を有する。金属層105の表面におけるCu膜107の成膜速度は、金属窒化層106の表面におけるCu膜107の成膜速度よりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】誘電率が低くかつ金属との密着性に優れた絶縁層を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板(シリコン基板)と、基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜12bと、多孔質SiOCH膜12bに設けられた凹部と、凹部を埋め込むように設けられた金属膜(Cu膜22b)と、Cu膜22bと接しており、凹部内の多孔質SiOCH膜12bの表面に設けられた、改質層31bと、を備え、改質層31bは、多孔質SiOCH膜12bの内部と比較して、C/Si比が小さく、かつO/Si比が同等である。

(もっと読む)

絶縁膜および半導体装置

【課題】誘電率の低い絶縁膜であって、半導体装置の製造においてCMP法により当該絶縁膜上の膜を好適に除去することができるとともに、キャップ層を備えておらず、かつ、信頼性に優れた半導体装置の製造に好適に用いることができる絶縁膜を提供すること。

【解決手段】本発明の絶縁膜は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて形成された絶縁膜であって、0.03〜20μmの膜厚を有し、ナノインデンターを用いて、膜厚の2分の1以上の最大押し込み深さにおいて、弾性率測定変位を膜厚の10分の1とする測定から求められる弾性率が、4.0GPa以上であることを特徴とする。

(もっと読む)

絶縁膜、半導体装置および膜形成用組成物

【課題】無機膜との密着性に優れ、銅配線のヒロックを抑制できる絶縁膜、該絶縁膜を備える半導体装置及び該絶縁膜を提供できる膜形成用組成物を提供すること。

【解決手段】本発明の絶縁膜は、1分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む膜形成用組成物を用いて形成された絶縁膜であって、該絶縁膜とSiCN膜とを用いて測定される、m−ELT法による密着力が、0.15MPa・m(1/2)以上0.35MPa・m(1/2)以下であることを特徴とする。前記重合性反応基は、芳香環と、当該芳香環に直接結合するエチニル基またはビニル基とを有するものであり、前記重合性化合物において、前記芳香環由来の炭素の数は、当該重合性化合物全体の炭素の数に対して、15%以上、38%以下であるのが好ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の表皮効果の抑制と低抵抗化を図る。

【解決手段】第1配線部41と、その第1配線部41の周りを被覆する、高融点金属窒化物を含む第2配線部42とを含む配線40aを形成する。このような配線40aにおける第2配線部42は、第1配線部41側から外周に向かって窒素含有率が高くなる部分を有するように形成する。これにより、配線40aにおける表皮効果が抑制されると共に、配線40aの低抵抗化が図られるようになる。

(もっと読む)

基板貫通の相互接続部を形成する方法

【課題】表側と裏側とを有する基板を含むマイクロエレクトロニクス・デバイスに基板を貫通する相互接続部を形成する方法を提供する。

【解決手段】基板の表側に回路素子(134)を形成するステップと、回路素子(134)に達するトレンチ(138)を基板の裏側に形成するステップと、ポリマー絶縁材料からなる層(140)をトレンチ(138)内に形成するステップと、ポリマー絶縁材料からなる層(140)を基板の表側から露出させるために、回路素子(134)に開口(150)を形成するステップと、ポリマー絶縁材料からなる層(140)のうち開口(150)によって露出された部分を基板の表側から除去するステップと、回路素子(134)と電気的に通じている導電相互接続層(142)をトレンチ(138)内に形成するステップと、を有する。

(もっと読む)

半導体装置の製造方法

【課題】形状制御性良く、タングステンを含む導電層のエッチングを行える半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層上にタングステンを含む導電層を形成する工程と、導電層を選択的にエッチングし、導電層の表面から下地層に達する深さよりも浅い溝を形成する工程と、溝を形成した後、臭素を含むガスを用いて、溝内の導電層の側面及び底面にタングステンと臭素との化合物を含む保護膜を形成する工程と、導電層の底面の保護膜を除去する工程と、導電層の底面の保護膜を除去した後、導電層の側面に保護膜が形成された状態で、導電層における溝より下の部分をエッチングする工程と、を備えた。

(もっと読む)

酸化表面層のハイブリッドその場ドライクリーニングプロセス

【課題】 集積回路における酸化表面層の洗浄を行うための新しいドライクリーニングプロセスの提供。

【解決手段】 一の実施例によると、当該方法は、酸化表面層を有する金属含有バリア層を含む基板を供する工程、前記酸化表面層を活性化させるために、プラズマ励起されたアルゴン気体を含む第1処理気体流へ前記酸化表面層を曝露する工程、及び、前記の第1処理気体流へ酸化表面層を曝露する工程中に基板バイアス電力を印加する工程を有する。当該方法は、非プラズマ励起された水素気体を含む第2処理気体へ前記の活性化した酸化表面層を曝露する工程をさらに有する。前記の第1処理気体流へ酸化表面層を曝露する工程は、前記酸化表面層を活性化させるのに加えて、水素気体を含む前記第2処理気体による、前記活性化した酸化表面層の還元を助ける。前記金属含有バリア層の厚さは、ハイブリッドその場ドライクリーニングプロセスによって実質的には変化しない。

(もっと読む)

プロセス均一性及び熱消散を改善するダミーTSV(スルーシリコンビア)

【解決手段】

各々が能動回路領域を含むチップの積層体において、多重チップ積層体内の複数のスルーシリコンビア(TSV)開口をパターニングし、エッチングし、そして熱的伝導性材料で充填することによって、多重チップ積層体からの熱を熱的に伝導させるための複数のTSV構造が形成され、複数のTSV開口は、いずれの能動回路領域をも貫通せずに多重チップ積層体の実質的に全体を通って延びる第1の大きなTSV開口と、能動回路領域まで下に延びるが通過はしない第2の小さい開口と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ポーラス絶縁層を用いた半導体装置において、当該ポーラス絶縁層を覆うポアシール絶縁層を良好に形成すること。

【解決手段】本発明に係る半導体装置の製造方法は、(A)ポーラス絶縁層の表面にトレンチを形成する工程と、(B)ビニル基を含み−Si−O−を含む構造を備える化学物質を、ポーラス絶縁層の表面上あるいはポーラス絶縁層中に導入する工程と、(C)当該化学物質の重合を行うことにより、ポーラス絶縁層よりも高密度のポアシール絶縁層をトレンチの表面上に形成する工程と、を含む。

(もっと読む)

マンガン含有低誘電率膜及びその製造方法、半導体装置の製造方法並びに成膜装置

【課題】マンガン含有材料を利用して、低誘電率膜への銅の拡散を防止する。

【解決手段】成膜装置100では、制御部70の制御に基づき、処理容器1内を真空にして、ヒーター6によりウエハWを加熱しつつ、シャワーヘッド11のガス吐出孔13a,13bからウエハWへ向けて低誘電率材料とマンガン含有材料とを含む成膜ガスを供給する。高周波電源23からシャワーヘッド11に高周波電力を供給することにより、成膜ガスを解離させ、処理容器1内に成膜ガスのプラズマを生成させる。このプラズマによって、ウエハWの表面にMnを含有するSiCOH膜を成膜する。

(もっと読む)

ビア及びエッチングされた構造におけるコンフォーマル絶縁層の形成方法及びパターン形成方法

マスク層の下にアンダーカット形状を形成するエッチングプロセスによって基板にビアが形成される。ビアはコンフォーマルな絶縁層で覆われ、この構造にエッチングプロセスを実施して水平面から絶縁層を取り除くと共にビアの垂直な側壁の絶縁層を残す。ビアの上部領域はエッチバックプロセスの際、アンダーカットハードマスクによって保護される。  (もっと読む)

(もっと読む)

絶縁膜、積層体、半導体装置および半導体装置の製造方法

【課題】誘電率が低く、半導体装置の製造に適用した際に絶縁不良等の問題を生じにくい絶縁膜を提供すること。

【解決手段】本発明の絶縁膜は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて形成されたものであって、フッ素系ガスでエッチングした際のエッチングレートが、SiO膜の0.75倍以下であることを特徴とする。前記重合性反応基は、芳香環と、当該芳香環に直接結合するエチニル基またはビニル基とを有するものであり、前記重合性化合物において、前記芳香環由来の炭素の数は、当該重合性化合物全体の炭素の数に対して、15%以上、38%以下であるのが好ましい。

(もっと読む)

プラズマ化学気相堆積による、有機官能基と共にシリコンを含有するハイブリッド前駆体を使用する超低誘電材料

低誘電率層を基板上に堆積するための方法が提供される。一実施形態では、本方法は、1種または複数のオルガノシリコン化合物をチャンバに導入するステップであって、1種または複数のオルガノシリコン化合物がシリコン原子およびこのシリコン原子に結合されたポロゲン成分を含むステップと、1種または複数のオルガノシリコン化合物を、RF電力の存在下で反応させることにより、低誘電率層をチャンバ内の基板上に堆積させるステップと、低誘電率層からポロゲン成分が実質的に除去されるようにこの低誘電率層を後処理するステップとを含む。任意選択で、不活性キャリアガス、酸化ガス、またはその両方を、1種または複数のオルガノシリコン化合物と共に処理チャンバ内に導入してもよい。後処理プロセスは、堆積した材料の紫外線硬化とすることができる。UV硬化プロセスは、熱または電子ビーム硬化プロセスと同時にまたは連続して使用してもよい。低誘電率層は、良好な機械的性質および望ましい誘電率を有する。  (もっと読む)

(もっと読む)

半導体装置

【課題】本発明は小型化を図ると共に、デバイス形成層を保護した状態で貫通孔及び貫通電極を形成することを課題とする。

【解決手段】デバイス形成層18と電極パッド20を有する半導体素子14の電極パッド20と半導体素子14の他面側に形成された再配線パターン52とを接続する貫通電極56を有する半導体装置50であって、半導体素子14の上面側にデバイス形成層18及び電極パッド20を形成し、電極パッド20及びデバイス形成層18の表面に第1レジスト層62を形成し、電極パッド20にエッチングにより開口64を形成し、開口64に連通する位置に貫通孔54をエッチングにより半導体素子14に形成する。第1レジスト層62によりデバイス形成層18を保護すると共に、貫通電極56を設けてフリップチップ接続を可能にして小型化を図る。

(もっと読む)

半導体装置の製造方法

【目的】ウェット処理を行った場合でも絶縁膜上に庇形状が形成されない半導体装置の製造方法を提供する。

【構成】本発明の一態様の半導体装置の製造方法は、基板上に絶縁膜を形成する工程(S102)と、絶縁膜上に保護膜を形成する工程(S104)と、保護膜に第1の開口部を形成する工程(S114)と、第1の開口部内に保護膜よりもウェットエッチングレートが大きい犠牲膜を形成する工程(S116)と、第1の開口部内の犠牲膜に第1の開口部よりも幅の狭い第2の開口部を形成する工程(S122の一部)と、第2の開口部を転写することで絶縁膜に第3の開口部を形成する工程(S122の一部)と、第3の開口部が形成された後に、ウェット処理を行なう工程(S126)と、ウェット処理後に、第3の開口部内にバリアメタル膜を形成する工程(S128)と、第3の開口部内に導電性材料を埋め込む工程(S132)と、を備えたことを特徴とする。

(もっと読む)

積層回路材料

【課題】特性インピーダンスを小さくできるために、超高周波又は超高速信号の伝送時においても反射や放射が少なく、かつ低損失である回路材料を提供する。

【解決手段】単一元素からなる原子層が単層若しくは複数層で構成する導体層と、導体層を構成する元素同士間の原子間結合よりもより安定な結合を形成する単一又は復数の元素からなる原子層が単層若しくは複数層で構成する拘束層とからなり、前記導体層と拘束層の原子同士が原子的整合状態(ヘテロ構造)で積層することを特徴とする回路材料の電気抵抗低下方法。

(もっと読む)

半導体装置及びその製造方法

【課題】発熱に対して効率的に冷却を行うことができる、半導体装置を提供する。

【解決手段】半導体層の表面に形成された活性領域5,6と、N型の不純物を有する半導体から成るN型ゲート7Nと、P型の不純物を有する半導体から成るP型ゲート7Pと、N型ゲート7N及びP型ゲート7P及び活性領域5,6に接続された第1の金属配線13と、P型ゲート7P及びN型ゲート7Nに接続された第2の金属配線と15、第2の金属配線15に接続され、熱を外部に放出するための放熱部19とを含む冷却機構素子を備えた半導体装置を構成する。

(もっと読む)

ダマシンインターコネクトのエレクトロマイグレーション抵抗を向上させる界面層

【課題】、ダマシンインターコネクトのエレクトロマイグレーション特性を向上させるべく銅線内に保護キャップを形成する方法を提供する。

【解決手段】a)酸化物を含まない銅または銅合金107の露呈領域と誘電体の露呈領域とを含む基板100を、アルミニウムを含む化合物に、少なくとも約摂氏350度の基板温度で曝して、前記誘電体および前記銅または銅合金の層の両方の上にアルミニウムを含む第1の層を形成する工程と、(b)前記第1の層の少なくとも一部を化学的に修正して、アルミニウムを含むパッシベーション層109を形成する工程と、(c)前記パッシベーション層の上に誘電体層111.を堆積させる工程とを備える方法。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

101 - 120 / 530

[ Back to top ]