Fターム[5H730AS01]の内容

DC−DCコンバータ (106,849) | 用途 (11,272) | 定電圧電源 (3,623)

Fターム[5H730AS01]に分類される特許

161 - 180 / 3,623

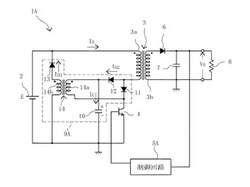

スイッチング電源装置

【課題】コストを増大させることなく、高効率化を実現できるスイッチング電源装置を提供する。

【解決手段】直流電源2に直列接続された主トランス3およびスイッチング素子4と、スイッチング素子4を制御する制御回路5Aと、スイッチング素子4がターンオフした際に充電されてスイッチング素子4がターンオンした際に放電するコンデンサ10と、コンデンサ10の放電電流が流れる一次側巻線14aおよび放電電流に応じた二次電流を発生させる二次側巻線14bからなる補助トランス14とを備えたスイッチング電源装置1Aであって、主トランス3の一次側巻線3aとスイッチング素子4との間に設けられ、主トランス3の一次側巻線3aからスイッチング素子4に向かう方向に順方向接続された第1ダイオード11をさらに備え、放電電流は、第1ダイオード11とスイッチング素子4との接続部に流れ込んだ後、スイッチング素子4側に流れることを特徴とする。

(もっと読む)

力率改善回路およびその制御回路、それらを用いた電子機器

【課題】PFC回路の温度特性の改善にある。

【解決手段】第1V/I変換回路10は、PFC回路200に入力される全波整流波形を有する交流電圧VACに応じた第1電圧V1を、第1抵抗R1に印加することにより第1電流I1を生成する。第1誤差増幅回路18は、PFC回路200の出力電圧VDCに応じた第1検出電圧VSと所定の基準電圧VREFとの誤差を増幅し、第2電圧V2を生成する。第2V/I変換回路12は、第2電圧V2を第2抵抗R2に印加することにより第2電流I2を生成する。第3V/I変換回路14は、所定の電圧VBGRを第3抵抗R3に印加することにより第3電流I3を生成する。乗算器20は、第1電流I1と第2電流I2を乗算し、第3電流I3により除算した第4電流I4を生成し、第4電流I4を第4抵抗R4に流すことにより、第4電圧V4を生成する。

(もっと読む)

力率改善回路およびその制御回路、それらを用いた電子機器

【課題】入力電力の増大にともない、PFC回路の最大電力が増大する。

【解決手段】第1誤差増幅回路18は、DC/DCコンバータの出力電圧VDCに応じた第1検出電圧Vsと所定の基準電圧VREFとの誤差を増幅し、第2電圧V2を生成する。電圧レベル判定回路15は、第1電圧V1の振幅レベルに応じた離散的なレベルをとる第3電圧V3を生成する。乗除算回路17は、第1電圧V1と第2電圧V2を乗算し、第3電圧V3で除算することにより、第4電圧V4を生成する。コンパレータ45は、DC/DCコンバータのスイッチングトランジスタM1に流れる電流IM1に応じた第2検出電圧VIと、第4電圧V4とを比較する。駆動回路40aは、所定の周期ごとにスイッチングトランジスタM1をオンし、コンパレータ45の出力に応じて、第2検出電圧VIが第4電圧V4より高くなるごとにスイッチングトランジスタM1をオフする。

(もっと読む)

電源装置

【課題】冗長構成による複数の電源部の故障を予防するとともに、異常が発生した電源部を個別に切り離すことが可能な電源装置を提供する。

【解決手段】電源装置を構成する複数の電源部に、並列冗長および待機冗長を併用する。各電源部の入力段にリレー部を、出力段にFETスイッチ部を、それぞれ設けて、個別に電気的に切り離すことを可能とする。また、故障時以外にも、各電源部の待機状態および稼動状態を定期的に切り替える制御を行うことによって、各電源部の故障を防ぎ、電源装置全体としての寿命を延ばす。

(もっと読む)

電源装置及び画像形成装置

【課題】蓄電装置未使用時において電力損失が大きくならないようにする。

【解決手段】商用AC電源から供給される電力を入力源に用いる定電圧出力の主電源30と、商用AC電源から供給される電力を蓄電するキャパシタ37及びこのキャパシタ37の電力を入力源に用いる補助電源32と、を備え、主電源30の出力と補助電源29の出力とを並列に接続し、主電源30からの電力と補助電源29からの電力を同時に24V系負荷35に供給する電源装置であって、24V系負荷35の前段に当該負荷に流れる電流を検出する電流検出抵抗60と、この電流検出抵抗60と並列に設けたSW素子(リレー)71を備え、前記補助電源32の未使用時は、前記SW素子71を介して24V系負荷35に電力を供給する。

(もっと読む)

DC−DCコンバータの制御装置

【課題】スイッチングパルスのスキップを過電圧保護回路の出力によって行い、軽負荷における出力電圧精度の向上と重負荷における過電圧保護動作後の速やかな通常制御への復帰とを共に実現するDC−DCコンバータの制御装置を提供する。

【解決手段】出力信号の帰還電圧との基準電圧との差電圧を増幅して誤差電圧を出力する誤差増幅器11と、前記帰還電圧が過電圧閾値を超えた場合にスキップ信号を出力する過電圧比較器13と、前記誤差電圧に基づいてパルス幅を設定された最小値以上で変化させて前記DC−DCコンバータ動作を行うスイッチング素子を駆動するパルス駆動信号を生成し、当該パルス駆動信号のパルスを前記スキップ信号によってスキップするパルス幅変調信号生成回路18と、前記パルス駆動信号のパルス幅が最小値であることを検出するパルス幅検出部23と、前記パルス駆動信号のパルス幅が最小値であるときに、前記過電圧閾値を低下させる過電圧閾値制御部14とを備えている。

(もっと読む)

電圧変換装置

【課題】電源の電圧が変動する場合であっても、電圧指令の指示する電圧値と実際の出力電圧との誤差を無くして出力電圧の精度を向上させた電圧変換装置を提供する

【解決手段】電圧指令Vrefの指示する指示電圧値(=電圧指令Vrefの電圧値)となるようにバッテリから印加される直流の電源電圧VBを直流の出力電圧Voutに変換するにあたり、スイッチング素子SWの開閉動作によって電源電圧VBを、単位時間に占めるスイッチング素子のオン時間の割合であるデューティー比と電源電圧VBとを乗じた大きさの出力電圧Voutに変換するゲート回路部と、バッテリの電源電圧値VBを取得可能に構成され、取得した電源電圧値VBに対する指示電圧値の比率{=電圧指令Vrefの電圧値/電源電圧値VB}と等しいデューティー比でスイッチング素子SWの開閉動作をPWMにより制御する制御手段2とを設けた。

(もっと読む)

直流電圧変換装置及びその制御方法

【課題】MOSFETをスイッチング素子として使用する直流電圧変換装置において、サーマルシャットダウン時に生じるラッチアップを防止する。

【解決手段】直流電圧変換装置1は、ハイサイドMOSFETQ1と、ローサイドMOSFETQ2と、直流電圧変換装置1の温度が閾値を超えたことを検出する検出部(12、14、15)と、ハイサイドMOSFETQ1及びローサイドMOSFETQ2をスイッチングする制御信号を生成する制御部10と、MOSFETQ1及びQ2をスイッチングする制御信号を停止することにより直流電圧変換装置1の出力を停止する場合のうち、直流電圧変換装置1の温度が閾値を超えたことに応答して直流電圧変換装置1の出力を停止する場合、ハイサイドMOSFETQ1をスイッチングする制御信号を停止した後の所定期間、ローサイドMOSFETQ2をオン状態に保持する保持部(11、16)を備える。

(もっと読む)

スイッチング電源装置

【課題】電流モード制御において、降圧/昇降圧切替時または昇圧/昇降圧切替時の出力電圧変動を低減することができるスイッチング電源装置を提供する。

【解決手段】切替回路部62は、補償値切替部40の切替信号SELに従って、補償値Vos分だけシフトさせるか否かを切り替える切替部64と、切替部64の切り替え結果を電流センス信号Vsensに加算することにより、電流センス信号Vsensを誤差増幅器出力信号Veに対して補償値Vos分だけ相対的にシフトさせる加算回路部65と、を備えている。これによると、降圧/昇降圧切替のタイミングもしくは昇圧/昇降圧切替のタイミングで、PWM指令算出部70が生成するPWM信号のデューティー比を瞬時に切り替えることができる。このため、降圧/昇降圧切替時もしくは昇圧/昇降圧切替時の出力電圧変動を低減することができる。

(もっと読む)

チップ電子部品、チップ電子部品の実装構造、及びスイッチング電源回路

【課題】部品数を増やすことなく、インピーダンスの制御を容易で且つ広範囲に行うことが可能なチップ電子部品を提供すること。

【解決手段】チップ電子部品EC1は、フェライト材料を含有する素体3と、素体3の表面に配置された第一端子電極11、第二端子電極13、第三端子電極15、及び第四端子電極17と、素体3内に配置され、第一端子電極11、第二端子電極13、第三端子電極15、及び第四端子電極17に電気的に接続された内部導体7と、を備えている。第一端子電極11と第二端子電極13との間の内部導体7を介した電流経路のインピーダンスと、第一端子電極11と第三端子電極15との間の内部導体7を介した電流経路のインピーダンスと、が異なる。

(もっと読む)

誤差増幅器及び誤差増幅器を用いたDC−DCコンバータ

【課題】仮想短絡特性を用いずに、DC−DCコンバータのLCフィルタによる位相遅れを補償可能な誤差増幅器を提供する。

【解決手段】本発明は、入力電圧と基準電圧との誤差電圧に応じた出力電流を出力する第1の電圧電流変換器と、前記第1の電圧電流変換器と接続された位相補償回路とを備える誤差増幅器であって、前記位相補償回路は、誘導性回路と、容量を有する第1の容量性回路とを直列接続した構成であり、前記誘導性回路は、+側入力端子と−側入力端子との電位差に応じた出力電流を出力する第2の電圧電流変換器と、容量及び抵抗で構成され、前記第2の電圧電流変換器の+側出力端子と−側出力端子との間に接続された第2の容量性回路と、前記第2の電圧電流変換器に接続され、前記第2の容量性回路の両端に発生する電圧を入力し、該電圧に応じた電流を出力端子と前記第1の容量性回路に供給する第3の電圧電流変換器とを含む誤差増幅器である。

(もっと読む)

電源装置及び情報処理装置並びに電源供給方法

【課題】スケーラビリティを持つ装置においても負荷変動によらず高い効率で負荷に電源を供給することができるようにすること。

【解決手段】入力された電圧を所定の電圧に変換して負荷2〜5に向けて出力するとともに互いに出力特性が異なる複数のスイッチング電源11、12と、複数のスイッチング電源11、12から負荷2〜5に向けて出力される出力電流値を検出する電流検出部23と、複数のスイッチング電源11、12のうちいずれか1つを選択して動作させる制御部24と、を備え、制御部24は、電流検出部23で検出された出力電流値を用いて、複数のスイッチング電源11、12のうち最も電力効率が良くなるスイッチング電源を選択して動作させる。

(もっと読む)

コンバータ制御装置、およびこのコンバータ制御装置を用いた系統連系インバータシステム

【課題】並列接続された各DC/DCコンバータの寿命を可及的に均一化させるコンバータ制御装置を提供する。

【解決手段】コンバータ制御装置8に、運転させるDC/DCコンバータの台数を決定する台数決定部83と、運転させるDC/DCコンバータの優先順位を決定する優先順位決定部86と、決定された運転台数と運転優先順位とに基づいて、運転させるDC/DCコンバータを決定する運転制御部87とを設けた。優先順位決定部86は、積算異常回数に1を加算した値を積算電力量に乗算した算出値を算出し、当該算出値が小さいほど優先順位が高くなるように決定するようにした。算出値が小さいほど優先的に運転されるので、各DC/DCコンバータの積算電力量が均一化され、何らかの問題が生じている可能性があるDC/DCコンバータの使用が制限される。これにより、各DC/DCコンバータの寿命が均一化される。

(もっと読む)

DC/DCコンバータならびにそれを用いた電源装置および電子機器

【課題】消費電力を低減し、かつ短時間で起動可能なDC/DCコンバータを提供する。

【解決手段】電源端子VCCには、第2出力キャパシタCo2に生ずる電圧VCCが入力される。ハイ電圧端子VHには、入力電圧VINが入力される。充電用トランジスタM2は、ハイ電圧端子VHと電源端子VCCの間に設けられ、ノーマリオンとなるようバイアスされたNチャンネルMOSFET(Metal Oxide Semiconductor Field Effect Transistor)である。電流制限回路40は、電源端子VCCの電圧VCCが所定の第1しきい値電圧VTH1より低い第1状態において、ハイ電圧端子VHから電源端子VCCへ流れる充電電流ICHGを制限し、電圧VCCが第2しきい値電圧VTH2より高い第2状態において、充電電流ICHGを実質的にゼロに低減する。

(もっと読む)

電力変換装置

【課題】電源と負荷との間で絶縁を確保しながら電力供給を行いつつ、負荷に高すぎる電圧が供給されることを防ぐことが可能な電力変換装置を得る。

【解決手段】電力変換装置101は、入力電圧を分圧して分圧電圧を生成する分圧回路11と、分圧電圧を第1の直流電圧に変換する昇圧回路12と、分圧電圧を第2の直流電圧に変換する昇圧回路13と、第1および第2の直流電圧を負荷202に供給する電力伝達用絶縁回路14とを備え、電力伝達用絶縁回路14は、キャパシタC5と、スイッチ素子Q3,Q4を含み第1の直流電圧をキャパシタC5に供給する入力スイッチ部21と、スイッチ素子Q5,Q6を含み第2の直流電圧をキャパシタC5に供給する入力スイッチ部22と、スイッチ素子Q7,Q8を含みキャパシタC5に蓄えられた電力を出力する出力スイッチ部23とを含む。

(もっと読む)

ストロボ充電制御回路及びその制御方法

【課題】充電完了時におけるコンデンサの電圧ばらつきを低減させる。

【解決手段】コンパレータ100は、Vb≧Vrefとなると“High”を出力する。変換トランス140が蓄積した磁気エネルギを二次側から放出し、二次側の出力電圧(分圧値Vb)がGNDレベル以下となると、コンパレータ104はフリップフロップ106に“High”を出力する。時間検出部107は、スイッチ素子124をOFFにしてから、フリップフロップ106が“High”を保持するまでの出力時間Toffを計時する。ロジック部120は、Toff>T1である場合は、Vb≧Vrefとなるまで(充電完了電圧を検出するまで)充電制御を継続する。しかしToff≦T1となった場合は、入力電流Ipの設定値を、Ipテーブルに従って1段階上げて、充電制御を継続する。

(もっと読む)

位相シフトコントローラ、位相シフトの方法、およびそれらを用いた発光装置、電子機器

【課題】簡易に位相シフトバースト調光を実現可能な回路を提供する。

【解決手段】ポジティブエッジカウンタにより、調光パルス信号PWMのポジティブエッジを契機として初期値からカウントを開始する。ネガティブエッジカウンタにより、調光パルス信号のネガティブエッジを契機として初期値からカウントを開始する。第iチャンネル(2≦i≦n)において、調光パルス信号PWMの周期を示す周期カウント値CHLTCHR(CHLTCHF)を(i−1)/n倍することにより、そのチャンネルの位相シフト量SHFTRi(SHFTFi)を計算する。そしてカウント値CHCNTRが位相シフト量SHFTRiと一致すると、バースト制御信号PWMiを第1レベルに遷移させる。またカウント値CHCNTFが位相シフト量SHFTFiと一致すると、バースト制御信号PWMiを第2レベルに遷移させる。

(もっと読む)

DC/DCコンバータモジュール

【課題】放熱性及び耐振動性が向上されたDC/DCコンバータモジュールを提供する。

【解決手段】重心点を含む中心領域、及びその中心領域を挟んで互いに対向する第1及び第2部品領域が定義された搭載面を有するシャーシと、シャーシの中心領域上に配置されたトランスと、シャーシの第1及び第2部品領域上にそれぞれ配置された、コンバータ動作時の発熱量が大きい発熱部品とを備える。

(もっと読む)

スイッチング電源装置

【課題】同期整流回路を有し、出力短絡時等に負荷や内部の回路素子を確実に保護するシングルエンディッド・フォワード型のスイッチング電源装置を提供する。

【解決手段】MOS型FETの主スイッチング素子14及び転流側スイッチング素子24を備える。主スイッチング素子14のオン時間が短くなると、転流側スイッチング素子24をオフ状態に保持する同期整流駆動回路32を備える。出力電圧Voの誤差信号ΔVoに基づいてパルス幅変調すると共に、電流検出回路38のスイッチング電流信号が第1基準電圧Vr1に達すると駆動パルスV16をローレベルにするPWM制御回路16を備える。主スイッチング素子14のゲート・ソース端子間に可変抵抗素子46を備える。スイッチング電流信号が第2基準電圧Vr2に達すると、可変抵抗素子46の抵抗値を低下させ、主スイッチング素子14のゲート・ソース端子間電圧Vg14を抑える可変制御回路48を備える。

(もっと読む)

制御回路

【課題】スイッチング電源のクロスレギュレーション特性等を改善する制御回路を提供する。

【解決手段】電力補給部110が制御出力回路20からの電力供給を受け、電力補給部により非制御出力回路30に電力が補給的に供給され、電圧比較制御部120により、電力補給部と非制御出力回路との接続点の接続点電圧と非制御電圧とが比較され、接続点電圧が非制御電圧以上である場合に電力補給部と非制御出力回路とが導通させられ、接続点電圧が非制御電圧より小さい場合に電力補給部と非制御出力回路とが開放させられる。したがって、接続点電圧が非制御電圧以上になると、電力補給部と非制御出力回路とが導通させられて制御出力回路から非制御出力回路に電力を補給的に供給され、非制御出力回路の出力電圧低下が防止される。

(もっと読む)

161 - 180 / 3,623

[ Back to top ]