Fターム[5J055CX01]の内容

電子的スイッチ (55,123) | 用途(負荷、信号の種類) (3,195) | 高速スイッチング用 (27)

Fターム[5J055CX01]に分類される特許

1 - 20 / 27

高周波スイッチ

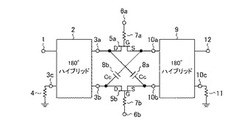

【課題】通過損失を低減するためにオン状態時の抵抗を小さくしても、十分なアイソレーション量を確保する高周波スイッチを得る。

【解決手段】トランジスタ5a,5bのオフ容量Coffと同一の容量Ccを有するクロスカップルキャパシタ8a,8bを設ける。

クロスカップルキャパシタ8a,8bにより、トランジスタ5a,5bのオフ容量Coffをキャンセルすることができるので、アイソレーションを大きく改善することができる。したがって、通過損失を低減するためにトランジスタ5a,5bのオン抵抗Ronを小さくしても、十分なアイソレーション量を確保することができる。

(もっと読む)

半導体スイッチ及び無線機器

【課題】高周波特性を改善した半導体スイッチ及び無線機器を提供する。

【解決手段】電源回路と、駆動回路と、スイッチ部と、第1の電位制御回路と、を備えた半導体スイッチが供給される。前記電源回路は、負の第1の電位を生成する第1の電位生成回路と、電源電位を降圧した正の第2の電位を生成する第2の電位生成回路と、を有する。前記駆動回路は、前記第1の電位と第3の電位とが供給され、端子切替信号に基づいて前記第1の電位及び前記第3の電位の少なくとも一方を出力する。前記スイッチ部は、前記駆動回路の出力に応じて複数の高周波端子のいずれか1つに共通端子を接続する。前記第1の電位制御回路は、第1のトランジスタを有する分割回路と、第2のトランジスタを有する増幅回路と、を有する。

(もっと読む)

スイッチング回路

【課題】ゲート電流を抑制し且つ高速動作が可能なスイッチング回路を提供する。

【解決手段】窒化物半導体層の主面上に互いに離間して配置された第1及び第2の主電極、及び前記第1の主電極と前記第2の主電極間で前記主面上に配置された制御電極を有するスイッチング素子TSWと、コレクタ端子とエミッタ端子と制御端子とを有する第1の駆動素子TD1及び入力端子を含む駆動回路10と、を備え、前記第1の駆動素子の前記コレクタ端子は前記スイッチング素子の前記第1の主電極に接続され、前記第1の駆動素子の前記エミッタ端子は前記スイッチング素子の前記制御電極に接続され、前記第1の駆動素子の前記制御端子は前記入力端子及び前記エミッタ端子に接続される。

(もっと読む)

駆動回路、駆動信号出力回路及びインクジェットヘッド

【課題】出力する駆動信号の遅延を小さくし且つ小型化した安価な駆動回路、駆動信号出力回路及びインクジェットヘッドを実現することである。

【解決手段】駆動回路30は、負荷を駆動するプッシュ側のMOSFET32及びプル側のMOSFET33と、アノード、カソードがMOSFET32のゲート、ソースに接続されたツェナーダイオード38と、アノード、カソードがMOSFET33のソース、ゲートに接続されたツェナーダイオード39と、昇圧回路31の出力端とMOSFET32のゲートとに接続された抵抗36と、昇圧回路31の出力端とMOSFET33のゲートとに接続された抵抗37と、抵抗36、抵抗37に並列に接続されたスピードアップコンデンサ42,43と、を備える。MOSFET32,33のソースが高圧側、グランドに接続され、MOSFET32,33のドレインが互いに接続される。

(もっと読む)

グリッチフリークロック信号マルチプレクサ回路および動作の方法

【課題】クロックマルチプレクサを駆動する第1のクロック入力から第2のクロック入力への切換えにおいて起こるグリッチを低減する。

【解決手段】クロックマルチプレクサ116は、第1のクロック入力を受信し、クロック出力118を提供し、第1のクロック出力における低フェーズ入力レベルに応答してクロック出力における低フェーズ出力レベルを判定する。限定された期間、低フェーズ出力レベルは、第1のクロック入力信号のフェーズレベルに関わらず維持される。クロックマルチプレクサ116は、第2のクロック入力を受信し、第2のクロック入力信号における低フェーズ入力レベルを判定する。第2のクロック入力に応答してクロック出力118を提供することへの切換えは、第2のクロック入力信号における低フェーズ入力レベルの間に起こる。その後、クロックマルチプレクサ116の出力は第2のクロック信号のフェーズレベルに従う。

(もっと読む)

窒化物半導体装置

【課題】駆動回路への要求を緩和した使いやすい高速動作の窒化物半導体装置を提供する。

【解決手段】実施形態によれば、窒化物半導体を含む、nチャンネル型の第1〜第4トランジスタと、抵抗と、を備えた窒化物半導体装置が提供される。第1トランジスタは、第1ゲートと、第1ソースと、第1ドレインと、を有する。第2トランジスタは、第2ゲートと、第1ゲートと接続された第2ソースと、第2ドレインと、を有する。第3トランジスタは、第3ゲートと、第1ソースと接続された第3ソースと、第1ゲート及び第2ソースと接続された第3ドレインと、を有する。第4トランジスタは、第3ゲートと接続された第4ゲートと、第1ソース及び第3ソースと接続された第4ソースと、第2ゲートと接続された第4ドレインと、を有する。抵抗の一端は第2ドレインと接続され、他端は第2ゲート及び第4ドレインと接続される。

(もっと読む)

スイッチング回路

【課題】電力効率を低下させずに高速動作可能なスイッチング回路を提供する。

【解決手段】スイッチング回路は、入力電圧を第1の電圧に変換する第1のDC/DCコンバータB1と、制御信号に応じて第1の電圧を出力するか否か切り替える第1のスイッチ回路C1と、第1のスイッチ回路からの電圧の過渡特性を制御する第1の制御回路D1と、高圧側電源に一端が、出力端子に他端が接続され、第1の制御回路からの電圧に応じてオンオフされる第1の能動素子A1と、入力電圧を第2の電圧に変換する第2のDC/DCコンバータB2と、制御信号に応じて第1のスイッチ回路とは相補的に第2の電圧を出力するか否か切り替える第3のスイッチ回路C3と、第3のスイッチ回路からの電圧の過渡特性を制御する第2の制御回路D2と、出力端子に一端が、低圧側電源に他端が接続され、第2の制御回路からの電圧に応じてオンオフされる第2の能動素子A2とを備える。

(もっと読む)

出力バッファ回路

【課題】出力信号のデューティを保ちつつ消費電流の変化を低減する。

【解決手段】出力バッファ回路は、出力回路(300)と、第1入力回路(210)と、第2入力回路(220)と、第1クランプ回路(110)と、第2クランプ回路(120)とを具備する。出力回路(300)は、第1出力トランジスタ(P301)と第2出力トランジスタ(N301)とを備え、出力信号(VOUT)を出力する。第1クランプ回路(110)および第2クランプ回路(120)のそれぞれは、カスコード接続される第1導電型のトランジスタ(P111/P121)と、第2導電型のトランジスタ(N111/N121)とを備える。第1クランプ回路(110)は、所定の期間第1入力回路(210)の出力電圧(VA1)をクランプする。第2クランプ回路(120)は、所定の期間第2入力回路(220)の出力電圧(VA2)をクランプする。

(もっと読む)

サンプルホールド回路

【課題】インバータなどの遅延が無視できない高速動作時において、クロックフィールドスルーの影響を改善するのが困難

【解決手段】MOST4はソース端子に入力されるアナログ入力信号を矩形波パルスのサンプル信号によりオンオフしてサンプリングする。MOST5はMOST4のドレイン端子にソース端子およびドレイン端子が接続されサンプル信号の極性を反転した反転サンプル信号によりオンオフしてMOST4の寄生容量を補償する。論理回路10,11はサンプル信号と反転サンプル信号の位相差を検出して誤差信号を出力する。MOST6,7はMOST5のソース端子およびドレイン端子にソース端子およびドレイン端子が接続され、位相差を補償する。

(もっと読む)

ルックアップテーブル回路およびフィールドプログラマブルゲートアレイ

【課題】動作速度の速いルックアップテーブル回路およびフィールドプログラマブルゲートアレイを提供する。

【解決手段】ルックアップテーブル回路1は、入力信号に基づいて複数の抵抗変化型素子の中から一つの抵抗変化型素子を選択する抵抗変化回路2と、抵抗変化回路2の最大抵抗値と最小抵抗値との間の抵抗値を有する参照回路4と、抵抗変化回路2の他端にソースが接続された第1のnチャネルMOSFET6と、参照回路の他端にソースが接続された第2のnチャネルMOSFET8と、第1のnチャネルMOSFET6のドレインを通して抵抗変化回路2に電流を供給する第1の電流供給回路10と、第2のnチャネルMOSFET8のドレインを通して参照回路4に電流を供給する第2の電流供給回路12と、第1のnチャネルMOSFET6のドレイン電位と第2のnチャネルMOSFET8のドレイン電位を比較する比較器14と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】入出力端子と半導体スイッチとの間を接続する配線同士が交差する箇所が発生しても、端子間のアイソレーション特性を向上させつつ、サイズ及びコストを抑制可能な半導体装置を提供する。

【解決手段】半導体スイッチ回路(20)は、複数の入力端子(31,32)のうち任意の入力端子を配線層(51)又は再配線層(251)を介して複数の出力端子(41〜44)のうち任意の出力端子と接続させるように構成される。複数の入力端子及び複数の出力端子のうち、ある端子と半導体スイッチ回路との間を接続する配線と、他の端子と半導体スイッチ回路との間を接続する配線とが交差している箇所において、交差する配線のうち、一方の配線を配線層とし、他方の配線を再配線層とする。

(もっと読む)

ゲート駆動回路及びゲート駆動方法

【課題】トランジスタの駆動電力の損失を防ぎ且つスイッチング時間の高速化を図る。

【解決手段】接合型トランジスタ2の駆動に必要な基準駆動能力レベル電圧からなる基準波形Sg′及び駆動能力のより高い高駆動能力レベル電圧からなる重畳パルスSpを生成し、重畳パルスSpのパルス幅を、接合型トランジスタ2のスイッチング時間に、若しくはドレイン電位VDの遷移収束タイミングを表す閾値により設定する。基準波形Sg′と重畳パルスSpとを重畳しこれを、接合型トランジスタ2のゲート駆動信号Sgとする。ゲート駆動信号Sgは、接合型トランジスタ2の遷移終了とみなすことの可能なタイミングで基準駆動能力レベル電圧に切り換わることになるため、遷移終了後も高駆動能力レベル電圧で駆動されることにより、接合型トランジスタ2に形成されるダイオードに順方向電流が流れることに伴う電力損失の発生を回避することができる。

(もっと読む)

電流源回路

【課題】矩形波の信号入力に応じて出力する出力電流の波形を矩形波に近づけることが可能な電流源回路を提供する。

【解決手段】電流源回路は、電圧端子に一端が接続された第1のMOSトランジスタと、第1のMOSトランジスタの他端に一端が接続され、出力端子に他端が接続された第2のMOSトランジスタと、電圧端子に一端が接続された第3のMOSトランジスタと、第3のMOSトランジスタの他端に一端が接続され、出力端子に他端が接続された第4のMOSトランジスタと、を備える。この電流源回路は、第1のMOSトランジスタおよび第4のMOSトランジスタに電流が流れるように第1の入力端子にバイアス電圧が印加された状態で、第2の入力端子に印加されるスイッチ電圧に応じて、第2のMOSトランジスタおよび第3のMOSトランジスタのオン/オフを同期して制御する。

(もっと読む)

半導体電力変換装置

【課題】スイッチング素子のオンオフ切り替え時において、スイッチング素子のゲートに供給されるゲート電圧の変化を監視し、最適なタイミングで段階的にゲート電圧を切り替えることによって、スイッチング素子のオンオフ切り替え時における電圧・電流サージを発生させない半導体電力変換装置を提供する。

【解決手段】本発明の半導体電力変換装置は、スイッチング素子をオンオフさせる半導体電力変換装置であって、スイッチング素子に供給されるゲート電圧の変化を検出するゲート電圧変化検出手段と、入力される駆動信号に基づいて、スイッチング素子のゲートにゲート駆動電圧を出力するゲート駆動手段とを備え、ゲート駆動手段は、ゲート電圧変化検出手段によってゲート電圧の変化が検出されたタイミングで、ゲート駆動電圧を制御することを特徴とする。

(もっと読む)

多チャンネル高周波信号切替装置

【課題】多チャンネルの高周波信号切り替えを小規模の回路構成にて容易に実現できる多チャンネル高周波信号切替装置を提供する。

【解決手段】多チャンネルの高周波信号を扱う切替回路を、四辺形のマトリクス配線領域11を囲繞するように例えば8組の高周波信号切替スイッチ12A〜12Hを設け、各チャンネルに共通のマトリクス配線領域に集成して、多チャンネル集成型の高周波信号切替回路を構成した。

(もっと読む)

可変制御電圧を有するスイッチ

可変制御電圧を用いた、改善された信頼性及び性能を有するスイッチが説明される。典型的な設計において、装置は、スイッチ、ピーク電圧検出器、及び制御電圧生成器を含む。スイッチは、スタックされたトランジスタを用いて実装されうる。ピーク電圧検出器は、スイッチへ提供された入力信号のピーク電圧を検出する。典型的な設計において、制御電圧生成器は、検出されたピーク電圧に基づいて、スイッチをオフにするための可変制御電圧を生成する。別の典型的な設計において、制御電圧生成器は、検出されたピーク電圧に基づいて、スイッチをオンにするための可変制御電圧を生成する。また別の典型的な設計において、制御電圧生成器は、ピーク電圧が高閾値を上回った場合、スイッチをオンにして入力信号を減衰させるための制御電圧を生成する。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】電圧パルスで振動子を駆動する送信回路において、誤送信や波形オーバーシュートを改善するため出力がハイインピーダンス状態にならない回路構成を提供し、且つ複数チャネルを集積化した半導体集積回路装置を実現する。

【解決手段】最も絶対値の大きい正電圧VPP1及び負電圧VNN1が供給された従来のパルス発生回路部10と、2番目に絶対値が大きい正電圧VPP2が供給されたP型アナログスイッチタイプのパルス発生回路部20と、2番目に絶対値が大きい負電圧VNN2が供給されたN型アナログスイッチタイプのパルス発生回路部30と、接地電位が供給されたN型アナログスイッチタイプの接地レベルダンピング回路部40とを備える送信回路において、10、20、30、及び40がそれぞれ出力端子OUTに接続される。スイッチ制御信号S1〜S5によって10、20、30、及び40を各別にオンオフして超音波振動子50を駆動する。

(もっと読む)

ドライバ回路及びドライバIC

【課題】クロスポイントが50%からずれた電気波形を出力する際も、良好な出力波形を維持することができるドライバ回路を得る。

【解決手段】初段増幅段A1、2段目増幅段A2及び最終増幅段A3の3段の差動増幅段が直列に接続されている。初段増幅段A1及び2段目増幅段A2に、クロスポイント調整回路CP1,CP2がそれぞれ接続されている。クロスポイント調整回路CP1は、初段増幅段A1の正相と逆相のDCレベルの少なくとも一方を制御して、初段増幅段A1の出力信号のクロスポイントを調整する。また、クロスポイント調整回路CP2は、2段目増幅段A2の正相と逆相のDCレベルの少なくとも一方を制御して、2段目増幅段A2の出力信号のクロスポイントを調整する。

(もっと読む)

超伝導デマルチプレクサ回路用のシステム、方法、および装置

デマルチプレクサ回路用のスイッチングセルは超伝導入力信号経路、少なくとも2個の超伝導出力信号経路、および交差ノードと出力信号経路との各端部の間に配置されたトランスを含む。トランスを介して印加された磁束は信号が伝播する方向に影響を及ぼすことができる。スイッチングセルはまた、電源入力ノードを含んでいてもよい。スイッチングセルは、各種の構成、例えば2分木またはH木に配置されてもよい。超伝導インダクタラダー回路はデジタル/アナログ変換を実行することができる。個別スイッチングセルと共に磁束記憶構造を用いてもよい。ラッチング量子ビットを用いてもよい。カスケードエラーを減少または除去すべくスイッチングセルのバッファ段を用いてもよい。  (もっと読む)

(もっと読む)

電圧制御型トランジスタのゲートドライブ回路

【課題】安定した電圧で充電して当該充電電圧をターンオフ時に利用することができ、しかもターンオフ時にパルストランスの二次巻線側に設けたゲート放電用トランジスタを高速にオンすることができる電圧制御型トランジスタのゲートドライブ回路を提供する。

【解決手段】パルストランス10とMOSトランジスタ20とダイオード21とコンデンサ30とダイオード31とゲート放電用pnpトランジスタ40と抵抗41とを備え、一次巻線11に印加された電圧によって二次巻線12に発生する電圧をトランジスタ20およびダイオード21を介して電圧制御型トランジスタ50のゲートに印加するとともにダイオード31を介してコンデンサ30を充電し、一次巻線11に印加される電圧が印加されなくなることで二次巻線12に発生する逆電圧によりコンデンサ30、抵抗41、ダイオード21、トランジスタ20を介する電流が流れる。

(もっと読む)

1 - 20 / 27

[ Back to top ]