Fターム[5J055DX82]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 複数の素子で構成される主スイッチ (1,328) | 異種類の素子を組み合わせるもの (146)

Fターム[5J055DX82]に分類される特許

1 - 20 / 146

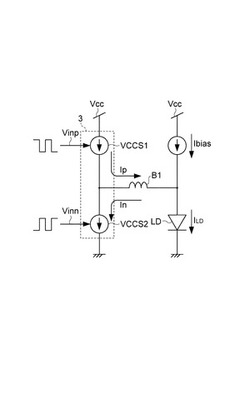

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子に接続されている逆相信号処理回路と、アノードが接続されている端子に接続されている第1及び第2の電圧制御電流源回路を備える。第1の電圧制御電流源回路には、正相信号Vinpに対応する電圧及び逆相信号Vinnの逆相に対応する電圧が入力され、第2の電圧制御電流源回路には、逆相信号Vinnに対応する電圧及び正相信号Vinpの逆相に対応する電圧が入力される。

(もっと読む)

ドライブ回路

【課題】トランスの補助巻線を用いることなく、制御回路の電源を確保して安価にできるドライブ回路を提供する。

【解決手段】ノーマリオン型のハイサイドスイッチQ1とノーマリオフ型のローサイドスイッチQ2との直列回路が直流電源に並列に接続され、ハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ回路であって、ハイサイドスイッチとローサイドスイッチとを制御信号によりオンオフさせる制御回路10と、ハイサイドスイッチとローサイドスイッチとの接続点に一端が接続された整流手段D2と、整流手段の他端と直流電源の一端とに接続され且つ制御回路に電源を供給するコンデンサC2と、制御回路からの制御信号とコンデンサからの電圧とに基づいてハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ部A1,AND1,Q3,Q4とを備える。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】NPNバイポーラトランジスタT11のエミッタは抵抗R11の一端に接続されるとともに接地レベルに接続され、コレクタは抵抗R12の一端及びコンデンサC12の一方電極に接続され、ベースは抵抗R11の他端及びコンデンサC11の一方電極に接続される。コンデンサC11の他方電極はLライン通信線10Lに接続される。PNPバイポーラトランジスタT12のエミッタは電源電圧V11を受け、コレクタはNMOSトランジスタQ11のゲートに接続される。NMOSトランジスタQ11のドレインはHライン通信線10Hに接続され、ソースがLライン通信線10Lに接続され、ゲートは抵抗R14を介して接地される。

(もっと読む)

半導体装置

【課題】出力信号を高速に変化させかつオーバーシュートやアンダーシュートを抑制できるようにする。

【解決手段】入力信号を反転して出力する主ドライバ11に加えて、補助ドライバ12を設け、入力信号の電圧変化に応じて出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、変化開始から主ドライバの出力信号がある電圧レベルを超えるまでの期間では信号変化を補助するように制御部15により補助ドライバの動作を制御し、主ドライバの出力信号がある電圧レベルを超えてから第2の電圧レベルになるまでの期間に信号変化を抑制するように制御部により補助ドライバの動作を制御するようにして、出力信号における信号変化の高速性を向上させ、かつオーバーシュートやアンダーシュートを抑制できるようにする。

(もっと読む)

半導体スイッチ及びスイッチ装置

【課題】電流変動が大きな箇所の半導体スイッチにおいて耐電流と損失を最適化する。

【解決手段】電気的特性及び種類が互いに異なるFET11とIGBT12を並列接続することで半導体スイッチ1aを形成する。端子5及び6間を接続するとき、FET11及びIGBT12は同時にオンされる。端子5及び6間の電流が小電流であるときには、FET11の内部抵抗がIGBT12よりも小さいため、FET11側に優先的に電流が流れて低損失が実現される。端子5及び6間の電流が増大するにつれて、FET11では発熱が内部抵抗増大を招くがIGBT12では内部抵抗が殆ど変化しないため、或る電流値以上では、IGBT12側に優先的に電流が流れる。結果、大電流がFET11側に流れることによるFET11の劣化又は破損が回避される。

(もっと読む)

半導体装置及びそれを備えた半導体リレー装置

【課題】半導体装置及び半導体リレー装置において、製造コストを抑えつつ、CR積の値を小さくする。

【解決手段】双方向スイッチ1を構成する2つのMOSFETのうち、一方のMOSFET2に、化合物半導体で構成されたユニポーラ型化合物半導体装置を用い、他方のMOSFET3に、シリコンで構成されたSi−MOSFETを用いる。ここで、ユニポーラ型化合物半導体装置の中には、Si−MOSFETよりもCR積の値が小さいものが多く存在する。従って、一方のMOSFET2にユニポーラ型化合物半導体装置を用いたことにより、両方のMOSFET2、3にSi−MOSFETを用いた場合に比べて、装置全体のCR積の値を小さくできる蓋然性が高まる。また、Si−MOSFETよりも製造コストの高いユニポーラ型化合物半導体装置を2つ用いた場合に比べて、製造コストを抑えられる。

(もっと読む)

半導体装置

【課題】周辺の回路構成を複雑にすることなく、繰り返しのデータの書き込みの際の劣化を低減することが可能な、不揮発性スイッチとして用いる半導体装置を提供する。

【解決手段】電源電圧が停止しても導通状態に関するデータの保持を、チャネル形成領域に酸化物半導体層を有する薄膜トランジスタに接続されたデータ保持部で行う構成とする。そしてデータ保持部は、ダーリントン接続された電界効果トランジスタ及びバイポーラトランジスタを有する電流増幅回路における、電界効果トランジスタのゲートに接続することでデータ保持部の電荷をリークすることなく、導通状態を制御する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】高耐圧回路の素子破壊を防止する際、半導体チップ面積の増大を軽減する。

【解決手段】半導体集積回路ICは、高電源電圧で動作する高耐圧回路100、200と低電源電圧で動作する低耐圧回路300、400を内蔵する。入力信号Aに応答して、高耐圧回路の第1素子5と第2素子3はオン状態とオフ状態に、低耐圧回路の第3素子7と第4素子8はオフ状態とオン状態に制御される。この状態において、高電源電圧供給端子に所定レベルのサージ電圧が供給される。この状態で、初期サージ電流が第1素子5と第2素子3の容量を介して低耐圧回路の出力端子Yに流入する。出力端子Yの電圧降下は、高耐圧回路の第2素子3のターンオン電圧に設定される。第2素子3はオフ状態からオン状態に制御されて、サージ電圧のエネルギーを吸収するサージ吸収電流が第1素子5と第2素子3に流入する。

(もっと読む)

半導体装置および電子機器

【課題】良好な逆回復特性と良好なEMCとを同時に実現することが出来て、かつ、従来の半導体装置よりも安価である半導体装置及び電子機器を提供する。

【解決手段】半導体装置1は、FET3のソースとMOSFET4のドレインとが接続されるとともに、一端が、FET3のゲートに接続され、他端が、MOSFET4のソースに接続される抵抗Rgsと、アノードが、FET3のゲートに接続され、カソードが、MOSFET4ソースに接続されるダイオードD1とを備える。

(もっと読む)

リセット回路

【課題】複数の電源電圧を駆動電圧とするSoC IC(System on a Chip Integrated Circuit)に対し、負荷変動やノイズに影響されること無く、複数の電源電圧の供給とリセット解除タイミングとのシーケンスを守ってリセットを行う。

【解決手段】供給ラインL1とリセット端子16との間においてエミッタを供給ラインL1に向けつつコレクタをリセット端子16に向けて介挿されたトランジスタTr1と、トランジスタTr1のベースとグランドとの間においてコレクタをトランジスタTr1のベースに向けつつエミッタをグランドに向けて介挿されたトランジスタTr2と、トランジスタTr1のコレクタとグランドとの間においてコレクタをトランジスタTr2のコレクタに向けつつエミッタをグランドに向けて介挿されたトランジスタTr3とを備える。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

パルス生成回路、パルス生成方法、走査回路、表示装置、及び、電子機器

【課題】自身の回路動作によって所望の遷移速度のパルス信号を生成可能なパルス生成回路、その生成方法、パルス生成回路を用いる走査回路、当該走査回路を用いる表示装置、及び、当該表示装置を有する電子機器を提供する。

【解決手段】2つの電源の間に直列に接続され、入力パルスの論理に応じて相補的にオン/オフ動作を行う2つのスイッチ素子を有し、パルス消滅時に所望の遷移速度のパルス信号を生成するパルス生成回路において、2つの電源のうち、入力パルスと同じ極性側の一方の電源を固定の電源電圧とし、他方の電源を複数の電源電圧間で切り換え可能とする。

(もっと読む)

出力回路

【課題】回路規模が増大する問題があった。

【解決手段】入力信号に応じて、出力端子に接続される負荷に出力電流を供給する出力回路であって、前記出力端子に出力電流を供給する出力トランジスタと、前記出力トランジスタを駆動する出力駆動回路と、前記出力電流を所定の電流値に制限する電流制御信号を生成する電流制限回路と、前記入力信号が供給された後、前記出力端子電圧が所定の電圧値以下の場合には前記電流制御信号に基づいて前記出力電流を制限し、前記所定の電圧値以上の場合には前記出力駆動回路によって前記出力トランジスタを駆動するように制御する制御回路と、を有する出力回路。

(もっと読む)

負荷駆動装置

【課題】スイッチング素子の立ち上がりの速度を高速に維持しつつ、スイッチング素子を駆動するドライバ回路の消費電流を削減することができる負荷駆動装置を提供する。

【解決手段】負荷10に接続されるスイッチング素子50と、定電流を生成する定電流生成部30と、定電流生成部30から流れ込む定電流の大きさに応じたオン時間でスイッチング素子50をオンするドライバ回路40と、を備えた構成とする。そして、定電流生成部30は、スイッチング素子50がオンするオン時間に達するまではドライバ回路40に第1電流量の大きさの定電流を流すことでスイッチング素子50の立ち上がりの速度を高速に維持する。また、定電流生成部30は、スイッチング素子50がオンするオン時間が経過した後はドライバ回路40に第1電流量よりも小さい第2電流量の定電流を流すことでドライバ回路40の消費電流を削減する。

(もっと読む)

負荷駆動装置

【課題】より高速駆動に対応でき、かつ、消費電流を低減することができる負荷駆動装置を提供する。

【解決手段】ダーリントン回路によってスイッチングデバイス2を駆動するようにし、ダーリントン回路を構成する第1PchMOSFET5と第2PchMOSFET6のドレインを共にスイッチングデバイス2を構成するIGBTのゲートに接続する。これにより、第2PchMOSFET6の駆動電流もIGBTの駆動に用いることができるため、消費電流を低減できると共に、より大電流でのIGBT駆動が可能になるため高速駆動を行うことができる。また、第2抵抗4と並列的にスイッチ10を備え、このスイッチ10をプルアップ駆動時にオンさせる。これにより、プルアップ駆動時に第1PchMOSFET5のゲート−ソース間の抵抗値を低下させることが可能となり、駆動スピードが低下することを抑制することが可能となる。

(もっと読む)

半導体装置、およびそれを用いた超音波診断装置

【課題】良好な線形性を有し、かつ電力損失の少ない双方向アナログスイッチの半導体装置を提供する。また、検出精度の高い超音波診断装置を提供する。

【解決手段】双方向にオンまたはオフ可能なスイッチ回路と、前記スイッチ回路の駆動回路を内蔵した双方向アナログスイッチの半導体装置であって、前記駆動回路は第一および第二の電源に接続され、前記第一の電源電圧は、前記スイッチ回路の入出力端子に印加される信号の最大電圧値以上であり、前記第二の電源電圧は、前記スイッチ回路の入出力端子に印加される信号の最小電圧値以下であり、さらに前記駆動回路は前記第一の電源と前記スイッチ回路との間に、直列に接続されたツェナダイオードとP型MOSFETを備えている。また、超音波診断装置であって、前記半導体装置を備える。

(もっと読む)

電磁石制御装置

【課題】簡素な構成の信号処理部で、複雑な波形の電流信号を発生させ、ドライバーを介して該電流信号に応じた波形の電流を各電磁石の励磁コイルに通電できる電磁石制御装置を提供すること。

【解決手段】複数の電磁石10を備え、各電磁石10の励磁コイルXに所定波形の励磁電流を通電することにより、隔壁で仕切られた空間内に発生したプラズマ分布を能動的に制御する電磁石制御装置であって、所定波形の励磁電流信号を生成する信号処理部13と、該信号処理部13からの所定波形の励磁電流信号S2を増幅して各電磁石10の励磁コイルに通電するドライバー11と、当該電磁石装置の各部に電力を供給する電源部17とを備えた電磁石制御装置。

(もっと読む)

出力回路及び出力装置

【課題】出力端子をシンク型又はソース型に切換える場合に、基板を交換する必要がなく、また出力端子に誤って電源を接続してもスイッチング素子の破損を防止することができる出力回路及び該出力回路を備える出力装置を提供する。

【解決手段】ディップスイッチ81にてソース型出力対応モードを選択した場合に、第2スイッチング素子32を常時オンにし、第1スイッチング素子31のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。ディップスイッチ81にてシンク型出力対応モードを選択した場合に、第1スイッチング素子31を常時オンにし、第2スイッチング素子32のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。またソース型出力対応モードを選択した状態で、第2出力端子32に誤って外部電源を接続した場合、第2スイッチング素子32に大電流が流れるが、直ちにヒューズ35が切断される。

(もっと読む)

保護装置、相補型保護装置、信号出力装置、ラッチアップ阻止方法、及びプログラム

【課題】保護対象のスイッチング素子のラッチアップを阻止することができる保護装置、相補型保護装置、信号出力装置及びプログラムを提供する。

【解決手段】PMOSトランジスタ106に対して過電流が流れていない状態でPMOSトランジスタ106を非導通状態にする場合、PMOSトランジスタ20A及びPMOSトランジスタ22の各々を導通状態とするように制御し、PMOSトランジスタ106に対して過電流が流れている状態でPMOSトランジスタ106を非道通状態にする場合、PMOSトランジスタ20Aを導通状態にすると共にPMOSトランジスタ22を非導通状態にするように制御する。

(もっと読む)

入力回路及び入力装置

【課題】入力端子をシンク型又はソース型に切換える場合に、基板を交換する必要がなく、また入力端子に誤って電源を接続してもスイッチング素子の破損を防止することができる入力回路及び該入力回路を備える入力装置を提供する。

【解決手段】ディップスイッチ70にてシンク型入力対応モードを選択した場合に、FET31をオフし、FET32をオンする。作業者が第2入力端子22に外部電源80を誤って接続した場合、FET32に大電流が流れる。定格電流よりも大きな電流がFET32に流れた場合、ヒューズ92は即時に切断される。そのためFET32の破損を防止することができる。またディップスイッチ70にてソース型入力対応モードを選択した場合に、FET31をオンし、FET32をオフするので、基板の交換を行うことなく、入力回路1をシンク型又はソース型に切換えることができる。

(もっと読む)

1 - 20 / 146

[ Back to top ]