Fターム[5J055GX04]の内容

Fターム[5J055GX04]に分類される特許

1 - 20 / 1,112

負荷駆動装置

信号切替回路およびA/D変換装置

電圧検出回路

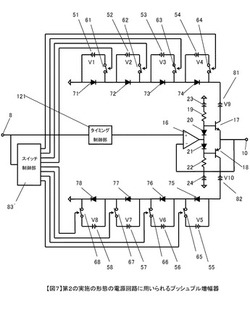

電源回路

【課題】 広帯域無線通信を行う送信機に用いられ、電源変換効率を向上させると共に、電圧レベル切替の遷移時間の影響を低減し、出力信号の歪特性を改善することができる電源回路を提供する。

【解決手段】 入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力するスイッチ制御部83′と、入力信号を特定の時間遅延させるタイミング制御部121を備え、スイッチ制御部83′が、制御信号の立ち上げの場合に、タイミング制御部121での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、立ち下げの場合には遅延時間のタイミングで立ち下げる電源回路としている。

(もっと読む)

パワー半導体素子の駆動回路

【課題】高速スイッチング性能を低下させることなく、パワー半導体素子のサージ耐量向上と過電圧保護を図る。

【解決手段】ドレイン端子1bから所定距離離間した位置にゲート制御端子5を備え、サージ発生時にドレイン端子1bとゲート制御端子5との間に放電が起こるようにする。この放電現象に伴ってゲート制御端子5にサージ電圧が印加されることで、パワー半導体素子1のゲートを充電し、パワー半導体素子1をオンさせることでサージエネルギーを吸収する。これにより、ドレイン端子1bに印加されるサージ電圧を抑制することが可能となり、パワー半導体素子1が破壊に至ることを抑制することが可能となる。

(もっと読む)

バッファ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路の入力電圧の振幅を増大させることが可能なバッファ回路を提供する。

【解決手段】第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、且つ、各入力端同士及び各出力端同士がそれぞれ共通に接続されており、第1,第2トランジスタ回路の少なくとも一方のトランジスタ回路がダブルゲートトランジスタから成るバッファ回路において、第1,第2トランジスタ回路の一方のトランジスタ回路が動作状態のとき、他方のトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

半導体スイッチ

【課題】半導体スイッチにおいて、エネルギー効率を高くする。

【解決手段】半導体スイッチ1は、LED2を駆動回路3により駆動して発光させ、LED2から発光された光を受光部4により受光する。駆動回路3は、バイポーラトランジスタ31と、コイル32と、ダイオード33等を有する。バイポーラトランジスタ31は、導通状態と非導通状態とに切換えられ、導通状態のときに、電源からLED2に電流が供給される状態にし、非導通状態のときに、電源からLED2に電流が供給されない状態にする。コイル32は、LED2に直列に接続されており、バイポーラトランジスタ31が導通状態から非導通状態になったときに、自己誘導作用によって誘導起電力を発生する。ダイオード33は、LED2及びコイル32に並列に接続されており、バイポーラトランジスタ31が非導通状態のときに、コイル32が発生する誘導起電力によって、LED2に電流を還流させる。

(もっと読む)

リセット信号生成回路及びそれを備えた半導体集積回路

【課題】電源投入後から外部リセット信号が最初にアクティブになるまでの期間にリセット信号をアクティブにすることが可能なリセット信号生成回路を提供すること。

【解決手段】本発明にかかるリセット信号生成回路101は、外部リセット信号が最初にアクティブになったことを検出する外部リセット検出回路102と、外部リセット検出回路102の検出結果が、外部リセット信号が最初にアクティブになる前であることを示す場合、外部リセット信号に関わらずリセット信号をアクティブにする制御回路と、を備える。

(もっと読む)

自動回復回路付き制御IC、制御ICの自動回復回路、パワ変換システム及び制御ICの自動回復方法

【課題】予備電源を備えなくても、制御ICが保護モードにて出力以外に自動復元の動作を行って、一定時間後自動に正常動作する。

【解決手段】システムまたは制御ICの異常状態を検出する異常状態検出部110と、異常状態の検出に応じて、保護モードに変更し、該保護モードにて自動回復信号を入力されて動作モードに変更するプロテクション部120と、入力電源からの電力の供給後、IC電源が予め決められた高電圧に到達すると、電力供給遮断信号に応じて入力電源からの電力の供給を遮断し、入力電源からの電力の供給及び遮断を繰り返すIC電源部130と、保護モードの開始に応じて、IC電源部130の電力供給信号及び電力供給遮断信号が交互に繰り返されるクロックをカウントし、該カウント数が予め決められた値に到達すると、プロテクション部120に自動回復信号を供給する自動再開部140とを含む。

(もっと読む)

制御装置

【課題】電源ユニットの出力ラインにおける地絡などの故障に対し、電源の保護及び故障の検知を行う。

【解決手段】サブ電源供給ラインLSに、サブ電源101側をソースとして第1MOSFET102を直列に接続し、第1MOSFET102のドレインにドレインを接続させて第2MOSFET103を直列に接続する。制御ユニット200内のサブ電源供給ラインLSにも、サブ電源101側をソースとして第3MOSFET202を直列に接続し、第3MOSFET202のドレインにドレインを接続させて第4MOSFET203を直列に接続し、第1〜第4MOSFETを制御することで、サブ電源101の電力を負荷201に対して供給する。各MOSFETのドレイン電圧、及び、第2MOSFET103と第3MOSFET202との間の電圧をモニタし、MOSFETの故障及びサブ電源供給ラインLSの故障を診断する。

(もっと読む)

電源切換装置

【課題】電圧変動の少ない電源切り換えを確実に行うことができる電源切換装置を提供する。

【解決手段】第2電源が接続される第2電源接続部、第2電源の電圧よりも高い電圧の第1電源が接続される第1電源接続部、負荷回路が接続される電源出力部、定電圧回路の出力端子と電源出力部とを接続するダイオード、第1電源接続部とダイオードとの間に挿入され第1電源の電圧を第2電源の電圧よりもダイオードの順方向電圧降下分高い電圧まで降圧する定電圧回路、第2電源接続部と電源出力部との接続をオン/オフするMOSスイッチと、第1電源接続部から電源が供給され、第2電源接続部または電源出力部の電圧と定電圧回路の出力電圧とを比較し、定電圧回路の出力電圧が第2電源接続部または電源出力部の電圧よりも高いとき、第1電源の電圧をMOSスイッチに導通することによってMOSスイッチをオフする比較回路と、を備える。

(もっと読む)

駆動回路

【課題】駆動電圧を調整可能な駆動回路を提供すること。

【解決手段】駆動回路10は、チャージポンプ回路部14を備えている。チャージポンプ回路部14は、メインスイッチング素子SW10がターンオンする遷移期間の初期段階において、キャパシタC1に充電された充電電圧に基づいて駆動電源18の電圧Vsを昇圧して駆動電圧Vgprを生成する。チャージポンプ回路部14では、指示信号S1に基づいてキャパシタC1に充電される充電電圧が調整可能に構成されている。

(もっと読む)

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

電界吸収型光変調器の駆動回路

【課題】電界吸収型光変調器に供給する駆動信号の直流電圧可変に伴う駆動信号波形の劣化を防止する。

【解決手段】電圧連動可変手段30は、ドライバ回路25の終段トランジスタTRの出力用の特定端子の直流電圧と他の端子の直流電圧とを、同一方向に連動可変させて、終段トランジスタTRの動作点の変動を抑制しつつ、電界吸収型光変調器1に与える駆動信号Dの直流電圧を変化させて、駆動信号Dの直流電圧可変に伴う駆動信号波形の劣化を防止し、波形劣化の無い変調光を出力させる。

(もっと読む)

ドライバ及びその使用方法

【課題】 簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えると共に、ユーザの使用態様の多様性に柔軟に対応できるようにする。

【解決手段】 デューティ比を変えることをもってして、パルスの立ち上がりのタイミングをずらす、すなわち、ドライバトランジスタのオンするタイミングをずらす。また、いくつかの出力端子を束ねる構成とする場合には、それらの出力端子に対応する各ドライバトランジスタについては、デューティ比を同じとすることをもってして、各ドライバトランジスタを同時オンさせて個々のオーバーロードを回避する。言い換えれば、出力端子を束ねない限りにおいては、デューティ比を変えてパルスの立ち上がりのタイミングをずらすことが得策となる。

(もっと読む)

ゲート駆動回路

【課題】逆導通IGBTに内蔵されたダイオードで発生するリカバリ電流を低減させる。

【解決手段】逆導通IGBTに内蔵されているダイオードに順方向電流が流れている間に、逆導通IGBTのゲート−エミッタ間にゲート閾値電圧よりも低い電圧を印加することで、逆導通IGBTのドリフト領域への正孔の注入を抑制し、リカバリ電流を低減させる。

(もっと読む)

低電圧検出回路

【課題】 電源電圧が所定の電位以上になって所定時間後に出力が解除状態になった後は定電流源の電流を流さないようにして消費電流を抑える遅延付き低電圧検出回路を実現する。

【解決手段】 電圧比較回路(13)により検出対象の電圧が所定の電圧値以下になったことを検出した場合には出力状態を直ちに変化させ、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には電流回路(14)により決まる遅延時間後に出力状態を変化させる低電圧検出回路において、電流回路は、電圧比較回路により検出対象の電圧が所定の電圧値以下になったことを検出した場合には、定電流源の電流を遮断する状態とし、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には、定電流源の電流を流す状態として電流回路によるコンデンサの充電を開始させ所定遅延時間後に定電流源に流れる電流を遮断するように構成した。

(もっと読む)

誘導性負荷駆動装置

【課題】電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現可能な誘導性負荷駆動装置を提供する。

【解決手段】第1のスイッチング素子と、第2のスイッチング素子と、還流回路と、逆起電流回生回路と、第2のスイッチング素子とアースとの間に介挿されたシャント抵抗とを備えた誘導性負荷駆動回路から誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、シャント抵抗の両端に接続された差動増幅器と、第1及び第2のスイッチング素子を制御するプロセッサと差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、プロセッサから第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチをオンにさせる遅延回路とを備える。

(もっと読む)

パワーオンリセット回路、固体撮像素子、およびカメラシステム

【課題】基準信号の精度を維持しつつスタンバイ時の電流低減を図ることが可能なパワーオンリセット回路、固体撮像素子、およびカメラシステムを提供する。

【解決手段】基準信号生成部は、少なくとも外部電源電圧検出器用基準信号を生成する第1の生成部と、記内部電源電圧検出器用基準信号を生成する第2の生成部と、を含み、第1の生成部は、電源起動時に外部電源電圧検出器用基準信号を生成可能となり、第2の生成部は、制御部からの起動信号を受けて内部電源電圧検出器用基準信号を生成可能となり、制御部は、スタンバイ期間が経過すると、起動信号を基準信号生成部の第2の生成部および内部電源電圧の生成系に出力する。

(もっと読む)

スイッチ制御装置

【課題】互いにオンオフ状態が反転するように制御すべき2つのスイッチング素子の特性に応じて容易にデッドタイムを調整可能なスイッチ制御装置を提供する。

【解決手段】互いにオンオフ状態が反転するように制御する第1及び第2のスイッチング素子を備えるスイッチ制御装置であって、前記第1及び第2のスイッチング素子の内、一方のスイッチング素子に出力する制御信号をオフレベルに切替えた時点から、コンデンサの容量で設定される設定期間後に他方のスイッチング素子に出力する制御信号をオンレベルに切替える信号を出力する制御信号生成回路を備える。

(もっと読む)

1 - 20 / 1,112

[ Back to top ]