Fターム[5K047LL02]の内容

デジタル伝送方式における同期 (12,489) | 通信制御 (259) | 速度変換 (147) | 非同期−同期信号変換 (27)

Fターム[5K047LL02]の下位に属するFターム

非連続−連続信号変換

Fターム[5K047LL02]に分類される特許

1 - 20 / 27

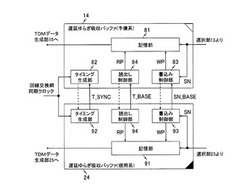

ゲートウェイ装置

【課題】現用系と予備系の各々のTDMデータの内容及びその出力タイミングを簡単に一致させることができるゲートウェイ装置を提供する。

【解決手段】

中継部の各々は、系切り替え手段による指定に関らず、IP網から到来したパケットを一時的に記憶する記憶部を含み、当該系切り替え手段によって現用系中継部として指定されたときは、先頭パケットに含まれるシーケンス番号を先頭シーケンス番号として予備系中継部に供給するとともに、当該先頭パケットを受信した時刻に所定遅延時間を加算して得られた読出し開始時刻を当該予備系中継部に供給し、当該系切り替え手段によって予備系中継部として指定されたときは、当該先頭シーケンス番号以降のシーケンス番号のパケットのみを当該記憶部に記憶し、且つ当該読出し開始時刻が到来してから当該記憶部に記憶されているパケットの読出しを開始する。

(もっと読む)

非同期吸収回路、画像処理装置及びプログラム

【課題】画像1ライン分よりも少ない記憶容量の複数のシングルポートメモリを用いて非同期吸収を行うことができる非同期吸収回路、画像処理装置及びプログラムを提供することを課題とする。

【解決手段】少なくとも画像1ライン分よりも少ない記憶容量の複数の記憶手段への入力データの書き込み動作を行う書き込み動作手段と、記憶手段からの出力データの読み出し動作を行う読み出し動作手段と、書き込み及び読み出しの対象となる記憶手段を切り替える切り替え手段と、画像1ライン分の入力データを複数に分けたブロックデータが記憶手段に振り分けられるタイミングに基づき、切り替え手段による記憶手段の切り替えを制御する切り替え制御手段と、入力データのクロック信号と出力データのクロック信号との非同期吸収を行う非同期吸収手段とを有することにより上記課題を解決する。

(もっと読む)

データ転送システムおよびデータ転送方法

【課題】システム性能を低下させることなくマスタから周辺回路へデータを転送することが可能なデータ転送システムを提供することである。

【解決手段】本発明にかかるデータ転送システムは、マスタM1〜M3と、マスタから第1のバス2を介して出力された複数のデータD1〜D3を入力し第2のバス4を介して当該データを出力するバスブリッジ3と、バスブリッジ3から出力されたデータD1〜D3を保持するライトバッファWB1〜WB3および当該ライトバッファWB1〜WB3から出力されたデータD1〜D3を保持するレジスタR1〜R3を備える周辺回路5と、を備える。バスブリッジ3およびライトバッファは第1のクロックで動作し、レジスタは第1のクロックとは非同期の第2のクロックで動作し、ライトバッファとレジスタとを同期化することでライトバッファからレジスタへデータを転送する。

(もっと読む)

データ受信装置及びデータ送信装置

【課題】後段の誤動作を抑制するデータ受信装置及びデータ送信装置を提供する。

【解決手段】物理層回路とMAC層との間でデータが非同期転送される。データは1バイト単位で処理される。検出回路は変換モジュールが送信したデータの第1のパケットと第2のパケットとの間隔が規格最小値より短いことを検出する。第2のパケットは第1のパケットに続く。無効化回路は間隔が規格最小値より短いことが検出回路に検出された場合に第2のパケットの先頭から1バイトの自然数倍分のデータを無効化する。無効化は、間隔が規格最小値以上となるように行われる。

(もっと読む)

高圧インバータのセル通信制御装置およびセル通信制御方法

【課題】インバータを有するセルを複数備えた高圧インバータのセル通信制御装置において、MCUと各セル間の通信に必要とする光配線の本数を減らす。

【解決手段】 MCUの通信制御部50に、シリアル信号の送信開始タイミングから、入力ゲート指令信号の状態が変化するまでの時間を遅延時間として検出するゲート状態変化ラッチ回路55およびゲート遅延検出カウンタ56を設け、前記検出時における送信シリアル信号の、設定されたフレーム送信期間後に送信するシリアル信号の送信開始タイミングを、前記遅延時間分遅らせて更新するシリアル信号更新遅延減算カウンタ57およびシリアル信号更新開始信号出力回路58を設け、前記更新されたシリアル信号を、1本の光配線110を介して前記セルに送信するシリアル信号送信処理回路59を設け、前記セルに、前記送信されたシリアル信号から前記ゲート指令信号を再生する信号再生部100を設ける。

(もっと読む)

非同期インタフェース回路及び非同期データ転送方法

【課題】非同期回路間で、確実にデータ転送する。

【解決手段】NANDからは、転送データ数分のDQS22と、DQ21とが順次出力される。I/Oブロック10は、データ保持回路11を介して転送データをFIFO30に書き込む。FIFO30に書き込まれたデータは、データ転送先のクロック信号に同期して読み出され、マルチプレクサ42を介して転送先内部に取り込まれる。最終データは、データ保持回路11には保持されるが、FIFO30には転送されない。マルチプレクサ42は、データ保持回路11に直接接続する経路を用いて、データ保持回路11に保持される最終データをシステムクロックに同期して取得する。

(もっと読む)

信号処理装置および信号処理方法

【課題】 相互に異なる周期のクロック信号が与えられ、かつ相互に非同期で所定の処理を行う複数の処理部のリセットを、簡単な構成で、確実に行うことができる信号処理装置および信号処理方法を提供する。

【解決手段】 モジュール回路部14は、モジュールA,B,Cのうちのいずれかに対するリセット指令が与えられると、指令されたモジュールを指定する信号を含み、かつCPUCLKの1周期分の長さを有する1shotリセット信号を生成する。同期リセット生成回路部15は、1shotリセット信号が与えられ、この1shotリセット信号の長さを指令されたモジュールに対応する長さに引き延ばした伸長リセット信号を生成し、生成した伸長リセット信号を指令されたモジュールのクロックに同期させて同期リセット信号を生成し、指定されたモジュールでは、同期リセット信号が与えられた状態で、クロック信号が立上がりまたは立下ると、リセットされる。

(もっと読む)

非同期型における送受信装置間の同期方法及び送受信装置

【課題】送信装置側と受信装置側にそれぞれ発振回路を有している非同期型の送受信装置の場合でも、送信装置側からのデータパルス信号に対して受信装置側のクロックパルスの位相が進んだり、遅れたりした場合でも、誤動作せずにデータパルス信号を正確に受信できるようにすること。

【解決手段】データパルス信号列の各パルスの周期と発振器27の周期とを同一にすると共に、データパルス信号列の各パルスと発振器27から出力されるクロックパルスのデューティ比をそれぞれ50%に設定する。クロックパルスCjと反転クロックパルス BarCjとで常時入力信号パルスの受信を監視し、クロックパルスCjあるいは BarCjのどちらで入力信号パルスを受信したかにより、Dフリップフロップ25での信号の取り込みのための同期信号としてのクロックパルスCjまたは BarCjを使い分ける。

(もっと読む)

シリアル通信装置

【課題】実時間通信が必要な同期通信パケットに遅延を発生させることなく、省配線化を実現する。

【解決手段】同期通信と非同期通信を識別可能なヘッダ情報を含む通信パケットと、自局より送信する同期通信パケットと他の周辺機器から入力される非同期通信パケットとの衝突の可能性を検出する手段(422、442)と、入力ポートに設けられた通信パケット待機用バッファ(424、444)と、同期通信パケットを受信した際は、同期通信パケットをそのまま出力し、非同期通信パケットを受信した際は、自局より送信する同期通信パケットとの衝突の発生が予想される場合、非同期通信パケットのバッファリングを行ない同期通信パケットを優先的に伝送する手段と、衝突の発生が無いと判断した場合、非同期通信パケットをそのまま出力する手段と、を備える。

(もっと読む)

転送性能最適化機能付非同期吸収回路

【課題】非同期吸収のための固定的なパルスの引き伸ばしでは、データ転送性能の劣化が起こる。

【解決手段】前段と後段のクロックドメインの動作周波数が用途に応じて様々な周波数に切り替わることが想定されるとき、複数の非同期吸収経路のうちのいずれかをセレクタ21で選択できるようにし、周波数比レジスタ30に設定された前段と後段のクロック周波数比の情報等をもとにしたセレクタ制御回路200の動作により、パルスの引き伸ばし等の非同期吸収で必要となる周波数依存の処理について最適な非同期吸収経路を選択する。

(もっと読む)

通信装置およびソースクロック再生方法

【課題】受信データに欠損がある場合にもクロック同期を確立することができるクロック再生装置を得ることを得ること。

【解決手段】送信側装置のソースクロックに基づいて送信されたデータを受信する通信装置であって、受信データに含まれるシーケンス番号に基づいてデータの欠損を検出し、検出した場合にはシーケンス番号に基づいて欠損したデータの個数を推定し、推定した個数分のダミーデータの生成を指示するシーケンス番号監視部20と、指示に基づいてダミーデータを生成するダミーフレーム生成部22と、ダミーデータと受信データをバッファリングするクロック再生バッファの残量に基づいてソースクロックを再生するソースクロック再生部23と、を備える。

(もっと読む)

データ変換回路

【課題】送信速度の設定及びデュアルポートRAMから取出すデータ量の設定が可能で、かつ送信データのエラーチェックが可能なデータ変換回路を提供する。

【解決手段】電源投入時に通信速度設定部41、RAM領域設定部42、パリティ設定部43にデータを設定する。通信速度設定部41はクロックセレクタ52で選択するクロックを指定し、デュアルポートRAM51の動作速度を決定する。RAM領域設定部42はアドレスカウンタ55の最大カウント値を決定し、デュアルポートRAM51から取出すデータ量を設定する。外部入力データをデュアルポートRAM51にポートAから書込み、ポートBから読出してデータ取込み用レジスタ56に取込み、データ分析部57で分析してパリティ処理部58でパリティビットを生成する。データ送信部59は、データ取込み用レジスタ56で取込んだデータにスタートビット、ストップビット、パリティビットを付加して出力する。

(もっと読む)

フレーム同期回路及び方法

【課題】バッファメモリの記憶容量を最小限で複数の系の入力データをフレーム同期させて出力するフレーム同期回路及び方法を提供する。

【解決手段】複数の系の入力データを複数のバッファメモリ12に、それぞれの系のフレーム同期信号を入力とするWRカウンタ11の制御下で書き込む。このWRカウンタ11の計数出力及びそれぞれのフレーム同期信号が入力されるパルス伸張部13で任意の位相調整長の伸張パルスを加算器14に入力して最大値を求め、この最大値と対応するフレームカウンタ15の計数値によりRD同期タイミング生成部17でRD同期タイミング信号を生成してRDカウンタ18を制御し、バッファメモリ12からフレーム同期した出力データを読み出す。

(もっと読む)

同期制御装置

【課題】バッファサイズを冗長化させることなく、非同期回路の動作を、基準となる回路の動作に同期させることが可能な同期制御装置を提供する。

【解決手段】第1の処理を実行し、当該第1の処理の完了時に第1の指示信号を出力する第1処理ブロックと、供給される電力に応じて処理速度を変更可能に動作するとともに、前記第1処理ブロックの処理に関係する第2の処理を実行し、当該第2の処理の完了時に第2の指示信号を出力する非同期回路の第2処理ブロックと、前記第1の指示信号と前記第2の指示信号との入力タイミングの時間差に応じて、前記第2処理ブロックに供給する電力値を決定する制御手段と、前記電力値に応じた電力を前記第2処理ブロックに供給する供給手段と、を備える。

(もっと読む)

非同期シリアル通信方法及び非同期シリアル通信装置

【課題】ある程度の高速性を得ながら、信号線数が少なく、回路規模を小さくする事の出来る非同期シリアル通信方法及び非同期シリアル通信装置を提供する。

【解決手段】送信側において、信号レベルを所定のレベルへ変化させた後、所定の第1時間T1の経過後から別に定めた第2時間T2以内に1ビットの送出データを送出するステップと、受信側において、信号レベルの変化を検出してから更に別に定めた第3時間T3(但し、T3>T1+T2)の経過後、または該第3時間T3の経過時点の何れかに、前記1ビットの送出データを取り込むステップとを含む。

(もっと読む)

直列データ受信回路

【課題】CPUの命令に従い、調歩同期方式で入力される制御コマンドを解析して通信速度と文字形式の識別を行い、受信動作以外では消費電力の低減を図る。

【解決手段】IF部23を介してCPUから開始命令を受けると、シーケンス制御部22はゲート部11を介してマスタークロック信号MCKを内部クロック信号ICKとして供給する。開始ビット測定部12は直列入力信号SINの第1文字の開始ビットの時間を測定し、通信速度選択部13と受信クロック発生部14は測定結果に従って受信クロック信号RCKを発生する。シーケンス制御部22の制御に従い、第1〜第3文字受信部15〜19で文字列を受信して特定の制御コマンドか否かを判定する。文字形式選択部21は受信した文字列に基づいて調歩同期方式の文字形式を選択する。CPUから停止命令を受けた時や、受信が完了した時にゲート部11を閉じて受信クロック信号RCKを停止する。

(もっと読む)

通信装置および通信方法

【課題】フレームを送受信する通信装置において、伝送路の利用率が高い場合でもクロック誤差が原因でバッファメモリが溢れることを防止する。

【解決手段】フレーム保持手段11は、送信待ちのフレームを保持する。送信手段13は、制御信号に基づいてフレーム保持手段11からフレームを順次取り出し伝送路4bへ出力する。送信制御手段14は、初期動作としてTクロック(T≧2)周期で制御信号を発信すると共に、N×Tクロック(N≧2)毎に待ちフレーム数を取得する。待ちフレーム数がK個(K≧1)の場合、少なくとも一部の発信間隔をTクロックより短くすることで、次のN×Tクロックの間にN+K回の制御信号を発信する。

(もっと読む)

非同期ネットワークのデータ伝送方法およびシステム

【課題】送信側で符号化レートが変更されても、受信側がレート変更に素早く追従できるようにした非同期ネットワークのデータ伝送システムを提供する。

【解決手段】同期化部202bのタイマ機能部にはパケット送出間隔計数値Δpnがセットされる。バッファ監視部205は、受信バッファ202aの書き込みアドレスADwと読み出しアドレスADrとの差分の変化を監視する。基準クロック調整部206は監視結果に基づいて基準クロックSref2を調整する。タイマ機能部は、基準クロックSref2’でセット値をダウンカウントし、カウント値が「0」になると受信バッファ202bへトリガ信号Tを出力して符号化データを転送させ、自身のカウント値をパケット送出間隔計数値Δpに再セットする。これ以後、調整後の基準クロックSref’がパケット送出間隔計数値Δpnだけカウントされるごとに受信バッファ202bへトリガ信号Tが出力される。

(もっと読む)

通信装置

【課題】 受信フレームタイミングを非同期クロックにより受け渡ししても、受信フレームタイミングのずれにのみ的確に追従できることを課題とする。

【解決手段】 受信FPの受信タイミングに対して送信FPの送信タイミングを追従させる通信装置であって、第1のクロック信号により動作し、受信FPの受信タイミングと第1の基準タイミングとの差分情報に基づき追従の方向と大きさを表す所定の追従情報を生成するフレームパルス受信部と、前記生成された追従情報を保持する追従情報保持部と、第2のクロック信号により動作し、第2の基準タイミングに従って送信するデータの基準となる送信FPを生成すると共に、前記追従情報保持部の追従情報に従って第2の基準タイミングを更新するフレームパルス送信部とを備える。

(もっと読む)

同期/非同期変換装置およびクロック制御方法

【課題】専用のクロック回線を設けることなく、SDH/SONET装置などの同期伝送装置をLAN網など非同期伝送網を介してエラーフリーで接続することが可能な同期/非同期変換装置およびクロック制御方法を提供する。

【解決手段】同期伝送網から受信したデータを前記非同期伝送網に出力する送信処理部と、前記非同期伝送網から受信したデータをバッファを介して前記同期伝送網に出力する受信処理部と、前記バッファ使用量の増減を監視するバッファ監視手段と、前記バッファ監視手段の出力に応じて前記バッファから読み出すクロックを可変するクロック制御手段とを設け、前記クロック制御手段は、前記バッファ使用量が増加する場合は前記バッファから読み出すクロックを速くし、前記バッファ使用量が減少する場合は前記バッファから読み出すクロックを遅くする。

(もっと読む)

1 - 20 / 27

[ Back to top ]