Fターム[5E346FF45]の内容

多層プリント配線板の製造 (97,916) | 導体層間接続の方法 (9,115) | 部品の実装によるもの (1,788)

Fターム[5E346FF45]に分類される特許

41 - 60 / 1,788

部品内蔵配線基板の製造方法

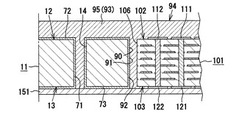

【課題】樹脂充填材とコア基板との密着性を改善することにより、信頼性に優れた部品内蔵配線基板を製造することが可能な部品内蔵配線基板の製造方法を提供すること。

【解決手段】コア基板準備工程ではコア基板11を準備し、収容穴部形成工程では収容穴部90をコア基板11に形成し、貫通穴部形成工程では貫通穴部14を形成する。めっき層形成工程では、収容穴部90の内壁面91に対してめっき層92を形成するとともに、貫通穴部14の内壁面に対して、空洞部を有するスルーホール導体となるめっき層71を形成する。収容工程では、部品101を収容穴部90に収容する。樹脂埋め工程では、収容穴部90の内壁面91と部品側面106との隙間、及び、空洞部に対して、樹脂充填材93を充填して埋める。

(もっと読む)

部品内蔵基板

【課題】マザー基板から伝わる応力を分散し、マザー基板との接続性に優れた部品内蔵基板を提供する。

【解決手段】本発明の部品内蔵基板20の樹脂層12は、コア基板6と固着している面とは反対側の面に凹部16が形成されている。マザー基板から部品内蔵基板20に応力が伝わった場合、樹脂層12に凹部16が形成されているため、部品内蔵基板20が撓みやすくなり、応力を分散させることが可能となる。その結果、マザー基板と接続している外部端子11に係る応力が小さくなり、マザー基板と部品内蔵基板20の接合性が向上する。

(もっと読む)

表面実装型受動素子部品、部品キャリアテープ、部品内蔵配線板

【課題】板厚み内部に位置させたとき部品端子からの導電路の配置密度を向上させること。

【解決手段】直方体状の素子部材と、素子部材の長手方向の一方向側の端部面である第1の端部面上に、および該第1の端部面に連なる素子部材の少なくとも上面上および下面上のそれぞれ一部に第1の端部面上と連なるように設けられた第1の端子電極と、素子部材の長手方向の他方向側の端部面である第2の端部面上に、および該第2の端部面に連なる素子部材の少なくとも上面上および下面上のそれぞれ一部に前記第2の端部面上と連なるように設けられた第2の端子電極と、を具備し、第1の端子電極および第2の端子電極が、いずれも、素子部材の上面上に設けられている面積の方が、素子部材の下面上に設けられている面積よりも広い。

(もっと読む)

貫通コンデンサ内蔵多層基板及び貫通コンデンサ内蔵多層基板の実装構造

【課題】貫通コンデンサの接続不良の発生を低減できる貫通コンデンサ内蔵多層基板及び貫通コンデンサ内蔵多層基板の実装構造を提供する。

【解決手段】貫通コンデンサ内蔵多層基板1では、基板11の内部に貫通コンデンサ21を配置することにより、ノイズ成分を貫通コンデンサ21の接地用端子電極24から接地導体層13に流して除去することができる。また、貫通コンデンサ内蔵多層基板1では、貫通コンデンサ21の接地用端子電極24に接続される接地プレーン14cが、貫通コンデンサ21の信号用端子電極23に接続される電源プレーン14a及び電源用配線14bと同一段の導体層として配置されている。これにより、貫通コンデンサ21と電源導体層14及び接地導体層13との接続が同一段で実現されるので、貫通コンデンサ21の寸法に多少のばらつきが生じたとしても接続不良の発生を低減できる。

(もっと読む)

電子部品素子搭載用基板及びその製造方法

【課題】材料コストが安く、しかもパッケージとした際に、薄型化が可能で、異物の発生を抑制可能な電子部品素子搭載用基板及びその製造方法を提供する。

【解決手段】基材14の一方の面が開放し他方の面が閉塞されて底部となる非貫通孔6と、この非貫通孔6の底部に設けられた電子部品素子搭載部12と、を有する配線基板2と、配線基板2の基材14の一方の面上に接着層4を介して配置され、電子部品素子搭載部12上に空隙部15を形成するスペーサ層3と、スペーサ層3上に接着層4を介して空隙部15を塞ぐように配置される蓋基板5と、を有する。

(もっと読む)

素子を内包したプリント基板の製造方法

【課題】積層プリント基板に素子を内包したプリント基板の製造方法において、Sn系合金半田を内層の実装に使用した信頼性の高い素子を内包したプリント基板の製造方法を提供。

【解決手段】素子実装面側に所望の表面実装用の素子をSn系合金半田を使用して表面実装し、実装基板の半田表面および素子の電極表面のSnをSnのエッチング液で選択エッチングすることにより、半田表面に、および電極表面を構成する他の金属のリッチ層およびこの金属表面に酸化膜28を形成するとともに、半田表面表面および電極表面に凹凸を形成する。

(もっと読む)

プリント回路基板及びその製造方法

【課題】積層される半導体チップの個数を増加させて高機能化を果たすとともに、薄板化の要求を満すことができるだけでなく、キャビティの内部下面を平坦化してキャビティに挿入される半導体チップを容易に整列できるようにする効果を有し、多数の半導体チップを同時に収容することができ、容易に高機能化を果たすことができるプリント回路基板及びその製造方法を提供する。

【解決手段】本発明の一実施例によるプリント回路基板100は、第1絶縁材110a及び第1絶縁材110a上に形成された第2絶縁材110bを含む絶縁層110と、絶縁層110の内層及び外層に形成された回路パターン120と、第1絶縁材110a又は第2絶縁材110bに複数個形成された半導体チップ挿入用キャビティ140と、を含む。

(もっと読む)

半導体パッケージ及びその製造方法

【課題】反りを低減可能な半導体パッケージ、及びその製造方法を提供する。

【解決手段】本半導体パッケージは、第1の半導体チップの回路形成面及び側面を封止する第1の封止絶縁層と、前記第1の封止絶縁層の前記回路形成面側の面である第1面に積層された配線層及び絶縁層と、前記絶縁層上に搭載された第2の半導体チップと、前記第2の半導体チップを封止するように前記絶縁層上に形成された第2の封止絶縁層と、を有する。

(もっと読む)

半導体パッケージ及びその製造方法

【課題】反りを低減可能な半導体パッケージ、及びその製造方法を提供する。

【解決手段】本半導体パッケージ10は、第1の半導体チップ20の回路形成面及び側面を封止する第1の封止絶縁層32と、第1の封止絶縁層32の前記回路形成面側の面である第1面に積層された配線層33、35、37及び絶縁層34、36と、第1の封止絶縁層32の前記第1面の反対面である第2面に搭載された第2の半導体チップ40と、第2の半導体チップ40を封止するように前記第2面に形成された第2の封止絶縁層49と、を有する。

(もっと読む)

多層基板

【課題】電子部品2を搭載する多層基板10における電子部品2と導電パターン121との間における接続信頼性の低下を抑制する。

【解決手段】熱可塑性樹脂をフィルム基材とする第2樹脂フィルム13、および熱硬化性樹脂をフィルム基材とし、片面に導電パターン121が形成された第1樹脂フィルム12を交互に積層した積層体10aと、電子部品2を搭載するベースフィルム11とを加熱プレスすることで形成される多層基板において、ベースフィルム11には、導電パターン121と電子部品2の電極端子2aとを接続するための端子接続用貫通穴111が形成され、積層体10aの積層方向から見たときに電子部品2と重合する部品搭載部位101は、端子接続用貫通穴111と重合しない非重合部位101bよりも、端子接続用貫通穴111と重合する重合部位101aに、積層方向における導電パターン121の数が多くなるように構成されている。

(もっと読む)

配線基板

【課題】絶縁基板とサーマルビアとの界面におけるクラックの抑制および発光素子で発生した熱の放熱性の向上。

【解決手段】配線基板20は、外部接続用電極層120、セラミックス層130および配線層140を備える。セラミックス層130は、アルミナとホウ珪酸ガラスを材料として形成されており、熱伝導率が6W/m・K以下である。セラミックス層130は、複数の第1のサーマルビア132、および、第1のサーマルビア132より小さい直径を有する第2のサーマルビア134を配置することにより、熱伝導率の低いセラミックス層130を用いた配線基板20において、発光素子150で生じる熱の放熱性能を向上している。第1のサーマルビア132は、発光素子搭載領域150a内に格子状に配置され、第2のサーマルビア134は、隣接する全ての第1のサーマルビア132から等距離離れた位置に配置されている。

(もっと読む)

印刷回路基板用積層板及び印刷回路基板の製造方法

【課題】本発明は、印刷回路基板用積層板及び印刷回路基板の製造方法を提供する。

【解決手段】本発明による印刷回路基板の製造方法は、半硬化状態の絶縁体の一面に電子素子を仮接するステップと、電子素子を加圧して絶縁体に電子素子が挿入された印刷回路基板用積層板を準備するステップと、印刷回路基板用積層板の表面に電子素子と電気的に接続される回路パターンを形成するステップと、を含むことを特徴とする。

(もっと読む)

プリント配線板

【課題】EMC特性の高い多層プリント配線板を提供する。

【解決手段】上述した課題は、コネクタと、コネクタと接続されたバイパスコンデンサと、コネクタが接続された第1のランドと、第1のランドとは異なる層に、第1のランドと対向する位置に配置され、かつ接地された第2のランドとを備えた多層プリント配線板等により解決される。

(もっと読む)

コンデンサ内蔵基板の製造方法

【課題】コンデンサ内蔵基板の製造方法において、絶縁基材上にコンデンサ素子を搭載する工程を簡略化する。

【解決手段】本発明に係るコンデンサ内蔵基板の製造方法は、貼着工程と、剥離工程と、積層工程とを有する。ここで、貼着工程では、外的な作用を与えることによりコンデンサ素子1の貼着と剥離とが可能なシート80を用いて、該シート80の表面の内、1又は複数の所定領域にコンデンサ素子1を貼着して添付することにより素子添付シート8を作製する。剥離工程では、絶縁基材20上の所定位置に、素子添付シート8を、該素子添付シート8に添付されているコンデンサ素子1を絶縁基材20に向けた姿勢で重ね合わせ、その状態で素子添付シート8に外的な作用を与えることにより、コンデンサ素子1をシート80から剥離して絶縁基材20上に搭載する。積層工程では、該絶縁基材20上に別の絶縁基材20を積層することにより絶縁基板を形成する。

(もっと読む)

半導体装置の製造方法およびその方法により製造された半導体装置

【課題】はんだの再リフローが不要となることにより製品設計またはプロセス設計などの自由度をより向上させ、かつ、余計な平坦化処理も不要とする。

【解決手段】配線基板1の導電性ペーストビアと、インターポーザ基板2の下面の電極22とが対応するように、インターポーザ基板2を配線基板1に対して位置決めし、その後、そのように位置決めされた配線基板1およびインターポーザ基板2を熱プレスにより積層する。このとき、導電性ペーストの硬化処理と、インターポーザ基板2の上面の電極22の平坦化処理が一緒に行われる。その後、インターポーザ基板2の上面の電極22と、ベアチップ3の微小バンプ31とが対応するように、ベアチップ3をインターポーザ基板2に対して位置決めし、フリップチップボンダ等で実装する。

(もっと読む)

電磁誘導機器

【課題】簡単な構造及び組立て作業性で、高温化を抑制したトランスを得る。

【解決手段】この発明に係るトランスは、ガラスエポキシ樹脂にコイルパターン10を内蔵したコイル基板3と、このコイル基板3に対面して設けられているとともにガラスエポキシ樹脂に放熱パターン11を内蔵した放熱基板6と、この放熱基板6を支持したベース8とを備え、コイルパターン10に流れる電流により発生した熱は、放熱パターン11を通じてベース8に流れるようになっている。

(もっと読む)

コンデンサ素子及びコンデンサ内蔵基板

【課題】コンデンサ内蔵基板に生じるインダクタンスを小さくすることが可能なコンデンサ素子、及び該コンデンサ素子を具えたコンデンサ内蔵基板を提供する。

【解決手段】本発明に係るコンデンサ素子は、第1電極層11と第2電極層12との間に誘電体層13が介在したコンデンサ素子1であって、第1電極層11は、第2電極層12側の表面111の一部が該第2電極層12によって覆われ、第1電極層11が金属箔により形成される一方、第2電極層12が金属薄膜又は金属箔により形成されている。本発明に係るコンデンサ内蔵基板は、前記コンデンサ素子1と絶縁基板2とを具え、該絶縁基板2内にコンデンサ素子1を埋設することにより絶縁基板2にコンデンサ素子1が内蔵されている。

(もっと読む)

チップインダクタ内蔵配線基板

【課題】チップインダクタ内蔵配線基板において、チップインダクタの漏れ磁束に起因したノイズとしての高周波電流の配線層への影響を低減し、配線基板に実装された他の回路部品や電子部品に対する電位変動や電源供給の変動を抑制して、これら回路部品及び電子部品の動作を良好に保持する。

【解決方法】相対向して配置される一対の第1の配線層及び第2の配線層と、前記第1の配線層及び前記第2の配線層間に配設されてなる絶縁層と、前記絶縁層内に配設されるとともに、前記第1の配線層に実装されてなるチップインダクタとを具え、前記第2の配線層は安定電位を供給する配線層であり、前記第2の配線層の前記チップインダクタと相対向する領域において非連続の複数の開口部が形成され、前記領域が前記非連続の複数の開口部によって画定されるようにして、チップインダクタ内蔵配線基板を構成する。

(もっと読む)

電子部品モジュールの製造方法

【課題】チップ側面にスルーホールを設ける場合において、樹脂等の絶縁体が充填されたとしてもマザーシートをチップ毎に分割することができる電子部品モジュールを提供する。

【解決手段】絶縁体31を塗布するより前に、スルーホール内に固体材料52を充填しておき、絶縁体31がスルーホール内に流れ込まないようにする。固体材料52は、ワックスや蝋材等の低融点材料(絶縁体31の硬化温度よりも低い100℃未満の融点を有するもの)である。そして、絶縁体31を熱硬化させると、固体材料52が溶出または揮発し、スルーホールは空洞となる。したがって、上記V字型のブレイク用溝55を外側に、矩形状のブレイク用溝51およびV字型のブレイク用溝57を内側にして曲げることでマザー積層体を各チップにブレイクすると、スルーホールの側壁に端面電極が露出し、分割後のいずれか一方のチップの側壁に絶縁体が付着している、ということはなくなる。

(もっと読む)

モジュールの製造方法

【課題】層間接続導体を形成する複数の接続端子が支持体に挿入されてなるる端子集合体を形成し、この端子集合体を配線基板に実装することで、層間接続導体を備えるモジュールを低コストかつ短い製造時間で製造できる技術を提供する。

【解決手段】層間接続導体を形成する柱状の接続端子11および電子部品102を配線基板101上に実装し、樹脂封止してなるモジュール100を製造する場合に、配線基板101の一方主面に、電子部品102を実装するとともに、複数の孔が形成された支持体12に接続端子11を挿入して成る端子集合体10を実装し(第1実装工程)、実装された電子部品102ならびに端子集合体10を樹脂層により封止する(第1封止工程)。こうすることにより、層間接続導体を有するモジュール100を低コストかつ短い時間で製造できる。

(もっと読む)

41 - 60 / 1,788

[ Back to top ]