Fターム[5F082BC12]の内容

Fターム[5F082BC12]に分類される特許

1 - 20 / 20

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置

【課題】電力破壊を抑制できる半導体装置を提供すること。

【解決手段】ベース領域12の表面に設定されたベースコンタクト領域14において、ベース電極15がベース領域12に接合されている。ベースコンタクト領域14の境界部の下方には、エミッタ領域13と同じ導電型を有するN型領域21がベースコンタクト領域14を包囲するように形成されている。言い換えれば、ベースコンタクト領域14の境界部の下方において、P型のベース領域12およびN型領域21によりPN型の寄生ダイオードが形成されている。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮する。

【解決手段】半導体装置1は、還流ダイオードDと、還流ダイオードDに対し並列に接続され、且つ、キャパシタCと抵抗Rを有する半導体スナバ2を備え、環流ダイオードDの遮断状態における静電容量に対するキャパシタCの静電容量の比が0.1以上になっている。このような構成によれば、振動現象の収束効果が高くなるように半導体スナバ2を構成するキャパシタCの静電容量が設定されているので、環流ダイオードDの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮することができる。

(もっと読む)

半導体装置

【課題】半導体基板内に縦型のスイッチング素子群が設けられている半導体装置において、スイッチング素子領域内の局所的な温度上昇を抑制する。

【解決手段】半導体装置100の半導体基板内に、縦型のスイッチング素子群が設けられているスイッチング素子領域50を備えている。スイッチング素子領域50は、第1領域51と第2領域52を有している。第1領域51には、バイポーラ構造の第1スイッチング素子群が設けられている。第2領域52には、ユニポーラ構造の第2スイッチング素子群が設けられている。第2スイッチング素子群は、第1スイッチング素子群の間に設けられている。

(もっと読む)

新構造半導体集積回路

【課題】現在、半導体集積回路で使用されているバイポーラトランジスタとMOSトランジスタは最初に発明された時よりその構造は変わっておりません。構造と原理を根本的に見直し、高速化・低消費電力化・微細化を進展させる。

【解決手段】サブミクロンスケールの微細加工技術を用い、新しい原理と構造のトランジスタによる半導体集積回路を形成する。

(もっと読む)

n型ベースを有するバイポーラトランジスタ及びその製造方法

【解決手段】ベースコンタクト接続部(12)、エミッタ部(4、5)及びコレクタ部がn層(3)上に配置され、当該n層は、更なるnpnバイポーラトランジスタために用いることができる。当該コレクタ部はエミッタ部に対して側方に配置され、当該エミッタ部及びコレクタ部の少なくとも一方は、当該n層の表面領域上でショットキーコンタクト(14)を備える。 (もっと読む)

パワー電界効果トランジスタ

寄生NPNなしでバルクシリコンからの電流フローを許容する、非常に短いチャネルを有するハイブリッドパワー電界効果トランジスタ(FET)装置。装置は、JFETコンポーネント、JFETコンポーネントに近接して配置された第1の蓄積型MOSFET、およびトレンチ端の底部のJFETコンポーネントに近接して配置された第2の蓄積型MOSFETまたはソースに接続する絶縁ゲートを有するMOSFETを含む。 (もっと読む)

複合半導体装置

【課題】同一の半導体層上に、半導体素子とセンサ素子とが形成され、半導体素子の温度が、高い応答速度でセンサ素子により検出される複合半導体装置を提供すること。

【解決手段】同一の半導体層上に、FRDとSBDとが並存するように形成した複合半導体装置は、

FRD11が、N型の第1半導体層1と、第1半導体層1上に島状に形成され、且つ、第1半導体層1とPN接合が形成されるP型の第2半導体層2と、第2半導体層2上に形成され第2半導体層2と電気的に接続される第1電極5と、で構成され、

SBD12が、第1半導体層1と、第1半導体層1上に形成され、且つ、第1半導体層1との間にショットキー接合が形成される第2電極6と、で構成され、

第2電極6、又は、第2電極6と接触する伝熱板が、平面的に見て第1電極5と重なるように延伸して形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】同一チップ内にショットキーバリアダイオードを備える半導体装置およびその製造技術において、信頼性を向上させる。

【解決手段】p型の半導体基板1の主面S1上に形成された、n型のnウェル領域w1nと、その中の一部に形成された、nウェル領域w1nよりも不純物濃度の高いn型カソード領域nCa1と、それを環状に囲むようにして形成されたp型ガードリング領域pgと、n型カソード領域nCa1とp型ガードリング領域pgとを一体的に覆い、かつ、それぞれに電気的に接続するようにして形成されたアノード導体膜EAと、p型ガードリング領域pgの外側に分離部2を隔てて形成されたn型カソード導通領域nCbと、これを覆い、かつ、電気的に接続するようにして形成されたカソード導体膜ECとを有し、アノード導体膜EAとn型カソード領域nCa1とはショットキー接続されていることを特徴とする。

(もっと読む)

半導体装置の品質評価方法および製造方法

【課題】最終製品での電気特性検査において半導体装置の歩留まりが低下するのを抑制することが可能な半導体装置の品質評価方法を提供する。

【解決手段】この半導体装置(安定化電源用IC)の品質評価方法は、n型エピタキシャル層13およびアノードショットキー電極層27からなるショットキーバリアダイオードの電気特性を測定する工程と、アノードショットキー電極層27と同時に形成され、半導体層(n+型エミッタ拡散層17、p+型ベース拡散層15b、n+型コレクタ補償拡散層18およびp+型ベース拡散層19a〜19d)にそれぞれオーミック接触されるオーミック電極層(エミッタオーミック電極層23、ベースオーミック電極層24、コレクタオーミック電極層25および抵抗オーミック電極層26a〜26d)の品質を、ショットキーバリアダイオードの電気特性により評価する工程とを備えている。

(もっと読む)

保護回路

【課題】安定動作可能な動作電圧の設定に自由度を与えることができる保護回路を提供する。

【解決手段】ドレイン端子と被保護素子2が接続された端子1を接続した電界効果トランジスタ3と、前記電界効果トランジスタ3のゲート端子と一端を接続し、他端を接地した抵抗4と、前記電界効果トランジスタ3のソース端子とアノード端子が接続され、カソード端子が接地された第1のダイオード5とで構成されていることを特徴とする保護回路6であり、入力端子に低電圧信号が印加された場合は前記トランジスタ3が遮断状態となり、高電圧パルスが印加されたときは導通状態となるようにバイアスされる。

(もっと読む)

ワイドバンドギャップデバイスのためのアバランシェ保護

本発明は、ワイドバンドギャップデバイスを電圧過渡の抑制の間の損傷から保護する方法及びデバイスである。アバランシェ耐量を向上させることは、ワイドバンドギャップデバイスのブロック接合部に1つ以上のダイオード又はPNPトランジスタを配置することにより達成される。  (もっと読む)

(もっと読む)

メサ型バイポーラトランジスタ

【課題】200℃以上の環境温度でも実用上十分な電流増幅率を確保できるバイポーラトランジスタ、わけても小型な電力用バイポーラトランジスタを提供する。

【解決手段】ベースのアクセプタ濃度勾配をコレクタ層端に比較してエミッタ層端で大きくした。また、エミッタ層およびベース層からなる第1のメサ構造と、ベース層およびコレクタ層からなる第2のメサ構造との距離(L2)を3μm以上9μm以下とした。さらに、ベース層を均一なアクセプタ濃度を有する第1のp型ベース層と、深さ方向に濃度傾斜を有する第2のp型ベース層から構成した。これらの手段により、電流増幅率を確保でき、小型化に適した高温対応電力用バイポーラトランジスタ。

(もっと読む)

定電流回路

【課題】定電流回路を構成するチップの面積縮小を図ることができる回路構成を提供する。

【解決手段】トランジスタ6のベース電流を流すための起動素子をツェナーダイオード7で構成する。そして、このツェナーダイオード7を構成する各拡散層20〜22をリーク電流が発生するような不純物濃度に設定する。このため、ツェナーダイオード7は、リーク電流分の電流を流し、かつ、ツェナーダイオード7の両端間に電位差(Vz×ツェナーダイオード7の個数)を発生させるため、抵抗と等価の役割を果たすことができる。このように、起動素子をツェナーダイオード7で構成することにより、起動素子を抵抗で構成する場合と比べて必要な面積を低減することが可能となる。したがって、定電流回路を構成するチップの面積縮小を図ることができる回路構成が可能となる。

(もっと読む)

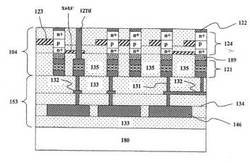

ダイオード内蔵パワースイッチングデバイスとその製造方法

【課題】フライホイールダイオードを内蔵したパワースイッチングデバイスにおける、高速スイッチング性向上と、安価に製造できるデバイス構造と製造方法。

【解決手段】下面にコレクタ電極を有するN+半導体層上面に形成したN-半導体層上面から厚み方向にP型領域を櫛状に形成し、該P型領域上面をエミッタ電極に接続したショトキー金属層に接合してなる、MPS構造体のダイオードをコレクタ・エミッタ間に造り込み、MPS構造のダイオードの逆回復時間が従来のPINダイオードの6分の1に短くすることが出来た。

(もっと読む)

化合物半導体装置

【課題】近接する2つの素子間に高濃度不純物領域を配置し、フローティング電位またはGND電位を印加することにより2つの素子間のアイソレーションを向上させる手法は、漏れた高周波信号のパワーが大きい場合に高濃度不純物領域の電位が変動してしまう。このため、結果として2つの素子間のアイソレーションが十分確保できなくなる問題があった。

【解決手段】近接する2つの素子間に伝導領域または金属層による分離素子を配置する。分離素子は高抵抗素子を接続し、直流端子パッドに接続する。また直流端子パッドから分離素子に至る接続経路は電位が高周波振動しない経路とする。これにより、少なくとも一方に高周波信号が伝搬する2つの素子の間に高周波GND電位を配置したこととなり、2つの素子間の高周波信号の漏れを防止できる。

(もっと読む)

マイクロ波モノリシック集積回路

【課題】HBTにおける高い耐電圧特性と優れた高速特性を維持した状態で、バラクタダイオードにおける広い容量可変幅を確保する。

【解決手段】1つの共通の半絶縁性基板1上に、HBT20とバラクタダイオード21とを形成したマイクロ波モノリシック集積回路において、HBTとバラクタダイオード21とに共通するコレクタ層を、コレクタコンタクト層4側に位置する第1のコレクタ層22a、22bと、反コレクタコンタクト層側に位置する第2のコレクタ層23a、23bとで構成し、さらに、第1のコレクタ層のキャリア濃度を第2のコレクタ層のキャリア濃度より高く設定している。そして、バラクタダイオード21においては、第2のコレクタ層23b上にショットキー電極24を形成する。

(もっと読む)

双方向フォトサイリスタチップ、光点弧カプラ、および、ソリッドステートリレー

【課題】転流特性の向上を図る。

【解決手段】 双方向フォトサイリスタチップ31の2つの動作チャンネルCH1,CH2が、交差しないように、互いに分離して配置されている。そして、N型シリコン基板上における左側のPゲート拡散領域23と右側のPゲート拡散領域23'との間であって、CH1とCH2との間に、リンがドープされた酸素ドープ半絶縁多結晶シリコン膜35aでなるチャネル分離領域29が形成されている。したがって、上記N型シリコン基板の表面におけるチャネル分離領域29近傍のシリコン界面準位(Qss)が増大し、N型シリコン基板内の少数キャリアである正孔が上記領域において消滅する。その結果、CH1がオフした時点でCH2側に逆位相の電圧が印加された場合に光入射が無いにも拘わらずCH2がオンする転流失敗を防止することができ、転流特性を向上できる。

(もっと読む)

静電保護回路およびそれを用いた半導体集積装置

【課題】 サージおよびラッチアップの両方に対して十分な保護電圧を有し、集積化するのに好適な構造を備えた静電保護回路およびそれを用いた半導体集積装置を提供する。

【解決手段】 アノードAが第1端子P1に接続され、カソードKが第2端子P2に接続されたサイリスタ11と、第1の順方向電圧VF1を有する第1整流素子D1と、第1の順方向電圧VF1と異なる第2の順方向電圧VF2を有する第2整流素子D2とが順方向に直列接続され、サイリスタ11の第2ゲートG2に第1整流素子D1のアノードA1が接続され、サイリスタ11のカソードKに第2整流素子D2のカソードK2が接続された整流回路12とを具備する。

第1および第2の順方向電圧VF1、VF2の組み合わせにより、サイリスタ11のターンオン電圧を微調整する。

(もっと読む)

保護素子およびそれを用いた半導体装置

【課題】マイクロ波FETでは、内在するショットキー接合容量またはpn接合容量が小さく、それらの接合が静電気に弱い。しかし、マイクロ波デバイスにおいては、保護ダイオードを接続することによる寄生容量の増加が、高周波特性の劣化を招き、その手法を取ることができなかったという問題があった。

【解決手段】pn接合、ショットキー接合、または容量を有する被保護素子の2端子間に第1n+型領域−絶縁領域−第2n+型領域からなる保護素子を並列に接続する。第1n+型領域および第2n+型領域のうち少なくとも一方は対向する先端部分の幅が非常に狭く、金属層が重畳してコンタクトしており、近接した第1、第2n+領域間で非常に大きな静電気を放電できるので、寄生容量をほとんど増やすことなくHEMTの動作領域に至る静電エネルギーを大幅に減衰させることができる。

(もっと読む)

1 - 20 / 20

[ Back to top ]