Fターム[5J055CX13]の内容

電子的スイッチ (55,123) | 用途(負荷、信号の種類) (3,195) | 負荷の性質 (266) | 誘導性 (219)

Fターム[5J055CX13]の下位に属するFターム

Fターム[5J055CX13]に分類される特許

1 - 20 / 198

誘導性負荷の駆動回路

スイッチング素子の駆動回路

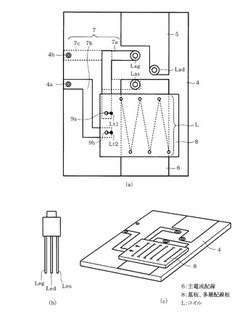

【課題】固定が容易で且つ設置スペースを削減できるようにしたスイッチング素子の駆動回路を提供する。

【解決手段】多層配線板8の下面が主電流経路6上に搭載する搭載面とされているため、その多層配線板8の搭載面を平坦面にすることができる。したがって、主電流配線6は、その上面が平坦な設置面として形成されていれば、単に多層配線板8の搭載面を主電流配線6の上面に配置することで設置できる。これにより、コイルLを容易に固定でき設置スペースを削減できる。

(もっと読む)

電磁機器駆動装置および電磁機器の駆動方法

【課題】電磁機器の累積使用量が多くなっても少ないと同じ一定時間で電磁機器を動作状態から停止状態に移行させる。

【解決手段】電磁機器駆動装置は、励磁用電源から電磁コイルへの通電が停止したときに逆起電力によって電磁コイルの両端間に生じる電圧をクランプするフリーホイール回路と、フリーホイール回路によってクランプされた電圧が、電磁機器の累積使用量が少ないときよりも多いときの方が高くなるように、フリーホイール回路の動作を制御するコントローラーと、を備える。

(もっと読む)

パワー半導体素子の駆動回路

【課題】高速スイッチング性能を低下させることなく、パワー半導体素子のサージ耐量向上と過電圧保護を図る。

【解決手段】ドレイン端子1bから所定距離離間した位置にゲート制御端子5を備え、サージ発生時にドレイン端子1bとゲート制御端子5との間に放電が起こるようにする。この放電現象に伴ってゲート制御端子5にサージ電圧が印加されることで、パワー半導体素子1のゲートを充電し、パワー半導体素子1をオンさせることでサージエネルギーを吸収する。これにより、ドレイン端子1bに印加されるサージ電圧を抑制することが可能となり、パワー半導体素子1が破壊に至ることを抑制することが可能となる。

(もっと読む)

半導体スイッチ

【課題】半導体スイッチにおいて、エネルギー効率を高くする。

【解決手段】半導体スイッチ1は、LED2を駆動回路3により駆動して発光させ、LED2から発光された光を受光部4により受光する。駆動回路3は、バイポーラトランジスタ31と、コイル32と、ダイオード33等を有する。バイポーラトランジスタ31は、導通状態と非導通状態とに切換えられ、導通状態のときに、電源からLED2に電流が供給される状態にし、非導通状態のときに、電源からLED2に電流が供給されない状態にする。コイル32は、LED2に直列に接続されており、バイポーラトランジスタ31が導通状態から非導通状態になったときに、自己誘導作用によって誘導起電力を発生する。ダイオード33は、LED2及びコイル32に並列に接続されており、バイポーラトランジスタ31が非導通状態のときに、コイル32が発生する誘導起電力によって、LED2に電流を還流させる。

(もっと読む)

スイッチ制御装置

【課題】互いにオンオフ状態が反転するように制御すべき2つのスイッチング素子の特性に応じて容易にデッドタイムを調整可能なスイッチ制御装置を提供する。

【解決手段】互いにオンオフ状態が反転するように制御する第1及び第2のスイッチング素子を備えるスイッチ制御装置であって、前記第1及び第2のスイッチング素子の内、一方のスイッチング素子に出力する制御信号をオフレベルに切替えた時点から、コンデンサの容量で設定される設定期間後に他方のスイッチング素子に出力する制御信号をオンレベルに切替える信号を出力する制御信号生成回路を備える。

(もっと読む)

ソレノイドの通電制御装置

【課題】ソレノイドに流れる電流を検出するタイミングと、PWM信号を出力するタイミングとのずれを抑制可能なソレノイドの通電制御装置を提供する。

【解決手段】ソレノイドの通電制御装置100は、ソレノイド50に流れる電流の電流値の取得用の電流取得用タイマ10と、当該電流取得用タイマ10の計数結果に基づいて、ソレノイド50の通電を制御するスイッチング素子51を駆動するPWM信号の1周期内において予め設定された回数だけ電流値を取得する電流値取得部11と、PWM信号の出力用のPWM制御用タイマ20と、1周期内に取得された電流値に基づき、次の1周期にスイッチング素子51に通電する通電時間を設定し、当該設定した通電時間に応じたPWM信号を出力するPWM制御部21と、PWM制御用タイマ20の計時結果に基づき、電流取得用タイマ10の計時値を更新する計時値更新部41と、を備える。

(もっと読む)

電流制御装置

【課題】電流制御装置をマイクロコントローラと電流制御用ICを用いて構成するとともに、多チャンネル化した際にも小型で低コストな電流制御装置を提供することにある。

【解決手段】電流制御装置は、電流制御用半導体素子1と、電流制御用半導体素子1に、負荷を駆動するためのPWMパルスを出力し、電流制御用半導体素子から、ハイサイド電流検出回路6とローサイド電流検出回路7の出力を入力するマイクロコントローラ12とを有する。電流制御用半導体素子1の出力合成回路8は、PWMパルスに同期して、1つの信号線上にハイサイド電流検出回路6の出力と、ローサイド電流検出回路7の出力を切り替えて、マイクロコントローラ12に出力する。

(もっと読む)

アクティブクランプ回路

【課題】アクティブクランプ動作期間を短縮するとともにESD耐量を向上させたアクティブクランプ回路を提供する。

【解決手段】実施形態によれば、第1のスイッチ素子と、第1のダイオードと、第1の抵抗と、第1および第2の制御回路と、を備えたことを特徴とするアクティブクランプ回路が提供される。前記第1のダイオードは、前記第1のスイッチ素子の両端にかかる過電圧によりブレークダウンする。前記第1の抵抗は、前記第1のダイオードの電流を検出する。前記第1の制御回路は、前記第1の抵抗の両端の電圧を増幅して前記第1のスイッチ素子の電流を制御する。前記第2の制御回路は、前記第1の抵抗の両端の電圧に応じて前記第1のスイッチ素子の導通を制御する。

(もっと読む)

電流制御用半導体素子およびそれを用いた制御装置

【課題】ゲインa、およびオフセットbの変動を動的に補正することで、1チップのIC内で高精度な電流検出が可能な電流制御用半導体素子、およびそれを用いた制御装置を提供することにある。

【解決手段】

同一半導体チップ上に、トランジスタ4と、電流−電圧変換回路22とADコンバータ23とを有する。参照電流生成回路6,6’は、負荷2の電流に電流パルスIcを重畳して、ADコンバータが出力する電圧デジタル値を変動させる。ゲインオフセット補正部8は、参照電流生成回路6,6’による電圧デジタル値の変動を信号処理して、ADコンバータ23が出力する電圧デジタル値と負荷の電流デジタル値の線形関係式におけるゲインa,a’及びオフセットb,b’を動的に取得する。電流デジタル値演算部12は、ゲインオフセット補正部8により取得されたゲイン及びオフセットを用いて、ADコンバータが出力する電圧値を補正する。

(もっと読む)

半導体装置

【課題】体格及びコストの増大が抑制された半導体装置を提供する。

【解決手段】直流電源とグランドとの間に直列接続された2つの単位回路と、単位回路を制御する制御部と、を備え、2つの単位回路の中点に誘導性負荷が接続された半導体装置であって、2つの単位回路それぞれは、第1スイッチ素子と、第1スイッチ素子と逆並列接続された還流ダイオードと、還流ダイオードと第1スイッチ素子それぞれと並列接続されたバイパス部と、を有し、バイパス部は、直列接続された第2スイッチ素子及び抵抗を有し、制御部は、2つの単位回路の第1スイッチ素子をOFF状態にするデッド期間を挟んで、2つの第1スイッチ素子を交互にON状態とし、デッド期間において、一方の第1スイッチ素子がOFF状態からON状態に移行するまで、一方の第1スイッチ素子と並列接続された第2スイッチ素子をON状態にする。

(もっと読む)

パワーMOSFETの駆動回路およびその素子値決定方法

【課題】パワーMOSFETを高速駆動する場合であっても、寄生インダクタンスに流れる電流の時間変化に応じて発生する電圧に起因したセルフターンオンの発生を防止できるようにしたパワーMOSFETの駆動回路、また、その素子値決定方法を提供する。

【解決手段】制御回路が、駆動回路によってスイッチを駆動制御することで、(2)区間においてスイッチS2HおよびS2Lをオンすると共にその他をオフとし、(3)区間においてスイッチS1LおよびS3Hをオンすると共にその他をオフとする。すると、(2)〜(3)区間にかけて、ハイサイド側のMOSFETのゲートソース間を所定のインピーダンスに切り替えることができ、リカバリー後半に至ったとしてもハイサイド側のMOSFETのゲートソース間電圧Vgs1を閾値電圧Vt未満に抑制できる。

(もっと読む)

負荷駆動回路

【課題】オン指令期間とオフ指令期間の両期間における電流を高精度に検出する。

【解決手段】制御装置13は、PWM駆動信号のオン指令期間において、電流検出回路14による検出電流と電源電圧検出回路15による検出電源電圧を電圧方程式に適用してオン期間電流経路の抵抗値とインダクタンス値を算出する。これらの値から還流経路12以外の経路の抵抗値とインダクタンス値を減算してオフ期間電流経路の抵抗値とインダクタンス値を求める。オフ指令期間において、オフ期間電流経路の抵抗値Rとインダクタンス値L、ダイオード7の順電圧Vfおよび前回の計算で求めた前回電流値を電圧方程式に適用し、リニアソレノイド2に流れる負荷電流を順次算出する。

(もっと読む)

スイッチング回路

【課題】整数倍の信号成分に起因して、負荷回路やスイッチング素子に余分な電流が流れない電力効率を向上したスイッチング回路を提供する。

【解決手段】スイッチング回路1は、第1端子50a及び第2端子50bを有しており、パルス信号により駆動されて第1端子及び第2端子の導通状態をスイッチするスイッチング素子10と、スイッチング素子の第1端子13に電圧を供給する電源部30と、電源部に並列に接続される負荷回路40と、電源部と負荷回路との接続点Pと、スイッチング素子の第1端子との間に接続され、パルス信号のクロック周波数のN倍(Nは1以上の整数)の周波数において、接続点からスイッチング素子へ流れる電流を抑制する受動回路部50と、受動回路部と接続点との間に接続され、N倍の周波数において共振する共振回路部60と、を備える。

(もっと読む)

スイッチング回路

【課題】大電流を制御可能なスイッチング回路において、部品点数を少なくしたコンパクトな構成にて、スイッチング損失を低減するとともにサージ電圧を抑制することができるスイッチング回路を提供する。

【解決手段】高電圧ラインL1と低電圧ラインL2との間においてMOSFET30,31,32,33が並列接続され、ゲート抵抗50,51,52,53の第1の端子がMOSFET30〜33のゲート電極に接続されている。MOSFET30,31,32,33毎に設けられたゲート抵抗50,51,52,53の第2の端子がゲート電圧印加ラインL3を介してパルス発生回路60と接続されている。パルス発生回路60により、ゲート抵抗50〜53を介してMOSFET30〜33のゲート電極にパルス状のゲート電圧が印加される。ゲート電圧印加ラインL3と高電圧ラインL1との間の1箇所にコンデンサ70が接続されている。

(もっと読む)

ゲート駆動回路

【課題】 リカバリー電流を低減させつつ、出力MOSトランジスタのスイッチング応答性を高くすることができるゲート駆動回路を提供する。

【解決手段】 制御信号Scdの信号レベルが所定の第1レベルLから第2レベルHへ遷移する第1遷移を契機として出力MOSトランジスタ2のゲートへ充電を開始する第1チャージ回路6と、制御信号Scdの第1遷移または第1期間Tp1の経過を契機として出力MOSトランジスタ2のゲートへの充電を開始する第2チャージ回路7と、制御信号Scdの第1遷移から第1期間Tp1より長い所定の第2期間Tp2経過後に出力MOSトランジスタ2のゲートへ充電を開始する第3チャージ回路8とを備え、第2チャージ回路7の単位時間あたりの充電量は、第1チャージ回路6および第3チャージ回路8の単位時間あたりの充電量より少ない。

(もっと読む)

スイッチング回路及び半導体モジュール

【課題】スイッチング制御する制御回路の負担を軽減するスイッチング回路を提供する。

【解決手段】第1のスイッチング素子の制御電極と第1のスイッチング素子をスイッチング制御する制御回路との間に接続される抵抗と、第1のスイッチング素子の制御電極と第1のスイッチング素子の低電位側電極との間に接続される第1のコンデンサと、第1のコンデンサと直列に接続される第2のスイッチング素子とを備え、第2のスイッチング素子の高電位側電極は、第1のスイッチング素子の制御電極に電気的に接続され、第2のスイッチング素子の低電位側電極は第1のスイッチング素子の低電位側電力端子に電気的に接続され、第2のスイッチング素子の制御電極は、抵抗と制御回路の間に接続されている。

(もっと読む)

ドライバ回路

【課題】 出力オフ時のスイッチング時間を短くすることのできるドライバ回路を提供する。

【解決手段】 実施形態のドライバ回路は、を駆動する出力用MOSトランジスタMV1が、電源端子VDDと誘導性負荷RLが接続される出力端子OUTとの間に接続され、抵抗R1が、出力用MOSトランジスタMV1のゲート端子とゲート電圧印加端子VGとの間に接続され、ゲート電圧印加端子VGに一端が接続された抵抗R2と、一端が抵抗R2の他端に接続され、他端が接地端子GNDに接続され、出力用MOSトランジスタMV1を制御する制御信号VSWにより導通が制御されるNMOSトランジスタMD1とを備える。さらに、このドライバ回路は、一端が抵抗R1の他端に接続され、他端が出力端子OUTに接続され、NMOSトランジスタMD1の一端から出力される信号により導通が制御されるPNPトランジスタQ1を備える。

(もっと読む)

誘導性負荷の駆動回路

【課題】スイッチング素子のオンオフによる誘導性負荷の電流応答性を良好なものとしながら駆動回路内の発熱をより抑制する。

【解決手段】誘導性負荷10を駆動する駆動回路20に、誘導性負荷10と並列接続され且つ互いに直列接続された第1の抵抗42および第2の抵抗44と、第2の抵抗44に並列接続されたコンデンサ46と、誘導性負荷10と並列接続されゲートが抵抗42と第2の抵抗44(コンデンサ46)との接続点に接続されドレインがグランドに接地されたNチャネル型のFET32と、FET32のソースと電源ライン24との間に介在しドレインからソースの方向を順方向とする第1のダイオード34とを設ける。

(もっと読む)

電源回路

【課題】 特殊なスイッチを用いず、手動による動作停止およびコントロール回路からの制御による動作停止が可能であり、無駄な電力消費が少ない電源回路を提供する。

【解決手段】 リレースイッチSW2がOFFの状態でスイッチSW1が押圧されると、交流電圧が給電線101および103間に与えられ、負荷400に対する直流電圧が立ち上がる。すると、コントロール回路210は、リレースイッチSW2をONさせる。このとき、充電回路110および120では、電解コンデンサC1およびC2の充電が行われるが、電解コンデンサC2の充電電流が小さいため、LED104は発光しない。リレースイッチSW2がONの状態で、スイッチSW1が押圧された場合、放電回路130が開くため、電解コンデンサC2が急速充電される。この場合、LED104が発光し、コントロール回路210は、リレースイッチSW2をOFFにする。

(もっと読む)

1 - 20 / 198

[ Back to top ]