Fターム[5F003BA92]の内容

バイポーラトランジスタ (11,930) | 素子構造 (1,262) | 空乏層制御構造 (403) | メサ、ベベル (349)

Fターム[5F003BA92]に分類される特許

81 - 100 / 349

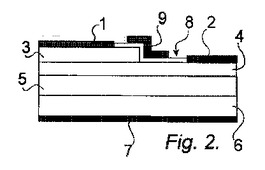

シリコンカーバイドバイポーラ接合トランジスタ

本発明は、シリコンカーバイド(SiC)バイポーラ接合トランジスタ(BJT)に関し、当該トランジスタ上のエミッタコンタクトとベースコンタクトと(1、2)の間の表面領域には、バルクSiC内の電位と比較して負の表面電位が与えられている。  (もっと読む)

(もっと読む)

半導体装置

【課題】高耐圧化及び高温動作を実現できる、HBTとFETを備える半導体装置を提供する。

【解決手段】本発明に係る半導体装置100は、基板101の上に順時積層されたn+型GaN層103及びn型GaN層104と、p型InGaN層105と、アンドープGaN層106及びn型AlGaN層107と、HBT領域121のn+型GaN層103と電気的に接続されたコレクタ電極114と、HBT領域121のp型InGaN層105と電気的に接続されたベース電極113と、HBT領域121のn型AlGaN層107と電気的に接続されたエミッタ電極112と、HFET領域120のn型AlGaN層107と電気的に接続されたソース電極109及びドレイン電極111と、n型AlGaN層107の上に形成されたゲート電極110とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】線形性に優れた半導体抵抗素子を提供する。

【解決手段】本発明の半導体装置は、GaAs基板101上に形成され、3−5族化合物半導体から構成されるHBT130と、GaAs基板101上に形成され、HBT130を構成する半導体エピタキシャル層の少なくとも1層から構成される半導体抵抗素子120とを備え、半導体抵抗素子120は、ヘリウム不純物を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】良好な電流増幅率が得られる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板と、半導体基板上に設けられ、炭化ケイ素から形成される第1導電型の第1伝導層12と、第1伝導層12上に設けられ、第1伝導層12の不純物濃度より低い不純物濃度を有し、炭化ケイ素から形成される第1導電型の第2伝導層14と、第2伝導層14中に設けられ、第1導電型とは異なる導電型の第2導電型のベース領域16と、ベース領域16中に設けられ、表面がベース領域16の表面と同一平面にあると共に、5×1017cm−3以上5×1019cm−3以下の不純物濃度を有する第1導電型のエミッタ領域18とを備える。

(もっと読む)

ヘテロ接合バイポーラトランジスタ及びその製造方法

【課題】耐破壊性に優れたヘテロ接合バイポーラトランジスタを提供する。

【解決手段】サブコレクタ層と、第1コレクタ層、第2コレクタ層、第3コレクタ層及び第4コレクタ層を有しサブコレクタ層上に形成されたコレクタ層と、コレクタ層上に形成されたベース層と、ベース層上に形成され、ベース層を構成する半導体よりも大きなバンドギャップを有する半導体から構成されるエミッタ層とを備え、第1コレクタ層は、第2コレクタ層、第3コレクタ層及び第4コレクタ層を構成する半導体と異なる半導体から構成されてサブコレクタ層上に形成され、第4コレクタ層は、第2コレクタ層の不純物濃度よりも低い不純物濃度で第1コレクタ層上に形成され、第2コレクタ層は、サブコレクタ層の不純物濃度よりも低く第3コレクタ層の不純物濃度よりも高い不純物濃度で第4コレクタ層上に形成され、第3コレクタ層は、第2コレクタ層とベース層との間に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッドの剥がれを防止し、かつボンディングパッド間におけるリーク電流の発生を防止することができる半導体装置及びその製造方法を提供すること。

【解決手段】HBT(ヘテロ構造バイポーラトランジスタ)が構成要素の1つとして集積された半導体装置110は、半絶縁性InP基板11上に、順次、エッチングストップ層12、コレクタコンタクト層13、コレクタ層14、傾斜コレクタ層15、セットバック層16、ベース層17が形成された構成を有し、ベース層17はInGaAsで構成された薄膜であってPを含まず、このベース層17上にSiN23が形成され、SiN23上にボンディングパッド25が形成された構成を有する。

(もっと読む)

発光並びにレーザ半導体素子および方法

半導体発光素子は、エミッタとコレクタ領域の間のベース領域を有するヘテロ結合バイポーラ発光トランジスタと、エミッタ、ベース、およびコレクタ領域それぞれで、結合電気信号ためのエミッタ、ベース、およびコレクタ電極と、前記ベース領域の中に量子サイズ領域とを備え、前記ベース領域は、前記量子サイズ領域のエミッタ側上に第1のベースサブ領域と、前記量子サイズ領域のコレクタ側上に第2のベースサブ領域を備え、前記第1と第2のベースサブ領域は非対称バンド構造を有する。2端子半導体構造から光放射を生み出すための方法は、第1の伝導型のエミッタ領域と、第1の伝導型の領域と反対に第2の伝導型のベース領域の間に第1の半導体接合、および前記ベース領域とドレイン領域との間に第2の半導体接合を含む半導体構造を提供するステップと、前記ベース領域の間に量子サイズ効果を示す領域を提供するステップと、前記エミッタ領域に結合されたエミッタ電極を提供するステップと、前記ベース領域と前記ドレイン領域に結合されたベース/ドレイン電極を提供するステップとを含み、前記半導体構造から光放射を得るため、前記エミッタおよび前記ベース/ドレイン電極に信号を印加する。 (もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板であっても加熱処理が可能となる、基板の熱処理方法を提供する。

【解決手段】熱処理される被熱処理部を備えるベース基板を熱処理して半導体基板を製造する方法であって、電磁波を吸収して熱を発生し、被熱処理部を選択的に加熱する被加熱部をベース基板上に設ける段階と、ベース基板に電磁波を照射する段階と、被加熱部が電磁波を吸収することにより発生する熱によって、被熱処理部の格子欠陥密度を低減する段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

縦型のバイポーラトランジスタとその製造方法

【課題】 ダイシングラインに沿って深部に至る深い不純物拡散領域を形成することによって必要な耐圧を確保する技術において、深い不純物拡散領域8を短時間の熱処理で製造可能な技術を提供する。

【解決手段】半導体基板4に不純物拡散領域を形成する際に、注入エネルギーを変えながら複数回に亘って不純物を注入する工程と、その後に半導体基板4を熱処理する工程を備えている。複数の深さL1〜L5に不純物を注入しておいてから熱処理をするので、深い不純物拡散領域8を短時間の熱処理で形成することができる。このバイポーラトランジスタ2の場合、複数の深さL1〜L5において不純物濃度のピークが観測される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の特性を向上できると共に、製造コストを低減できる。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1上に順次積層されたコレクタ層2A、ベース層3A及びエミッタ層4Aと、コレクタ層2Aの側面上に設けられ、コレクタ層に対して歪み応力を与える第1ストレスソース膜15Aと、ベース層3Aの側面上に設けられ、ベース層3Aに対して歪み応力を与える第2ストレスソース膜17と、を具備し、第1ストレスソース膜15A上端及び前記ベース層上端は、半導体基板表面から同じ高さに位置し、第2ストレスソース膜17は、ベース層3Aの側面と第1ストレスソース膜15Aの側面との間に設けられる。

(もっと読む)

過電圧保護素子

【課題】小型の過電圧保護素子を提供する。

【解決手段】サブコレクタ領域13にオーミックコンタクトを有する電極3と、サブコレクタ領域13上に形成され、第1導電性に対して反対の導電性である第2導電性を有するアノード領域4と、アノード領域4にオーミックコンタクトを有するアノード電極18と、アノード領域4と分離されて形成され、前記第2導電性を有するベースメサ領域5と、ベースメサ領域5上に形成され、前記第1導電性を有するエミッタメサ領域7と、エミッタメサ領域7と分離されて形成され、前記第1導電性を有するエミッタメサ領域8と、エミッタメサ領域8にオーミックコンタクトを有するエミッタ電極10と、エミッタメサ領域7にオーミックコンタクトを有するエミッタ電極9と、電極3とエミッタ電極10とを接続する配線16と、アノード電極18とエミッタ電極とを接続する配線17とを備え、配線16と配線17とを出力端子とする。

(もっと読む)

ショットキーバリア量子井戸共振型トンネルトランジスタ

【課題】ショットキーバリア量子井戸のトンネルトランジスタを提供する。

【解決手段】素子構造は、一つ或は複数の導電ベースリージョン33、第一半導体バリアーリージョン、第二半導体バリアーリージョン、導電エミッタリージョン31、導電コレクタリージョン35などを含み、第一半導体バリアーリージョン或は第二半導体バリアーリージョンのサイズは100Åより小く、第一ショットキーバリアの接合を第一半導体バリアーリージョンと導電ベースリージョンのインターフェイスで生じ、第二ショットキーバリアの接合を第二半導体バリアーリージョンと導電ベースリージョンのインターフェイスで生じ、第三ショットキーバリアの接合を導電エミッタリージョンと第一半導体バリアーリージョンのインターフェイスで生じ、第四ショットキーバリアの接合を導電コレクタリージョンと第二半導体バリアーリージョンのインターフェイスで生じる。

(もっと読む)

化合物半導体エピタキシャルウェハの製造方法

【課題】熱処理を行うことによって、電流利得を調整することができる化合物半導体エピタキシャルウェハの製造方法を提供する。

【解決手段】加熱された基板1上に、原料ガスを供給して、サブコレクタ層2、コレクタ層3、炭素ドープのベース層4、エミッタ層5、エミッタコンタクト層6を含むエピタキシャル層を形成する化合物半導体エピタキシャルウェハの製造方法において、エミッタコンタクト層6の形成直後に、熱処理を行う。

(もっと読む)

電流シフト領域を有する半導体デバイスおよび関連方法

半導体デバイスは、第1の伝導形を有する半導体バッファ層と、バッファ層の表面上にあって第1の伝導形を有する半導体メサとを含む。さらに第2の伝導形を有する電流シフト領域が半導体メサと半導体バッファ層との間の隅に隣接して設けられ、第1と第2の伝導形が互いに異なる伝導形である。関連する方法も開示される。  (もっと読む)

(もっと読む)

P型電界効果トランジスタ及びその製造方法

【解決手段】GaAsを用いることができる基板(1)の上方にn層(3)が配置され、前記n層上にp層(4)が配置される。前記p層は、ゲート電極(10)によって2つの別個の部分に分けられ、ソース及びドレインが形成されている。前記ゲート電極は、ゲート絶縁膜(6)によって半導体材料から絶縁されている。ソース/ドレインコンタクト(11)が、前記p層の前記2つの別個の部分に電気的に接続されている。 (もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】バイポーラトランジスタの高周波特性の向上を図る。

【解決手段】p型シリコン基板10上に形成されたn型導電型の第1コレクタ層14と、第1コレクタ層14上に形成された、第1コレクタ層14より幅の狭い、n型導電型の第2コレクタ層21と、第1コレクタ層14上に、第2コレクタ層21側面に接して形成された絶縁膜層20と、第2コレクタ層21上に形成された、p型導電型のベース層22と、ベース層22側面に接してに形成された、p型導電型のベース引き出し層25と、ベース層22上に形成された、n型導電型のエミッタ領域32とを備える。第1コレクタ層14とベース層22の間、又は第1コレクタ層14とベース引き出し層25の間に、絶縁膜層20が形成されていることにより、ベース・コレクタ間の接合容量を低減させる。

(もっと読む)

n型ベースを有するバイポーラトランジスタ及びその製造方法

【解決手段】ベースコンタクト接続部(12)、エミッタ部(4、5)及びコレクタ部がn層(3)上に配置され、当該n層は、更なるnpnバイポーラトランジスタために用いることができる。当該コレクタ部はエミッタ部に対して側方に配置され、当該エミッタ部及びコレクタ部の少なくとも一方は、当該n層の表面領域上でショットキーコンタクト(14)を備える。 (もっと読む)

半導体積層体を含む半導体装置の製造方法

【課題】 半導体下層と半導体上層が積層された半導体積層体において、半導体下層の表面に損傷を与えることなく、半導体下層の一部を露出させる技術を提供する

【解決手段】 半導体下層18の表面の一部に、半導体上層15とは格子定数の異なる格子不整合層30を形成する工程と、格子不整合層30の表面と格子不整合層30で被覆されていない半導体下層18の表面に、半導体上層15を結晶成長させる工程と、格子不整合層30上の半導体上層15に形成された転位40を介してウェットエッチング液を導入し、格子不整合層30とその格子不整合層30上の半導体上層15を除去して半導体下層18の一部を露出させる工程を備える。ドライエッチングにより半導体下層18に損傷を与えることなく、半導体下層18の一部を露出させることができる。

(もっと読む)

III族窒化物系化合物半導体素子及びその製造方法

【課題】積層された各層に平面的に電極が形成された、III族窒化物系化合物半導体素子

【解決手段】pnpトランジスタ100は、基板10の上に、図示しないバッファ層を介して、p型GaN層11、n型GaN層12、p型GaN層13を順に形成した後、ケミカルポリシングにより露出部である傾斜面11t、12t及び13tを形成し、そこに各々、コレクタ電極C、ベース電極B、エミッタ電極Eを形成して構成したものである。図1のpnp型トランジスタ100は、水平形状が1辺が500μmの矩形状で、その外周の1辺に水平面と10度の角度を成す傾斜面が形成されている。p型GaN層11、n型GaN層12及びp型GaN層13の膜厚はいずれも1μmであり、p型GaN層11の傾斜面11t、n型GaN層12の傾斜面12t及びp型GaN層13の傾斜面13tの幅はいずれも約5.8μmである。

(もっと読む)

81 - 100 / 349

[ Back to top ]