Fターム[5F003BG06]の内容

バイポーラトランジスタ (11,930) | ベース・コレクタ接合 (410) | Jc接合 (217) | ヘテロJc (199)

Fターム[5F003BG06]に分類される特許

81 - 100 / 199

ヘテロ接合バイポーラトランジスタ及びこれを用いた電力増幅器

【課題】大出力電力に対応した電力増幅用ヘテロ接合バイポーラトランジスタを小さい面積にレイアウトすることを可能とする。

【解決手段】サブコレクタ層上に、コレクタ層が互いに分離された複数のトランジスタ要素をエミッタの長辺方向に1列に配置して、ヘテロ接合バイポーラトランジスタを形成する。さらに、前記ヘテロ接合バイポーラトランジスタを単位トランジスタとして、マルチフィンガー型ヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

バイポーラトランジスタの製造方法

本発明は半導体基板(11)上にバイポーラトランジスタを製造する方法に関するものであり、前記半導体基板上に、全てが第1の導電型であるそれぞれ第1、第2および第3の半導体材料の第1、第2および第3の層(1、2、3)を設ける。第2の層(2)の第1部分を第1の電気的絶縁材料を含む埋め込み絶縁領域(15)に変換する。例えば、コレクタ領域を構成する第1の導電型の第1の半導体領域(6)を、埋め込み絶縁領域(15)に隣接する第2の層(2)の第2の部分および第2の層(2)の第2の部分に隣接する第1の層(1)の一部分から形成する。次に第3の層(3)を第1の導電型とは反対の第2の導電型に変換することにより、埋め込み絶縁領域(15)上および第1の半導体領域(6)上にベース領域(7)を形成する。その後、例えばエミッタ領域を構成する第1の導電型の第2の半導体領域(8)をベース領域(7)の一部分に形成する。この方法は、バイポーラトランジスタの形成方法を提供し、非本質的なコレクタ−ベース領域(6、7)間のキャパシタンスの値がコレクタ−ベース領域接合よりも十分に小さな誘電率を持つ埋め込み絶縁領域(15)によって主に決定されるという事実によって、非本質的コレクタ−ベース領域(6、7)間キャパシタンスが減少する利点を有する。  (もっと読む)

(もっと読む)

ヒューズ素子及びヒューズ素子を備えた半導体装置並びに半導体装置の製造方法

【課題】より低い電圧の印加によって溶断可能であって、しかも溶断に要する熱量を低減可能なヒューズ素子、及びヒューズ素子を備えた半導体装置、並びに半導体装置の製造方法を提供する。

【解決手段】ヒューズ素子は、半導体基板上に少なくともシリコンと、このシリコンよりも融点が低い元素とで形成した導電層と、この導電層の上面に形成した金属シリサイド層とで形成する。シリコンよりも融点が低い元素はゲルマニウムとする。特に、半導体基板には、上面に金属シリサイド層を設けたシリコン−ゲルマニウム層からなるベース引き出し電極を備えたバイポーラトランジスタが形成されており、導電層はバイポーラトランジスタにおけるシリコン−ゲルマニウム層の形成にともなってヒューズ素子部分に形成されたシリコン−ゲルマニウム層で形成する。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】高出力化に付随して要求される高耐破壊化を満たすヘテロ接合バイポーラトランジスタを提供する。

【解決手段】GaAsからなるn型のサブコレクタ層110と、サブコレクタ層110上に形成され、サブコレクタ層110よりアバランシェ係数の小さい半導体材料からなるn型の第1のコレクタ層121と、第1のコレクタ層121上に形成され、サブコレクタ層110より低い不純物濃度のn型又はi型のGaAsからなる第2のコレクタ層203と、第2のコレクタ層203上に形成され、GaAsからなるp型のベース層204と、ベース層204上に形成され、ベース層204よりバンドギャップの大きな半導体材料からなるn型のエミッタ層205とを備えるヘテロ接合バイポーラトランジスタ。

(もっと読む)

GaAs基板を用いたInP系半導体装置

【課題】本来InP基板に格子整合性を有するInP系半導体素子をGaAs基板に形成することができるようにする。

【解決手段】GaAs基板1上にInPメタモルフィックバッファ層2を、厚さ4μm以上として、その表面の欠陥密度を108/cm2以下にすることによって、GaAs基板上に、すぐれた特性と信頼性を有する、InP系半導体素子11を構成する

(もっと読む)

能動素子およびスイッチ回路装置

【課題】 HBTでは、ベース電流を増加させて電流密度の向上を図ると、二次降伏を起し、破壊に至りやすくなる。

【解決手段】 単位HBTと単位FETを分離領域を介して隣接して配置し、単位HBTのベース電極に単位FETのソース電極を接続した単位素子を複数接続して能動素子を構成する。これにより、単位素子に電流が集中した場合であっても二次降伏による破壊が発生しない能動素子を実現できる。また単位FETでは耐圧を確保するため埋め込みゲート電極構造を採用するが、埋め込み部をInGaP層に拡散させない構造とすることによりPtの異常拡散を防止できる。更に、単位HBTのエミッタメサ、ベースメサ形成、レッジ形成および単位FETのゲートリセスエッチングに選択エッチングを採用でき、再現性が良好となる。

(もっと読む)

バイポーラトランジスタ

【課題】臨界膜厚を厚くすることができるバイポーラトランジスタを提供することにある。

【解決手段】基板1上に核形成層2を形成し、核形成層2上にコレクタ電極層11を形成し、コレクタ電極層11上にノンドープIn0.1Ga0.9Nからなるコレクタ層12を形成し、コレクタ層12上にMgドープIn0.1Ga0.9Nからなるベース層13を形成し、ベース層13上にSiドープIn0.26Al0.74Nからなるエミッタ層14を形成し、エミッタ層14上にエミッタ電極層15を形成する。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタの電流増幅率の更なる向上とリーク電流の更なる低減とを好適に図ることのできる半導体装置を提供する。

【解決手段】シリコン基板11の主表面Saにおけるエミッタ電極18の外周面から低抵抗層21のエミッタ層17側の端部Sfまでの距離d1、素子分離領域13の内周面から外周面から低抵抗層21のエミッタ層17側の端部Sfまでの距離d2、及び素子分離領域13の底面Sdから、活性領域14の表層の領域における低抵抗層21の深さd3がシリコン基板11の主表面Saから0.04μm以上となるように、外部ベース層として機能する低抵抗層21の形成位置を設定する。

(もっと読む)

半導体装置の製造方法

【課題】水素ラジカルが発生する原料と水素ラジカルが発生しない原料とを使い分けることで、デバイス特性を低下させることなくエミッタ層の成長を行うとともにベース層の活性化を行うことを可能とする。

【解決手段】半導体基板101上に、インジウム・ガリウム・ヒ素を主成分とし、ドーパントとして炭素を含む第1の層(ベース層)105を形成する工程と、前記第1の層(ベース層)105の直上に水素ラジカルが発生するリン原料含む原料を流して、前記第1の層(ベース層)105上にインジウム・リンを主成分とする第2の層(低濃度エミッタ層)106を形成する工程と、前記第2の層(低濃度エミッタ層)106を形成する工程の後、水素ラジカルが発生しないリン原料を流して熱処理を行う工程とを備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】エミッタ層の寸法幅を微細化した高性能な半導体装置の製造方法を提供する。

【解決手段】シリコン基板1上に、素子分離膜3に囲まれた活性領域A1を形成する。素子分離膜3の上には活性領域A1を含む側の所定の領域に開口部A2を有するシリコン酸化膜からなる保護膜4を設ける。この活性領域A1上にSiGe合金層6aを形成し、SiGe合金層6a上にシリコン膜7およびn型拡散層(エミッタ層)13を形成する。このn型拡散層13は断面凸状のシリコン膜7の一部にn型不純物を拡散させて形成する。またn型拡散層13の上に多結晶シリコン膜8aおよびシリサイド膜15aを形成する。さらにn型拡散層13、多結晶シリコン膜8a、及びシリサイド膜15aは、絶縁膜からなる側壁膜11で囲う。さらにSiGe合金層6aのうち内部ベース層として働く領域の外側に、外部ベース層としてp+拡散層12aおよびシリサイド膜15bを形成する。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】ベース抵抗が小さく、最大発振周波数などの高周波特性が優れ、低雑音なバイポーラトランジスタおよびその製造方法を提供する。

【解決手段】Siコレクタ層3a上に、SiGeスペーサ層4a、傾斜SiGeベース層4b、Siキャップ層5が形成され、Siキャップ層5上にボロンドープのベース引き出し電極6が下全面接触で設けられ、ベース引き出し電極6に開口部6aが設けられ、開口部6aのベース引き出し電極6の側壁と底部Siキャップ層上に酸化膜7が設けられ、酸化膜7にエミッタ開口部7aが設けられている。エミッタ開口部7aを埋めるエミッタ引き出し電極9が設けられ、エミッタ引き出し電極9中のリンがSiキャップ層5に拡散されてエミッタ拡散層5aが形成されている。ベース引き出し電極6とエミッタ開口部7aは自己整合的に形成され、外部ベース層のリンク領域を削減し、ベース抵抗を低減できる。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】ベース抵抗が小さく、最大発振周波数などの高周波特性が優れ、低雑音なバイポーラトランジスタおよびその製造方法を提供する。

【解決手段】Siコレクタ層3a上に、SiGeスペーサ層4a、傾斜SiGeベース層4b、Siキャップ層5が形成され、Siキャップ層5上にエミッタ引き出し電極7が形成され、エミッタ引き出し電極7およびそのサイドウォール直下を除いたSiGeスペーサ層4a、傾斜SiGeベース層4b、Siキャップ層5にボロン注入でベース引き出し電極11が形成され、リンをSiキャップ層5中に拡散してエミッタ拡散層5aが形成され、ボロンをSiコレクタ層3a中に拡散して外部ベース拡散層1cが形成され、エミッタ拡散層5aの直下の真性ベース領域Bint に対して、ベース引き出し電極11と外部ベース拡散層1cで構成される外部ベース注入領域Bexを自己整合的に形成し、ベースリンク領域を削除し、ベース抵抗を低減できる。

(もっと読む)

バイポーラ接合トランジスタおよびその形成方法

【課題】バイポーラ接合トランジスタ(BJT)を提供すること。

【解決手段】各BJTのコレクタ領域は、半導体基板表面内に配置され、第1のシャロー・トレンチ・アイソレーション(STI)領域に隣接している。第2のSTI領域が形成され、この第2のSTI領域は、第1のSTI領域とコレクタ領域との間に延在し、約90°以下のアンダーカット角度で活性ベース領域の一部をアンダーカットする。例えば、第2のSTI領域は、約90°未満のアンダーカット角度のほぼ三角形の断面を有していても、約90°のアンダーカット角度のほぼ長方形の断面を有していてもよい。このような第2のSTI領域は、コレクタ領域の上側表面内に形成される多孔質表面部を使用して製作することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】エミッタからベース電極間の抵抗が低減され、高速動作が可能であり、高性能のバイポーラトランジスタを有する半導体装置を提供する。

【解決手段】半導体基体上に形成された絶縁膜の開口を含むように、シリコン層9A,9C、シリコンとゲルマニウム及び/又はカーボンとを有する層9B、により成るシリコン混晶層9によって形成されたエピタキシャルベース領域を有するバイポーラトランジスタが形成されて成り、シリコン混晶層9の最上層9Cがシリコン層であり、シリコン混晶層9から成るベース領域のうち、単結晶シリコン混晶層上及び多結晶シリコン混晶層上に、多結晶シリコン膜10を介してコバルトシリサイド11が形成されて成る半導体装置を構成する。

(もっと読む)

半導体装置の製造方法

【課題】 エミッタ層の寸法幅を微細化した高性能な半導体装置の製造方法を提供する。

【解決手段】 シリコン基板1上に、素子分離領域3に囲まれたエピタキシャル層2(活性領域2a)を形成する。この活性領域2a上にSiGe合金層4を形成し、SiGe合金層4上にシリコン膜5およびn型拡散層(エミッタ層)6を形成する。このn型拡散層6は断面凸状のシリコン膜5の一部にn型不純物を拡散させて形成する。またn型拡散層6の上に多結晶シリコン膜7aおよびシリサイド膜11aを形成する。さらにn型拡散層6、多結晶シリコン膜7a、及びシリサイド膜11aは、絶縁膜からなる側壁膜9で囲う。さらにSiGe合金層4のうち内部ベース層として働く領域の外側に、外部ベース層としてp+拡散層10およびシリサイド膜11bを形成する。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】ベース・エミッタのへテロ接合における伝導帯下端のバンド不連続(ΔEc)を無くすことが可能なヘテロ接合バイポーラトランジスタを提供する。

【解決手段】半絶縁性GaAsから構成される基板101と、基板101に格子整合するエピタキシャル層100とからなるヘテロ接合バイポーラトランジスタであって、エピタキシャル層100は、n+−GaAsから構成されるサブコレクタ層102と、n−GaAsから構成されるコレクタ層103と、p+−GaPSbから構成されるベース層104と、GaPSbと電子親和力が同じで、GaPSbよりもバンドギャップエネルギーが大きいInGaPから構成されるエミッタ層105とを有する。

(もっと読む)

メタルベースナノワイヤトランジスタ

メタルベーストランジスタを示す。該トランジスタは、第一電極2及び第二電極6と、該第一及び第二電極間の電流流れを制御するベース電極3とを備える。第一電極2を半導体材料から作製する。ベース電極は、第一電極を形成する半導体材料の上に堆積した金属層である。本発明によれば、第二電極は、ベース電極3と電気接触した半導体ナノワイヤにより形成される。  (もっと読む)

(もっと読む)

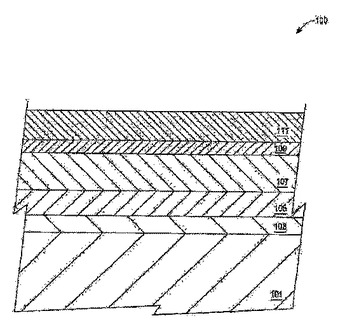

歪み補償の準安定化合物ベースヘテロ接合バイポーラトランジスタ

歪み補償原子種を置換配列することにより、例えば、SiGe NPN HNTの電子装置(100)へ、その場で添加した歪み補償の準安定化合物基部(107)を電子装置(100)に擬似格子整合を増大し統一するための方法。本発明は歪みSiGe、MOSアプリケーションのSi、垂直薄膜トランジスタ(VTFT)、および様々なその他の電子装置型などの、その他の電子装置の歪み層にも適用する。例えば、GaAs、InP、およびAlGaAsの、SiGe以外の化合物半導体から形成される装置も本願に記載する有益な工程に適している。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】ベース抵抗の低減とアーリー電圧の増加を併せて実現しうる半導体装置およびその製造方法を提供する。

【解決手段】外部ベース層51の領域にカーボンを添加し、外部ベース用ボロン注入時に発生する点欠陥生成を防止するように設定したものである。

(もっと読む)

半導体デバイスおよびその製造方法

本発明は、シリコンからなる基板および半導体本体を備え、エミッタ領域(1)、ベース領域(2)およびコレクタ領域(3)を有するバイポーラトランジスタを具え、前記エミッタ領域(1)、前記ベース領域(2)および前記コレクタ領域(3)の伝導型が、適切なドーピング原子の提供により、それぞれn型、p型、そしてn型である半導体デバイス(10)であって、前記ベース領域(2)が、シリコンおよびゲルマニウムの混晶を有し、前記ベース領域(2)は、前記エミッタ領域(1)よりも低いドーピング濃度を有し、かつ前記エミッタ領域(1)よりも小さい厚さを有する、シリコンからなる中間領域(22)によって、前記エミッタ領域(1)から分離され、前記エミッタ領域(1)が、シリコンおよびゲルマニウムの混晶を有し、前記中間領域(22)から離れたエミッタ領域(1)のサイドに位置決めされるサブ領域を具える半導体デバイスに関する。本発明によれば、シリコンおよびゲルマニウムの混晶を有する前記サブ領域は、実質的に、前記エミッタ領域(1)の全体を通って、前記中間領域(22)との界面まで延在し、かつ前記エミッタ領域(1)のドーピング原子が、ヒ素原子であることを特徴とする。そのようなデバイスは、中間領域で、または、その範囲内で、非常に急勾配のn型ドーピングプロファイル(50)および非常に急勾配のp型ドーピングプロファイル(20)を有し、したがって、高カットオフ周波数(fr)を備える、優れた高周波挙動を有する。好ましくは、前記エミッタ領域(1)は、その上半部において、ヒ素注入(I)によってドープされ、最後のドーピングプロファイルはRTAの後に形成される。本発明は、本発明に従うデバイス(10)の製造方法もまた具える。  (もっと読む)

(もっと読む)

81 - 100 / 199

[ Back to top ]