Fターム[5F003BG06]の内容

バイポーラトランジスタ (11,930) | ベース・コレクタ接合 (410) | Jc接合 (217) | ヘテロJc (199)

Fターム[5F003BG06]に分類される特許

21 - 40 / 199

半導体装置およびその製造方法

【課題】低コストで性能向上が可能なBiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】n型の半導体基板1の表面から所定の深さに、コレクタ領域を構成するn型の不純物領域26を備える。当該不純物領域26の上方、かつ半導体基板1に形成されたシャロートレンチ分離14で挟まれた領域18にはp型のベース領域20を備える。ベース領域20には、n型の半導体膜からなるエミッタ電極が接触して設けられている。当該半導体装置は、不純物領域26がベース領域20下からシャロートレンチ分離14下まで延在し、当該シャロートレンチ分離14を貫通して不純物領域26に電気的に接続するコンタクトプラグ52を備える。

(もっと読む)

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】同一基板に形成されるHBTとFETとの相互影響を低減する。

【解決手段】第1半導体と、第1半導体の上方に形成された第2半導体とを備え、第2半導体は、P型の伝導型を示す不純物またはN型の伝導型を示す第1不純物原子と、第2半導体が第1不純物原子を有する場合のフェルミ準位を、第2半導体が第1不純物原子を有しない場合のフェルミ準位に近づける第2不純物原子とを有する半導体基板を提供する。一例として、当該第2半導体の多数キャリアは電子であり、第2不純物原子は、第1不純物原子を有する第2半導体のフェルミ準位を下降させる。第2半導体は3−5族化合物半導体であり、第2不純物原子が、ベリリウム、ボロン、炭素、マグネシウム、および亜鉛からなる群から選択された少なくとも1つであってもよい。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】高電流注入における高周波特性が改善されたダブルヘテロ接合バイポーラトランジスタを提供すること。

【解決手段】基板1上に、サブコレクタ層2、コレクタ層、ベース層4、エミッタ層5、キャップ層6が順次積層されたダブルヘテロ接合バイポーラトランジスタにおいて、前記コレクタ層が、第1の半導体層31と第2の半導体層32の積層構造から形成され、第1の半導体層31と第2の半導体層32がType−II型のヘテロ接合を形成し、第2の半導体層32とベース層4がホモ接合あるいはType−I型のヘテロ接合を形成することを特徴とするダブルヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法

【課題】半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法を提供する。

【解決手段】シリコンに不純物原子が導入された不純物領域104を有するベース基板102と、不純物領域104に接して設けられている複数のシード体112と、複数のシード体112の各々に接して設けられ、複数のシード体112の各々とそれぞれ格子整合または擬格子整合する複数の化合物半導体114とを備える半導体基板100。当該半導体基板100は、ベース基板102上に設けられ、不純物領域104の少なくとも一部を露出する複数の開口が設けられた阻害体をさらに備えてもよい。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】エミッタ電子輸送特性やエミッタ注入効率を劣化させることなく、レッジ部を薄層化することが容易で、微細化に適したヘテロ接合バイポーラトランジスタを提供すること。

【解決手段】エミッタ層は、第1の半導体層11と、第2の半導体層12と、第3の半導体層13との積層構造からなり、第3の半導体層13は、第2の半導体層12に対してウェット・エッチングにより選択的に除去でき、第2の半導体層12は、第1の半導体層11に対してウェット・エッチングにより選択的に除去でき、第1の半導体層11と第3の半導体層13のバンドギャップはベース層4のバンドギャップよりも大きく、第2の半導体層12は不純物添加によって縮退しており、第3の半導体層13は不純物添加によって中性領域を形成しているヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】コレクタ層に用いる材料のバンドギャップを大きくし、コレクタ層の膜厚・キャリア濃度を変更せずに高耐圧化を図ることができるヘテロ接合バイポーラトランジスタを提供する。

【解決手段】半絶縁性化合物半導体基板上に、サブコレクタ層、コレクタ層、ベース層、エミッタ層、エミッタコンタクト層、ノンアロイ層が順次形成されてなるヘテロ接合バイポーラトランジスタにおいて、前記エミッタ層はInGaPからなり、前記コレクタ層はAlxGa(1-x)As(0≦x≦1)からなり、さらに前記コレクタ層は、前記サブコレクタ層側から前記ベース層側へxが大きくなるグレーデッド層と、前記グレーデッド層上に形成されるxが一定の定混晶比層とを有するものである。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】バイポーラトランジスタにおいて、耐圧改善のためにコレクタ濃度を低くした際のトランジスタとしての性能低下を抑制する。

【解決手段】バイポーラトランジスタ100は、コレクタ層3上に、エピタキシャル成長されたヘテロ接合の真性ベース層50を有する。真性ベース層50は、分離層4に囲まれたコレクタ層3上に配置され、コレクタ層3の表面部に、N型不純物層30が形成されている。N型不純物層30の不純物濃度は、N型不純物層30の下方におけるコレクタ層3の不純物濃度よりも高い。N型不純物層30と真性ベース層50との間に、N型不純物層30及び真性ベース層50よりも不純物濃度が低いエピタキシャル成長層が形成されている。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】単一半導体基板上にHBTおよびFETのような複数異なる種類のデバイスを形成するに適した半導体基板を製造する方法を提供する。

【解決手段】半導体を結晶成長させる反応容器内に第1不純物原子を構成要素として有する単体または化合物を含む第1不純物ガスを導入する段階を含む複数の段階を繰り返して、複数の半導体基板を製造する方法であって、第1不純物ガスを導入する段階の後に、製造された半導体基板を取り出す段階と、反応容器内に第1半導体を設置する段階と、反応容器内に、第1半導体内で第1不純物原子と反対の伝導型を示す第2不純物原子を構成要素として有する単体または化合物を含む第2不純物ガスを導入する段階と、第1半導体を第2不純物ガスの雰囲気中で加熱する段階と、加熱した前記第1半導体上に第2半導体を結晶成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体装置

【課題】高耐圧化及び高温動作を実現できる、HBTとFETを備える半導体装置を提供する。

【解決手段】本発明に係る半導体装置100は、基板101の上に順時積層されたn+型GaN層103及びn型GaN層104と、p型InGaN層105と、アンドープGaN層106及びn型AlGaN層107と、HBT領域121のn+型GaN層103と電気的に接続されたコレクタ電極114と、HBT領域121のp型InGaN層105と電気的に接続されたベース電極113と、HBT領域121のn型AlGaN層107と電気的に接続されたエミッタ電極112と、HFET領域120のn型AlGaN層107と電気的に接続されたソース電極109及びドレイン電極111と、n型AlGaN層107の上に形成されたゲート電極110とを備える。

(もっと読む)

バイポーラトランジスタの製造方法

【課題】最終的なコレクタを薄層化しつつ、広い線幅のSiO2細線を例とする絶縁物細線の埋め込みを可能にし、低消費電力での超高速動作が可能なバイポーラトランジスタの製造方法を提供すること。

【解決手段】半絶縁性基板1上にサブコレクタ層2を形成する工程と、サブコレクタ層2上に絶縁物3の細線を形成する工程と、サブコレクタ層2および絶縁物3の細線を覆うコレクタ層4を形成する工程とを有するバイポーラトランジスタの製造方法において、前記サブコレクタ層2および絶縁物3の細線を覆うコレクタ層4を形成する工程は、コレクタ層2の表面をエッチングする工程を含むことを特徴とするバイポーラトランジスタの製造方法を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の特性を向上できると共に、製造コストを低減できる。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1上に順次積層されたコレクタ層2A、ベース層3A及びエミッタ層4Aと、コレクタ層2Aの側面上に設けられ、コレクタ層に対して歪み応力を与える第1ストレスソース膜15Aと、ベース層3Aの側面上に設けられ、ベース層3Aに対して歪み応力を与える第2ストレスソース膜17と、を具備し、第1ストレスソース膜15A上端及び前記ベース層上端は、半導体基板表面から同じ高さに位置し、第2ストレスソース膜17は、ベース層3Aの側面と第1ストレスソース膜15Aの側面との間に設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】 シリコン基板上にゲルマニウムを主成分とする半導体素子を形成する際に、バッファ層を薄くすることで段差を減らし、同一基板上にシリコン系半導体素子を混載することを容易にする。

【解決手段】 具体例を述べれば、バッファ層をゲルマニウム層とシリコン層の2層とし、シリコン層のみを溶融することでゲルマニウムの面内原子間隔を安定的に保持するバッファ層を形成し、その上にゲルマニウム層を形成することで転位密度等の結晶欠陥を低減する。

(もっと読む)

トランジスタ素子およびその製造方法

【課題】

ベース電極とコレクタ半導体の電荷注入障壁の制御が可能である、高性能な縦型薄膜のトランジスタ素子および製造方法を提供する。

【解決手段】

基板10上に、第一電極20と、コレクタ半導体層30と、ベース電極40と、エミッタ半導体層31と、第二電極21とを順次積層するトランジスタ素子において、コレクタ半導体層とエミッタ半導体層の間にベース電極が存在するようにするとともに、コレクタ半導体層が金属酸化物よりなることを特徴とする。

(もっと読む)

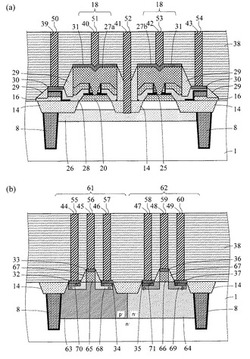

バイポーラトランジスタの製造方法及びバイポーラトランジスタ

【課題】バイポーラトランジスタの高周波特性を向上させる。

【解決手段】ヘテロバイポーラトランジスタ70は、ベースとエミッタ、ベースとコレクタがヘテロ接合を有し、双条ベース構造を有する。N型エピタキシャル層3上の内部ベース層(P型SiGe層)5と接する外部ベース層10、及び内部ベース層(P型SiGe層)5上には、絶縁膜7及びN型多結晶シリコン膜8が積層形成される。積層形成された絶縁膜7及びN型多結晶シリコン膜8の中央部にはエミッタ開口部19が設けられる。エミッタ開口部19にはN型エピタキシャル層11が設けられる。N型エピタキシャル層11及びN型多結晶シリコン膜8上には、エミッタ開口部19を覆うようにT型形状を有するN型多結晶シリコン膜12が設けられる。左右のN型多結晶シリコン膜8及びエミッタ開口領域は同時に形成され、左右のN型多結晶シリコン膜8の幅は同一に設定される。

(もっと読む)

半導体装置

【課題】SiGe混晶層を有する半導体装置において、高い高周波特性と安定した低いベースコンタクト抵抗とを得られるようにする。

【解決手段】半導体装置は、N型のコレクタ層1aと、コレクタ層1aの上に形成され、P型SiGe層3bを含む真性ベース層となるSiGeエピ膜3と、SiGeエピ膜3の周囲に形成され、P型の多結晶シリコン層及びP型の多結晶シリコンゲルマニウム層を含むベース引き出し電極4と、SiGeエピ膜3の上部に形成されたN型のエミッタ層8とを有している。真性ベース層の上部には、Si−Cap層3cが形成されており、エミッタ層8は、Si−Cap層3cの上部に形成された上部エミッタ領域8bと、該上部エミッタ領域8bの下側に該上部エミッタ領域8bと接して形成された下部エミッタ領域8aとにより構成されている。

(もっと読む)

高周波デバイスの誘電体突出部

(例えばシリコン)バイポーラデバイス(40、100、100’)の高周波性能は、外部ベースコンタクト(46)とコレクタ(44、44’、44”)との間の容量結合(Cbc)の低減により向上される。外部ベースコンタクト(46)をコレクタ(44、44’、44”)の外周部(441)から隔てるように、製造中に誘電体突出部(453、453’)が作製される。誘電体突出部(453、453’)は、外部ベースコンタクト(46)を真性ベース(472)に結合するトランジション領域(461)の下に位置する。デバイス製造中に、多層誘電体スタック(45)が真性ベース(472)に隣接して形成され、真性ベース(472)から外部ベースコンタクト(46)へのトランジション領域(461)を形成可能なアンダーカット領域(457、457’)の同時作製が可能にされる。キャビティ(457、457’)内に形成されたトランジション領域(461)が、それをコレクタ(44、44’、44”)の外周部(441)から隔てる誘電体突出部(453、453’)の上に位置することで、ベース−コレクタ接合容量(Cbc)が低減される。デバイスのfMAXが有意に上昇される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】非選択エピタキシャル法により半導体層を形成しても、エミッタとベースとを確実に接続して高い信頼性を確保することができる半導体装置及びその製造方法を提供する。

【解決手段】非選択エピタキシャル成長法により、ベース開口部8の内壁を覆うようにシリコン酸化膜7の全面にSiGe膜9を成長させる。このときの成膜条件としては、ベース開口部8内において、底部9aが単結晶からなり、側壁部9b等のその他の部位が多結晶となると共に、側壁部9bの膜厚が底部9aの膜厚の1.5倍以下になる成膜条件を選択する。このような非選択エピタキシャル成長では、原料ガスとして、モノシラン、水素、ジボラン及びゲルマンを用いる。このとき、モノシラン及び水素の各流量は、夫々20sccm、20slmとする。また、成長温度を650℃、ジボランの流量を75sccmに設定し、ゲルマンの流量を35sccmに設定する。

(もっと読む)

半導体デバイスの製造方法

【課題】犠牲層を介してInP系のデバイスを形成したときに、犠牲層としてAlAs単層を用いたときのデバイス特性よりも良好なデバイス特性を得ることができ、かつ、犠牲層をエッチングする際に、デバイス層もエッチングされてしまう虞のない半導体デバイスの製造方法を提供する。

【解決手段】保護膜35の平坦面35Aに支持基板10を接合もしくは接着したのち、InPと疑似格子整合するInAlAsからなる犠牲層42を、フッ酸を用いて選択的に除去することにより、InP基板41を、InP系のデバイス層21を含む支持基板10から剥離する。

(もっと読む)

半導体装置

【課題】 エッチング量を工程内で測定し、フィードバックをかけることにより、エッチング量のばらつきを無くすことを実現する。

【解決手段】 半導体層が選択エッチングされることにより半導体素子が形成される半導体素子領域と、前記半導体層と同じ材質からなり、前記半導体素子が選択エッチングされた量を検査するモニタ用半導体素子が設けられたモニタ領域とを有することを特徴とする。

(もっと読む)

半導体素子の製造方法

【課題】 偶発的に生成される層を異方性エッチングすることにより、エッチングを行う時間によるエッチングのばらつきを改善し、かつ任意の層を異方性エッチングで一定量エッチングすることにより、回り込みエッチングの制御性の向上を図ることを実現する。

【解決手段】 第1の層の表面に第2の層を積層したものに、前記第1の層を横方向にエッチングする半導体素子の製造方法において、前記第2の層側から前記第1の層側に向かって縦方向に異方性エッチングを行うステップと前記第1の層を横方向に等方性エッチングを行うステップとを有することを特徴とする。

(もっと読む)

21 - 40 / 199

[ Back to top ]