Fターム[5F003BP46]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | 酸化 (33)

Fターム[5F003BP46]の下位に属するFターム

Fターム[5F003BP46]に分類される特許

1 - 20 / 24

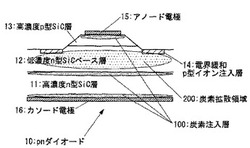

SiCバイポーラ型半導体素子

【課題】キャリア捕獲中心の少ないSiC半導体素子を提供する。

【解決手段】n型またはp型のSiC基板11と、n型またはp型の少なくとも1つのSiCエピタキシャル層12、あるいはn型またはp型の少なくとも1つのイオン注入層14と、を有し、pn接合界面付近および伝導度変調層(ベース層)内を除いた、SiC基板表面付近、SiC基板とSiCエピタキシャル層との界面付近、およびSiCエピタキシャル層の表面付近のうち少なくとも1つの領域100に、炭素注入層、珪素注入層、水素注入層、またはヘリウム注入層を有し、かつ、炭素原子、珪素原子、水素原子、またはヘリウム原子をイオン注入することで導入した格子間炭素原子をアニーリングにより伝導度変調層内へ拡散させるとともに格子間炭素原子と点欠陥とを結合させることで、電気的に活性な点欠陥が低減された領域を伝導度変調層内に有するSiCバイポーラ型半導体素子。

(もっと読む)

バイポーラ半導体素子

【課題】高温や電流密度が高い条件下でも基板へ少数キャリアが到達するのを防いで、順方向電圧の増大を防ぐことができるバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20では、n型SiC基板21とn型バッファ層22との間に形成したn型少数キャリア消滅層31は、n型バッファ層22よりも炭素空孔欠陥の濃度が高く、少数キャリア消滅層31の炭素空孔欠陥はp型のアノード層24,25からの正孔のトラップとして働く。よって、小数キャリア消滅層31に達した正孔(少数キャリア)がトラップされ、小数キャリア消滅層31において正孔密度K2が急激に減衰する。これにより、正孔(少数キャリア)が基板21へ到達することを防いで、基板21から積層欠陥が拡大するのを防いで、順方向電圧の増大を防止できる。

(もっと読む)

半導体基板の製造方法

【課題】イオン注入後のアニール後に生じる残留欠陥を除去することができ、その後シリコンエピタキシャル層を形成しても積層欠陥を生じない、高品質な半導体基板の製造方法を提供する。

【解決手段】半導体基板の製造方法であって、少なくとも、シリコン単結晶基板に選択的にイオン注入を行う工程と、該イオン注入後に、前記シリコン単結晶基板の結晶性を回復させる回復熱処理と前記注入イオンを拡散させる拡散熱処理を行う熱処理工程と、該熱処理後に、前記イオン注入工程によって前記シリコン単結晶基板の表面層に形成されたアモルファス層の全部を取り込む厚さの熱酸化膜を形成する熱酸化膜形成工程と、該形成された熱酸化膜を除去する工程と、該熱酸化膜を除去した表面上にエピタキシャル層を形成する工程と、を有することを特徴とする半導体基板の製造方法。

(もっと読む)

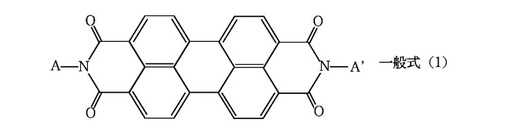

トランジスタ素子

【課題】エミッタ電極−コレクタ電極間において、オフ電流が小さく、かつ、低電圧で大電流変調が可能であるオン/オフ比に優れたトランジスタ素子を提供すること。

【解決手段】エミッタ電極とコレクタ電極との間に、有機半導体層とシート状のベース電極とが設けられているトランジスタ素子において、該有機半導体層が、下記一般式(1)で表される化合物を含んでいるトランジスタ素子。 (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】微細加工が求められる半導体装置であるBiCMOSの製造方法に関し、特に半導体基板上に形成されるエピタキシャル層の表面の平坦性を向上することを課題とする。

【解決手段】本発明のBiCMOSの製造方法は、P型シリコン基板1の主面をエッチングしてくぼみ部32を形成する第1工程と、くぼみ部32を被覆するシリコン酸化膜22をマスクにして当該P型シリコン基板1にN+型埋め込み層2を形成する第2工程と、N+型埋め込み層2を含むP型シリコン基板1の主面を熱酸化して、P型シリコン基板1上にシリコン酸化膜22を含むシリコン熱酸化膜25を形成する第3工程と、シリコン熱酸化膜25を除去した後、N+型埋め込み層2を含むP型シリコン基板1の主面上にN型エピタキシャル層を形成する第4工程と、を含む。

(もっと読む)

トランジスタ素子及びその製造方法並びに発光素子及びディスプレイ

【課題】エミッタ電極−コレクタ電極間において、低電圧で大電流変調を可能とするトランジスタ素子を提供する。また、そうしたトランジスタ素子の製造方法、また、そのトランジスタ素子有する発光素子及びディスプレイを提供する。

【解決手段】エミッタ電極3とコレクタ電極2との間に、半導体層5(5A,5B)とシート状のベース電極4が設けられているトランジスタ素子により、上記課題を解決する。半導体層5は、エミッタ電極3とベース電極4との間及びコレクタ電極2とベース電極4との間に設けられて、それぞれ第2半導体層5B及び第1半導体層5Aを構成し、さらに、ベース電極の厚さが80nm以下であることが好ましい。また、少なくともエミッタ電極とベース電極との間又はコレクタ電極とベース電極との間には、暗電流抑制層が設けられていてもよい。

(もっと読む)

有機トランジスタ素子と電子・電気機器

【課題】 大気圧下加熱処理などを行わずに、MBOT素子構造の改良により良好な電流増幅特性やON/OFF比を得る。

【解決手段】 エミッタ電極とコレクタ電極との間に有機半導体層とシート状のベース電極が設けられている有機トランジスタ素子であって、前記ベース電極とコレクタ電極の間に、電荷透過促進層を有するものとする。

(もっと読む)

半導体を用いた電子デバイス

【課題】高耐圧電子デバイスおよび耐環境電子デバイスを提供する。

【解決手段】本発明においては、ダイオードやトランジスタ等の電子デバイス中で電子が走行する領域に、高純度の酸化モリブデンであって、その禁制帯幅が3.45eV以上であるような酸化モリブデンが用いられる。本発明によれば、高耐圧特性および高耐環境特性を有する電子デバイスが実現できる。

(もっと読む)

半導体装置

【課題】エミッタ電極に対するコンタクト部を容易に形成しながら、エミッタ層の幅を小さくすることが可能な半導体装置を提供する。

【解決手段】このバイポーラトランジスタ(半導体装置)100は、シリコン層7と、シリコン層7の表面に形成された不純物領域8と、不純物領域8上に形成されたポリシリコン層からなるエミッタ電極10aと、不純物領域8とエミッタ電極10aとの間に形成され、エミッタ電極10aの幅W3よりも小さい幅W2を有するSiGe層9とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、深いエッチングや長時間の拡散を要することなく素子分離構造或いは引出電極構造を構成することによって素子間隔や素子自体を縮小する。

【解決手段】 一導電型半導体基板1上に逆導電型エピタキシャル層2を設けるとともに、逆導電型エピタキシャル層2に素子分離絶縁膜を含む局所的選択酸化膜3を設けた半導体装置における局所的選択酸化膜3を貫通するとともに一導電型半導体基板1に達しない貫通孔4を設けるともに、一導電型半導体基板1に達する高不純物濃度領域5を貫通孔4の底部に接するように設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波用途の半導体装置に採用する厚い絶縁膜をLOCOS法で形成する場合に、バーズビーグ増による欠陥の増大や、高温で長時間の酸化時間に伴う欠陥の増大という問題があった。これ等の問題点を考慮すると、超高周波用途の半導体装置に現状で用いることができる酸化膜の膜厚を厚くするにも限界があった。

【解決手段】半導体層に複数のトレンチを設け熱酸化により一体化して、内部に空隙部を有する絶縁領域を形成する。トレンチの深さで絶縁領域の厚みを制御でき、従来のLOCOS法以上の厚い絶縁領域を結晶欠陥等を増大することなく形成できる。絶縁領域を例えば電極パッドの下方に設けることにより、浮遊容量を低減できる。また、絶縁領域内部の空隙部によって、更に浮遊容量を低減できる。

(もっと読む)

半導体装置およびその製造方法

【課題】電流増幅率hFEやコレクタ・エミッタ間の耐圧を、他の半導体素子に影響を与えずに、容易に調整することができる半導体装置及びその製造方法を提供する。

【解決手段】本半導体装置は、第1の導電型不純物を含む半導体基板と、半導体基板上に形成された第2の導電型不純物を含む第1の半導体領域と、第1の半導体領域上に、周囲を第1の導電型不純物を含む第2の半導体領域で囲むように形成された、第2の導電型不純物を含む第3の半導体領域と、第2の半導体領域直下の第1の半導体領域内に形成された、第1の半導体領域より高濃度の第2の導電型不純物を含む埋込半導体領域と、第2の半導体領域及び第1の半導体領域の接合部に形成された、第1の半導体領域より高濃度の第2の導電型不純物を含む介挿半導体層とを有し、第3の半導体領域をエミッタとし、第2の半導体領域をベースとし、埋込半導体領域をコレクタとするバーティカル型バイポーラトランジスタである。

(もっと読む)

半導体装置の製造方法およびエミッタポリシリコン電極構造をもつバイポーラトランジスタの電流増幅率の調整方法

【課題】ポリシリコンエミッタ電極構造の縦型NPNバイポーラトランジスタの電流増幅率を、何らの工程を付加することなく制御し、低コスト化とバイポーラトランジスタの高周波数応答特性とを両立させる。

【解決手段】低温による(400℃)のエミッタポリシリコン190の形成時に、真性ベース140とポリシリコンエミッタ190間に界面酸化膜(自然酸化膜)が成長する。その後、エミッタ150を形成するための熱処理温度を、820℃〜910℃の範囲で調整することによって、界面酸化膜の状態と電子のパイルアップ状態を制御し、これによって、電流増幅率を微調整する。

(もっと読む)

トランジスタ素子及びその製造方法並びに発光素子及びディスプレイ

【課題】エミッタ電極−コレクタ電極間において、低電圧で大電流変調を可能とするトランジスタ素子を提供する。また、そうしたトランジスタ素子の製造方法、また、そのトランジスタ素子有する発光素子及びディスプレイを提供する。

【解決手段】エミッタ電極3とコレクタ電極2との間に、半導体層5(5A,5B)とシート状のベース電極4が設けられているトランジスタ素子により、上記課題を解決する。半導体層5は、エミッタ電極3とベース電極4との間及びコレクタ電極2とベース電極4との間に設けられて、それぞれ第2半導体層5B及び第1半導体層5Aを構成し、さらに、ベース電極の厚さが80nm以下であることが好ましい。また、少なくともエミッタ電極とベース電極との間又はコレクタ電極とベース電極との間には、暗電流抑制層が設けられていてもよい。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法およびヘテロ接合バイポーラトランジスタ

【課題】特にGaAsSb系ベース層を有するHBTにおいて、HBT素子の特性を劣化させることなく、素子表面を部分的に不活性化するHBTを提供する。

【解決手段】所定の材質の基板1上に形成したコレクタ層3、ベース層4、エミッタ層5を含む層構造の少なくとも側壁をAl酸化膜8で覆っている構造とする。基板1としてInPを、ベース層4に、少なくとも一層はAl(x)Ga(1−x)As(y)Sb(1−y)を用いる(x,y:組成比、0.0≦x≦0.2,0.2≦y≦0.8)。すなわち、基板1上に、エミッタ層5、ベース層4、コレクタ層3を含むHBTの層構造を結晶成長により作製した後、エッチングによりメサ状に加工し、さらに、表面に堆積させた前記Al化合物を酸化させることによりAl酸化膜8を形成し、電極形成領域に堆積させたAl酸化膜8をエッチングにより除去して電極9を形成する。

(もっと読む)

縦型バイポーラトランジスタおよびその製造方法

【課題】高い直流電流増幅率、特に小電流領域で高い直流電流増幅率を得ることができる縦型バイポーラトランジスタを提供する。

【解決手段】n型半導体基板1の下層に高濃度n型半導体層2を形成し、上層にp型半導体層3を形成し、p型半導体層3に表面から層内へ延在する高濃度n型半導体層4を形成し、p型半導体層3および高濃度n型半導体層4に二酸化珪素膜5を形成してなり、所定の水分を添加した酸素、または所定の水分を添加した酸素を含むガスからなる雰囲気下で熱処理することにより、二酸化珪素膜5の表面電荷密度を低くして、高い直流電流増幅率、特に小電流領域に於いて高い直流電流増幅率を得る。

(もっと読む)

半導体装置の製造方法

【課題】 層厚の厚い電極部および信頼性の高い保護膜を形成することができる半導体装置の製造方法を提供する。

【解決手段】 半導体層21の積層方向Zの一表面上に電極部34を形成する。次に半導体層21および電極部34とを予め定める第1の温度T1のN2雰囲気下でシンタ処理し、半導体層21と電極部34とのオーミック性を向上させる。次にPSG膜35がアニーリングされかつ堆積される予め定める第2の温度T2において、酸化膜22の表面と電極部34の表面とにPSG膜35を堆積して形成する。次にPSG膜35の一部をエッチングすることによって、電極部34の一部が露出するように第2貫通孔37を形成する。

(もっと読む)

バイポーラトランジスタの製造方法およびそれを用いたバイポーラトランジスタ

【課題】直流電流増幅率の特性が向上した耐電圧、大電力のバイポーラトランジスタの製造方法を提供する。

【解決手段】ベース領域3及びエミッタ領域4の上部に、それぞれベース電極パターン9a、エミッタ電極パターン10aを形成する。形成方法は、電極材料であるAlをスパッタ処理によりAl膜を形成し、リソグラフィ、ドライエッチング処理により電極パターンにする。次に、酸化剤である水、酸素雰囲気下で熱処理を行ない、表面が酸化されたベース電極9b、エミッタ電極10bを形成する。

(もっと読む)

バイポーラトランジスタの製造方法及びバイポーラトランジスタを有する半導体装置の製造方法

【課題】

エミッタ抵抗を低減でき電流利得特性を向上させたバイポーラトランジスタの製造方法及び、このバイポーラトランジスタを有する半導体装置の製造方法を提供する。

【解決手段】

コレクタ領域の表面に第1酸化膜を形成する工程と、第1酸化膜の表面にベース層を形成する工程と、ベース層の表面に第2酸化膜を形成した後にベース層をパターニングするとともに、コレクタ電極形成位置の第1酸化膜をエッチングすることにより前記第2酸化膜と等しい膜厚にする工程と、エミッタ電極を形成するためのエミッタ用開口及びコレクタ電極を形成するためのコレクタ用開口を形成する工程とを有することとした。

(もっと読む)

半導体装置及びその製造方法

【課題】 欠陥制御と拡散制御を同時に実現し、信頼性の高い半導体装置の製造方法を提供する。

【解決手段】 P型シリコン基板1の主表面領域中に、N+ 埋め込み層2およびN型エピタキシャル層3が形成されている。N型エピタキシャル層3にはSTI溝60が形成され、その凹部内面には熱酸化膜6が形成されている。さらにSTI溝60はHDP−NSG膜7で埋め込まれている。また、STI溝60内に形成された深い溝70はシリコン基板1に到達するまでの深さで形成され、その凹部内面には熱酸化膜9が形成されている。この熱酸化膜9の膜厚はSTI溝60内の熱酸化膜6よりも薄く形成されている。また、深い溝70内には、さらにシリコン酸化膜10が形成され、ポリシリコン膜11で埋め込まれている。

(もっと読む)

1 - 20 / 24

[ Back to top ]