Fターム[5F082DA02]の内容

Fターム[5F082DA02]に分類される特許

1 - 20 / 50

半導体デバイス

【課題】高い電流増幅率と高いアーリー電圧を両立することができ、CMOSトランジスタとともに製造する場合でもより少ない製造工程により製造することができる半導体デバイスを提供する。

【解決手段】基板P11の表面に形成された第1導電型のベースP14と、ベースの表面に形成された第2導電型のエミッタN23と、ベースの表面においてエミッタと離間して配置され、エミッタから第1の種類のキャリアを受け取るとともに、その第1の種類のキャリアをベースへ注入する、第2導電型のドープ領域N24と、ベースを挟んで、エミッタおよびドープ領域の反対側に形成された、第2導電型のコレクタN15とを備える。

(もっと読む)

半導体装置

【課題】 放熱性を改善したバイポーラトランジスタを有する半導体装置を提供することにある。

【解決手段】 複数のバイポーラトランジスタQuが配列される半導体装置であって、エミッタ配線L3は幅広部と細長部とを有し、細長部におけるバイポーラトランジスタ素子数が、幅広部が配置された配列の外縁に沿う方向に配列されたバイポーラトランジスタ素子数よりも少なくなるように配置する。

【効果】エミッタ配線の寄生抵抗によるエミッタ−ベース間電圧ばらつきを低減する。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

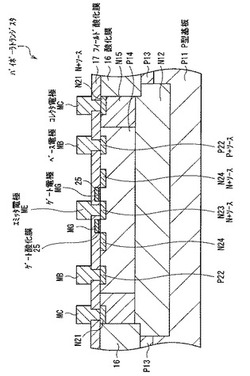

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

半導体装置

【課題】電力破壊を抑制できる半導体装置を提供すること。

【解決手段】ベース領域12の表面に設定されたベースコンタクト領域14において、ベース電極15がベース領域12に接合されている。ベースコンタクト領域14の境界部の下方には、エミッタ領域13と同じ導電型を有するN型領域21がベースコンタクト領域14を包囲するように形成されている。言い換えれば、ベースコンタクト領域14の境界部の下方において、P型のベース領域12およびN型領域21によりPN型の寄生ダイオードが形成されている。

(もっと読む)

高周波増幅器

【課題】回路面積を増加させることなく、動作状態のトランジスタからの発熱を抑制することによって、小型化及び低コスト化を図ることができる高周波増幅器を提供する。

【解決手段】複数の単位トランジスタ3が並列に接続されたトランジスタ列からなり、高周波を増幅する増幅素子と、トランジスタ列の隣り合った単位トランジスタ3のフィンガ間にそれぞれ形成された出力整合回路の回路素子2とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、容量素子の誘電体膜の膜厚がフォトレジストの剥離の際に一部除去され、その容量値がばらつき、耐圧特性が劣化するという問題があった。

【解決手段】本発明の半導体装置では、容量素子1の下部電極8上面に誘電体膜としてのシリコン窒化膜12が形成され、シリコン窒化膜12上面に上部電極15が形成される。上部電極15は、シリコン窒化膜12を保護する多結晶シリコン膜13とシリコン膜14の積層構造から成る。この構造により、フォトレジストの剥離の際等にシリコン窒化膜12の一部が除去され、容量素子1の容量値がばらつきや耐圧劣化が防止される。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体とを備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

高周波半導体装置

【課題】入出力ボンディングワイヤ若しくは入出力伝送線路のインダクタンス分布を調整して、信号位相を同相化し、利得および出力電力を向上させ、かつ各FETセルのアンバランス動作による発振を抑制する。

【解決手段】ゲート端子電極G1〜G10、ソース端子電極S1〜S11およびドレイン端子電極Dを有するFET24と、FETに隣接する入力回路パターン17,出力回路パターン18と、ゲート端子電極G1〜G10と入力回路パターン17とを接続する複数の入力ボンディングワイヤ12,12Lと、ドレイン端子電極Dと出力回路パターン18とを接続する複数の出力ボンディングワイヤ14,14Lとを備え、複数の入力ボンディングワイヤ12,12Lのインダクタンス分布を調整して、入力信号の位相を同相化し、かつ複数の出力ボンディングワイヤ14,14Lのインダクタンス分布を調整して、出力信号の位相を同相化した高周波半導体装置25。

(もっと読む)

半導体デバイス用基板、半導体デバイス装置、設計システム、製造方法、および設計方法

【課題】結晶薄膜の膜質および膜厚を均一にする。

【解決手段】半導体デバイスを形成するためのデバイス用薄膜と、デバイス用薄膜を囲み、デバイス用薄膜の前駆体が結晶に成長することを阻害する阻害部と、前駆体が結晶に犠牲成長することによって形成された犠牲成長部であって、デバイス用薄膜の周辺に阻害部で隔てられて設けられた犠牲成長部と、犠牲成長部の上部を覆い、かつデバイス用薄膜の上部を露出する保護膜を備えた。保護膜はポリイミドであってもよい。

(もっと読む)

n型ベースを有するバイポーラトランジスタ及びその製造方法

【解決手段】ベースコンタクト接続部(12)、エミッタ部(4、5)及びコレクタ部がn層(3)上に配置され、当該n層は、更なるnpnバイポーラトランジスタために用いることができる。当該コレクタ部はエミッタ部に対して側方に配置され、当該エミッタ部及びコレクタ部の少なくとも一方は、当該n層の表面領域上でショットキーコンタクト(14)を備える。 (もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高周波帯域で動作する半導体装置の特性向上と製造コストの低減とを両立した半導体装置およびその製造方法を提供する。

【解決手段】同一の半絶縁性GaAs基板1上に積層された複数の半導体層を用いて複数の半導体素子が形成された半導体装置100であって、FET領域23を用いて形成されたFETと、FET領域23と隣接するHBT領域22を用いて形成されたHBTと、FET領域23とHBT領域22との間である素子分離領域24に設けられ、FET領域23とHBT領域22とを分離する分離溝25とを備え、分離溝25は、内壁面と該内壁面の端部とに接地電位を有する導電性金属層が形成されることにより、素子分離領域24を通過する素子間リーク電流を抑制する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】Siの基板と、基板の上に形成され、結晶成長を阻害する阻害層とを備え、阻害層は、基板の一部を覆う被覆領域と、被覆領域の内部に基板を覆わない開口領域とを有し、さらに開口領域に結晶成長されたGe層と、Ge層上に結晶成長された機能層と、を備える半導体基板を提供する。当該半導体基板において、Ge層は、結晶欠陥が移動できる温度および時間でアニールされることにより形成されてよい。

(もっと読む)

半導体装置

【課題】耐性の低下を抑制するとともに、誤作動を抑制することができる半導体装置を提供すること。

【解決手段】本実施形態の半導体装置1は、一対のトランジスタQ1,Q2が形成された第一導電型の半導体基板13を有する。各トランジスタQ1,Q2は、半導体基板13中に形成された第二導電型のコレクタ領域101と、このコレクタ領域101内に形成された第一導電型のベース領域102と、前記ベース領域102内に形成された第二導電型のエミッタ領域103とを有している。各トランジスタQ1,Q2の各コレクタ領域101は、離間配置されるとともに、各トランジスタQ1,Q2のコレクタ領域101間には、第一導電型の第一領域11が形成されている。各トランジスタQ1,Q2のコレクタ領域101の下部同士は、半導体基板13内に形成された第二導電型の埋め込み層12により接続されている。

(もっと読む)

電力増幅器

【課題】集積回路チップと実装基板との接続の容易性や、放熱性の良好さを維持したままで、各単位セル動作の均一性を確保し、出力段トランジスタの総合的な動作特性を改善する。

【解決手段】

コレクタ電極配線101は、平行する2つの単位セル列用コレクタ電極配線1,2が、その一方の端部で、出力用配線3によって接続されてなり、この出力端とされる一方、単位セル列用コレクタ電極配線1,2の他方の端部は、セル列間接続配線4により相互に接続されたものとなっており、これによって、各単位セルの動作の均一性の改善がなされるものとなっている。

(もっと読む)

複合バイポーラトランジスタ、複合バイポーラトランジスタを用いた半導体デバイスおよび電子機器

【課題】コレクタ‐エミッタ間の飽和電圧を大きくすることなく、熱暴走時の破壊に至るまでの時間を長くする。

【解決手段】エミッタ電極パッド30近傍の領域外では、エミッタ電極パッド30から遠ざかるに連れて島状のベース層22の一辺を短くする一方、上記領域内においては、メッシュエミッタ層23周辺のベース層22および島状のベース層22にエミッタ層23と同じ導電型の拡散層31を形成し、この拡散層31の幅をエミッタ電極パッド30に近づくに連れて広くする。こうして、エミッタ電極パッド30から遠ざかるに連れて、バラスタ抵抗を含むベース抵抗を小さくする。その結果、エミッタ電極パッド30に近いユニットトランジスタほどベース電流が小さくなって電流の集中が緩和され、熱暴走による破壊が起こり難くなる。また、従来のベースにバラスタ抵抗を配置したメッシュエミッタトランジスタよりもコレクタ‐エミッタ間飽和電圧が大きくならない。

(もっと読む)

半導体装置

【課題】 エミッタ-ベース間に発生する順方向電圧の温度特性を利用するバイポーラトランジスタにおいて、素子面積を縮小することを目的とする。

【解決手段】 エミッタ-ベース間に発生する順方向電圧の温度特性を利用するバイポーラトランジスタにおいて、第二の導電型であるベース電極用高濃度不純物領域と、第一の導電型であるコレクタ電極用高濃度不純物領域とを直接に接触させ、不要な分離領域を形成しないことで素子面積を縮小する。

(もっと読む)

半導体装置

【課題】 コレクタ・エミッタ間の耐圧が異なる複数のバイポーラトランジスタを同一基板上に容易に混載可能な技術を提供ことにある。

【解決手段】 同一基板上に高周波バイポーラトランジスタと高耐圧バイポーラトランジスタとを混載した半導体装置において、高周波バイポーラトランジスタと高耐圧バイポーラトランジスタは、同一膜厚のエピタキシャル成長層上に形成されており、また、同一プロセスにより形成された同一の不純物プロファイルを持つ埋め込みコレクタ領域を備えた構造であり、高周波バイポーラトランジスタのベース直下には埋め込みコレクタ領域が存在し、高耐圧バイポーラトランジスタのベース直下には埋め込みコレクタ領域及びSIC領域が存在せずに、高耐圧バイポーラトランジスタのベース領域とコレクタプラグ領域との距離が高周波バイポーラトランジスタの同距離と比べて等しいか大きいことを特徴としている。

(もっと読む)

半導体装置及びその製造方法

【課題】同一のSOI基板上に、MOSトランジスタと、耐圧が十分に確保されたラテラルバイポーラトランジスタとが形成された半導体装置を提供する。

【解決手段】埋め込み酸化膜14上に形成され、p型のチャネル領域60を挟んで形成されるn型のソース領域62s及びn型のドレイン領域62dと、チャネル領域60上にゲート酸化膜52を介して形成されたゲート電極54と、を有するMOSトランジスタ51と、p型のベース領域90を挟んで形成されるn型のコレクタ領域92c及びn型のエミッタ領域92eと、ベース領域90とチャネル幅方向において隣接するp型のベースコンタクト領域89と、ベース領域90上に第2酸化膜82を介して形成されたダミーパターン84と、を有するバイポーラトランジスタ81と、を有する。

(もっと読む)

1 - 20 / 50

[ Back to top ]