Fターム[5J055FX19]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 制御、帰還信号の特徴 (2,064) | 制御、帰還信号はアナログ値であるもの (350)

Fターム[5J055FX19]に分類される特許

81 - 100 / 350

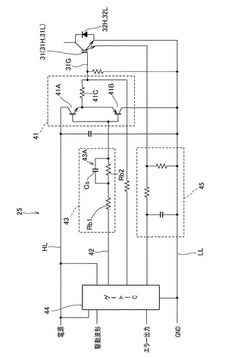

ゲート駆動回路

【課題】トランジスタの遮断遅延を抑制し、絶縁ゲート型トランジスタ(IGBT)の保護動作を向上できるゲート駆動回路を提供する。

【解決手段】絶縁ゲート型トランジスタ31のゲートに、相補型の対のトランジスタ41A,41Bを接続し、対のトランジスタ41A,41Bのベースライン42の電流制御により絶縁ゲート型トランジスタ31を駆動するゲート駆動回路25において、トランジスタ41A,41Bのベースライン42に、ターンオン時にベースライン電流で充電されるコンデンサCsと、ターンオフ時にコンデンサCsに充電された電荷を消費すると共に、絶縁ゲート型トランジスタ31のゲート電位上昇によりトランジスタ41Aのベースに供給された電荷を消費する抵抗Rb2とを並列接続した電荷消費回路43Aを設けた。

(もっと読む)

電流駆動装置

【課題】駆動電圧を駆動回路へ安定的に供給しつつ、部品点数を少なくすることができる電流駆動装置を提供する。

【解決手段】パワートランジスタ3の主端子および制御端子が主端子接続端子13および制御端子接続端子14にそれぞれ接続されることにより、第1の電源4の電圧を所定の目標出力電圧に降圧する3端子レギュレータ10として機能する3端子レギュレータ構成回路12と、第1の電源4より低い電圧を出力する第2の電源6からの電力を用いて、3端子レギュレータ構成回路12がパワートランジスタ3の制御端子に印加する目標出力電圧に対応する制御電圧を設定する電圧設定回路18と、制御端子接続端子14に接続され、第1の電源4から電力が供給されると、3端子レギュレータ構成回路12の出力電圧VOUTが予め定められた電圧VC以下となるようにパワートランジスタ3の制御端子に印加される制御電圧を制御する電圧制限回路19とを備える。

(もっと読む)

アクティブクランプ回路

【課題】アクティブクランプ回路の動作期間を短縮したアクティブクランプ回路を提供する。

【解決手段】実施形態によれば、第1のスイッチ素子と、第1のダイオードと、第1の抵抗と、制御回路と、を備えたことを特徴とするアクティブクランプ回路が提供される。前記第1のダイオードは、前記第1のスイッチ素子の両端にかかる過電圧によりブレークダウンする。前記第1の抵抗は、前記第1のダイオードの電流を検出する。前記制御回路は、前記第1の抵抗の両端の電圧を増幅して前記第1のスイッチ素子の電流を制御する。

(もっと読む)

ランプ波形生成装置および方法

【課題】本発明は、ランプ波形生成装置および方法に関する。

【解決手段】ランプ波形生成装置は、入力信号を用いて基準波形を生成し、負荷の電圧と基準波形の電圧を比較して第1端子が負荷に連結していて第2端子が電源に連結しているスイッチをオンオフさせる駆動制御信号を生成する。このような駆動制御信号に応じてスイッチのオンオフが反復しながらランプ波形が生成される。

(もっと読む)

スイッチングゲートドライバ

【課題】スイッチングゲートドライバにおいて、スイッチング時間を短くして、スイッチング損失を低減すること。

【解決手段】本発明は、IGBT素子のスイッチングゲートドライバであって、IGBT素子のゲート電流を制御するための抵抗部、及び、前記IGBT素子のコレクタ−エミッタ間の電圧に応じて、前記抵抗部の可変抵抗を制御するための制御信号を前記抵抗部に出力する電圧検針部を含むスイッチングゲートドライバを提供する。

(もっと読む)

電子スイッチ装置

【課題】商用交流電源から電子機器への電力供給をオン又はオフするために使用者が操作するスイッチ部品として、各国の安全規格を満たさないスイッチ部品であっても自在に利用可能な電子スイッチ装置を提供すること。

【解決手段】本発明によれば、発振手段が、操作スイッチにより二次側コイルの両端が開放されると発振し、該二次側コイルの両端が短絡されると、一次側コイルのインダクタ値の減少に起因し発振が停止するので、二次側コイルの両端の状態が発振手段からの出力の出力態様に反映される。よって、かかる出力態様に基づくことにより、電力供給路の導通又は遮断を操作スイッチの操作状態に応じて行うことができる。ここで、操作スイッチが接続される二次側コイルは、一次側コイルに対して絶縁されているので、各国の安全規格を満たさないスイッチ部品を操作スイッチとして使用したとしても、操作スイッチを操作する使用者の安全を確保できる。

(もっと読む)

情報処理装置

【課題】 電源遮断機能を有するLSIにおいて、電源遮断をオンオフするときにリーク電流による電流が急激に変化すると電源線にノイズを生ずる。

【解決手段】 情報処理装置であって、回路ブロックと、前記回路ブロックに電源を供給するためのローカル電源線と、電源線と、前記電源線と前記ローカル電源線の間にそのソース―ドレイン経路が設けられる第1のトランジスタとを有し、前記第1のトランジスタは、第1の状態においてはオフ状態に制御され、第2の状態においてはオン状態に制御され、前記第1の状態から前記第2の状態に移行する際に、前記第1のトランジスタは、前記第1のトランジスタのソース―ドレイン経路を流れる電流の変化率が、所定の値を超えないように制御されることを特徴とする。

(もっと読む)

半導体回路、インバータ回路および半導体装置

【課題】簡便な回路構成で過電圧から素子を保護する。

【解決手段】高電圧で抵抗値を制御可能なN1において、ドレイン端子は、抵抗R6を介して出力素子NO5のゲート端子(制御端子)、ソース端子は、NO5のエミッタ端子、そして、ゲート端子は、NO5の出力端子であるコレクタ端子に接続される。入力端子がHiレベルの場合、NO5はオフし、この状態で別に設けられた高圧回路の高電位側にNO5の出力端子を接続し、低電位側にVDD4のマイナス電極を接続すると、NO5のコレクタ−エミッタ間には所望の高電圧が印加される。入力端子をLoレベルに切替えると、PD2はオン、NO5の出力端子には未だ高電圧が印加されているので、N1もオンの状態となり、NO5の電流駆動能力は低い状態ではあるが、オン状態となる。

(もっと読む)

半導体集積回路

【課題】 ゲート酸化膜の信頼性を維持しながら、待機時のリーク電流を抑制でき、回路面積の増加を最小限にでき、欠陥を確実に検出することができる半導体集積回路を実現する。

【解決手段】 論理回路10と電源電圧Vddの供給端子との間にスイッチング回路20を設ける。動作時に、スイッチング回路20のトランジスタMP0のゲートに0Vの電圧を印加し、チャネル領域に電源電圧Vddと同じかまたは僅かに低いバイアス電圧VBを印加することで、トランジスタMP0のしきい値電圧を低くし、その電流駆動能力を大きくする。待機時にトランジスタMP0のゲートに電源電圧Vddと同じ電圧を印加し、ソースに電源電圧より低い電圧を印可し、チャネル領域に電源電圧Vddと同じかまたはそれより高いバルクバイアス電圧VBを印加し、トランジスタMP0のドレイン電流を最少化することにより、論理回路10の電流経路を遮断し、リーク電流の発生を抑制する。

(もっと読む)

電流制限回路

【課題】従来技術の電流制限回路では、温度変化が生じた場合に出力トランジスタの電流を精度良く制御することができないという問題があった。

【解決手段】本発明にかかる電流制限回路は、高電位側電源11から負荷12に流れる電流を制御する出力トランジスタMN0と、出力トランジスタMN0に流れる電流に応じた電流が流れるトランジスタMN1と、トランジスタMN1に直列に接続されたセンス抵抗18と、センス抵抗18に流れる電流とセンス抵抗18の抵抗成分とによってセンス抵抗18の両端に生じた電位差を検出する電位差検出部と、電位差検出部に対して定電流を供給する定電流源と、電位差と定電流とによって生成された制御電圧に基づいて出力トランジスタMN0の導通状態を制御する制御部と、を備え、センス抵抗18は、電位差検出部を囲むように配設される。

(もっと読む)

圧電アクチュエータ用のドライバ

【課題】複数の半導体デバイスを使用する電池駆動のドライバと同程度に効率的な圧電アクチュエータ用のシングルチップドライバを提供する。

【解決手段】圧電アクチュエータ用のドライバは、単一の半導体デバイスとしてパッケージされる、好ましくは単一の半導体ダイの上に形成されるパルス幅変調器33および出力増幅器34を含む。ドライバは、好ましくはプログラム可能な利得を有する出力増幅器34に電力を供給する第1の昇圧コンバータを含む。第1の昇圧コンバータのスイッチングトランジスタのゲートを駆動するための第2の増幅器は、第2の昇圧コンバータによって電力が供給される。圧電アクチュエータ22は、電池駆動の電子デバイスのキーボードまたはディスプレイに対して触覚フィードバックを提供する。

(もっと読む)

レベルシフト回路

【課題】消費電力低下および速度向上が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路2は、第1入力端子11、第2入力端子12、第1出力端子21、第2出力端子22、第1PMOSトランジスタ31、第2PMOSトランジスタ32、第1NMOSトランジスタ41、第2NMOSトランジスタ42、第1ブートストラップ回路51および第2ブートストラップ回路52を備える。第1ブートストラップ回路51は、第1充電用スイッチ511,第1転送用スイッチ512,第1容量部513および第1インバータ回路514を含む。第2ブートストラップ回路52は、第2充電用スイッチ521,第2転送用スイッチ522,第2容量部523および第2インバータ回路524を含む。

(もっと読む)

プリエンファシス機能を含む出力回路と半導体装置

【課題】プリエンファシス機能を有する出力回路において、デエンファシス時における差動出力信号のコモンモード電圧のプリエンファシス時のコモンモード電圧からの変動を抑制する。

【解決手段】入力信号とその相補信号とを差動入力して差動出力し、差動出力信号のうち高電位側の出力信号にデエンファシスをかける際に、当該デエンファシス電流を供給するトランジスタ(N3、N4)に流れる電流を絞る回路(N5、N6、R3)を備え、デエンファシス時の前記出力信号のハイレベルの前記出力信号のプリエンファシス時のハイレベルからの変化量を縮減させ、デエンファシス時の前記差動出力信号のコモンモード電圧をプリエンファシス時のコモンモード電圧に近づける。

(もっと読む)

ゲート・プルダウンを備えたMOSFET

スイッチングタイプのDC−DCパワー・コンバータのMOSFETメインスイッチ・トランジスタ(102)のドレインとゲートとの間にプルダウンMOSFET(110)が結合される。プルダウンMOSFET(110)のゲートは、キャパシタ118によってメインスイッチ・トランジスタ(102)のドレインに結合され、抵抗(120)によってメインスイッチ・トランジスタ(102)のソースに接続される。プルダウンMOSFET(110)は、メインスイッチ・トランジスタ(102)にわたる電圧降下への容量性結合によって動作され、ミラー効果によるメインスイッチ・トランジスタ(102)の意図しないターンオンを避ける又は低減するため、メインスイッチ・トランジスタ(102)のゲートをそのソース電位にまたはその近辺に保持するために用いられ得る。

(もっと読む)

(もっと読む)

レベルシフタ誤動作防止回路

【課題】本発明は、レベルシフタ誤動作防止回路に係り、レベルシフタの誤動作を、信号伝達の過大な遅延と消費電流の増大とを招くことなく防止することにある。

【解決手段】伝達すべき信号に応じて駆動されるN型トランジスタ30と、N型トランジスタ30の出力に応じて駆動されるP型トランジスタ32と、P型トランジスタ32を駆動するために設けられるプルアップ抵抗34と、を有する、基準電圧が互いに異なる2つの回路系の間で信号伝達を行うレベルシフタ16の誤動作を防止する回路において、2つの回路系の基準電圧が相対変位した際、N型トランジスタ30に存在する寄生容量36へプルアップ抵抗34を介して充電電流が供給される前に、その寄生容量36へ充電電流を供給する急速充電手段を設ける。

(もっと読む)

ドライバ回路

【課題】差動入力信号の振幅中心電圧が高い場合でも、差動出力信号の振幅変動やジッタを抑制することができるドライバ回路を提供することである。

【解決手段】本発明にかかるドライバ回路は、トランジスタM1と、トランジスタM1のソースと電源端子との間に接続された負荷素子R1と、トランジスタM1とカレントミラー回路を構成するトランジスタM2と、入力された差動入力信号に応じた差動出力信号を出力すると共に、トランジスタM2によりソースにバイアス電流が供給される一対のトランジスタを備える差動対と、トランジスタM2のソースと電源端子との間に接続された負荷素子R2と、非反転入力端子がトランジスタM1のソースと接続され、反転入力端子がトランジスタM2のソースと接続され、出力が差動対を構成する一対のトランジスタのバックゲートに接続されたオペアンプAMP1と、を有する。

(もっと読む)

時定数回路、スイッチ回路、DC/DCコンバータ及び表示装置

【課題】単調に減衰するだけの出力電圧特性に比べて、急峻に減衰した後に緩やかに減衰する出力電圧特性が得られる時定数回路等を提供する。

【解決手段】時定数回路10は、抵抗素子111と容量素子121との並列回路131,…が第一の端子14と第二の端子15との間に複数直列に接続されて成る直並列回路16と、第二の端子15に接続された第三の端子17と第四の端子18との間に接続された分圧用抵抗素子19と、を備えている。並列回路131は抵抗素子111と容量素子121とから成り、並列回路132は抵抗素子112と容量素子122とから成り、・・・、並列回路13nは抵抗素子11nと容量素子12nとから成る。nは、並列回路131〜13nの数であり、2以上の整数である。

(もっと読む)

駆動装置、及び表示装置

【課題】並列接続された複数の出力アンプ回路において所望の駆動能力を実現することができる駆動装置、及び表示装置を提供すること。

【解決手段】本発明に係る駆動装置(ソースドライバ1)は、並列接続された複数の出力アンプ回路10と、複数の出力アンプ回路10に、バイアス電圧供給源25からバイアス電圧を供給するバイアス配線(幹バイアス配線22)と、複数の出力アンプ回路10に、電源電圧供給源35から電源電圧を供給する電源配線31と、複数の出力アンプ回路10に供給される電源電圧とバイアス電圧との差が所望となるように、バイアス電圧にオフセット電圧を重畳する補正手段(バッファ26)とを備えた。

(もっと読む)

ターンオフ制御を有する電力トランジスタおよびその動作方法

回路が、電力トランジスタ48、駆動制御回路16、可変クランプ回路24、およびターンオフ制御回路18を有する。電力トランジスタが、第1電源端子に接続される第1電流電極、回路の出力50としての第2電流電極、および制御電極を有する。駆動制御回路が、電力トランジスタの制御電極に接続される出力を有して、回路のアクティブモードの間、電力トランジスタを制御する。可変クランプ回路は、回路の出力と第1電源端子との間に接続される。ターンオフ制御回路は、可変クランプ回路に接続され、回路をアクティブモードから非アクティブモードに移行する間、可変クランプ回路のクランプレベルを選択する。  (もっと読む)

(もっと読む)

スイッチング回路およびスイッチング回路の制御方法

【課題】 スイッチング損失を抑制しつつ、広い帯域に存在する高調波周波数成分を低減できるスイッチング回路およびスイッチング回路の制御方法の提供。

【解決手段】 スイッチング回路1は、狙いとするノイズ低減帯域を2つの帯域に分割して両帯域の高調波周波数成分を小さくする最適波形をそれぞれ生成し、生成した2つの最適波形を1パルス毎に切り替えてパワートランジスタM1を駆動する規範電圧波形生成部3を備える。

(もっと読む)

81 - 100 / 350

[ Back to top ]