Fターム[5J055FX19]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 制御、帰還信号の特徴 (2,064) | 制御、帰還信号はアナログ値であるもの (350)

Fターム[5J055FX19]に分類される特許

21 - 40 / 350

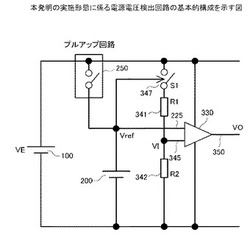

電源電圧検出回路

【課題】低電圧状態を検出し、システムへの通知やシステムの停止等を行う電源電圧検出回路において低電源電圧時の誤動作を回避する電源電圧検出回路を提供する。

【解決手段】基準電圧Vrefを生成する回路200の出力にプルアップ回路250を設け、基準電圧Vrefを生成する回路200を電源電圧VE(100)までプルアップする。さらに、R1(341),R2(342)から成る検出抵抗に直列にスイッチS1(347)を設け、基準電圧Vrefを生成する回路200によって、上記スイッチS1(347)をオン/オフする。そうしておいて低電源電圧時に上記プルアップ回路250により基準電圧Vref(225)を上記電源電圧VE(100)までプルアップさせると共に、上記スイッチS1(347)をオフし分圧値VI(345)を強制的に低下させることで、Vref>VIの状態を保持し、比較器330からの誤信号出力を回避する。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

ゲートドライブ回路

【課題】ターンオン時のスイッチング特性が変動せず、電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体かなるスイッチング素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲートドライブ回路であって、制御回路とスイッチング素子のゲートとの間に接続されたコンデンサC1と抵抗R1とからなる並列回路と、並列回路にコンデンサC2とスイッチング素子Q2と抵抗R2からなる直列回路がさらに並列接続され、コンデンサC2とスイッチング素子Q2との接続点にダイオードD1のアノードが接続され、ダイオードD1のカソードとスイッチング素子Q2のゲートはスイッチング素子Q1のソースに接続され、制御信号のオフ信号に対してスイッチング素子Q1ゲートを負電位にバイアスする。

(もっと読む)

アクティブクランプ回路

【課題】アクティブクランプ動作期間を短縮するとともにESD耐量を向上させたアクティブクランプ回路を提供する。

【解決手段】実施形態によれば、第1のスイッチ素子と、第1のダイオードと、第1の抵抗と、第1および第2の制御回路と、を備えたことを特徴とするアクティブクランプ回路が提供される。前記第1のダイオードは、前記第1のスイッチ素子の両端にかかる過電圧によりブレークダウンする。前記第1の抵抗は、前記第1のダイオードの電流を検出する。前記第1の制御回路は、前記第1の抵抗の両端の電圧を増幅して前記第1のスイッチ素子の電流を制御する。前記第2の制御回路は、前記第1の抵抗の両端の電圧に応じて前記第1のスイッチ素子の導通を制御する。

(もっと読む)

電流駆動型半導体スイッチの駆動回路

【課題】従来の電流駆動型半導体スイッチ8の駆動回路は、駆動回路における電力損失を抑制するためにスイッチやスイッチを制御するための手段が必要となり部品点数が増える。

【解決手段】電源1と電流駆動型半導体スイッチ8のベース又はゲート端子の間に接続される負の温度特性を有する第1の可変抵抗10と、前記電流駆動型半導体スイッチ8のコレクタ又はドレイン電流による動作損失により過熱される熱伝導部11を備え、前記第1の可変抵抗10を前記熱伝導部11により熱が供給されるように配置する。

本発明により、簡単な構成で部品点数を増やすことなく駆動回路における電力損失を抑制することができる。

(もっと読む)

半導体素子駆動装置及び方法

【課題】並列に駆動される複数の半導体素子の特性差によって生じる、ターンオンやターンオフ時のスイッチングにおける電流の偏りを緩和すること。

【解決手段】電圧変換器14は、IGBT13−1乃至13−3の各々のエミッタセンス電流を電圧信号に変換する。平均値演算器17や誤差演算器18等の演算器は、LPF15から出力される、IGBT13−1乃至13−3の各々に対応する電圧信号の平均値を求め、それぞれの電圧信号についての平均値に対する誤差を演算する。PWM波形生成部11は、IGBT13−1乃至13−3の各々を駆動するための駆動信号(パルス信号)を出力する。差動増幅器12の各々の駆動信号を、当該IGBT13−1乃至13−3の各々に対応する誤差に基づいて調整して、当該IGBT13−1乃至13−3の各々に供給する。

(もっと読む)

負荷駆動回路

【課題】簡単な構成で負荷オープン状態を検出することができる負荷駆動回路を提供する。

【解決手段】電源端子T1に入力される入力電圧Vinよりも低い基準電圧V1と出力端子T2の電圧Voutとを比較する第1のコンパレータ8と、スイッチング素子2がオフ状態で、且つ負荷オープン状態である場合に、出力端子T2の電圧Voutを基準電圧V1よりも高く、且つ入力電圧Vinよりも低いclamp電圧にクランプするクランプ回路7とを備えることにより、第1のコンパレータの出力によって、負荷オープン状態を検出する。また、入力電圧Vinよりも低く且つclamp電圧よりも高い基準電圧V2と出力端子T2の電圧Voutとを比較する第2のコンパレータ9を備えることにより、第1のコンパレータ及び第2のコンパレータ9の出力によって、負荷オープン状態と出力天絡状態とを検出する。

(もっと読む)

半導体スイッチ及び無線機器

【課題】高周波特性を改善した半導体スイッチ及び無線機器を提供する。

【解決手段】スイッチ部と、駆動回路と、電源回路と、を備えた半導体スイッチが供給される。前記スイッチ部は、共通端子と複数の高周波端子との接続を切り替える。前記駆動回路は、端子切替信号に基づいて前記スイッチ部に制御信号を出力する。前記電源回路は、温度に応じて変化する基準電位基づいて、前記制御信号の電位であって温度制御された第1の電位を生成して前記駆動回路に出力する。

(もっと読む)

ゲート駆動回路

【課題】過電流や短絡発生時に絶縁ゲート型トランジスタへの遮断の遅延を抑制し、安全に絶縁ゲート型トランジスタを保護できるゲート駆動を提供する。

【解決手段】対を成すNPNトランジスタ15、PNPトランジスタ17によるトーテムポール回路9に駆動信号が入力され、回路9の出力が絶縁ゲート型トランジスタ3のゲート3Aに接続され、トランジスタ3のゲート3Aの電位を下げて保護動作をする保護回路11が備えられたゲート駆動回路1であって、トーテムポール回路9のトランジスタ15、17ごとに独立して設けられて駆動信号をベース15A、17Aに入力するベースライン29A、29Bと、保護回路11の保護動作の間、トーテムポール回路9の上アーム側のトランジスタ15のベース電位を下げる電位強制低下回路13と、を備える。

(もっと読む)

電源回路

【課題】高速スイッチング素子である電圧駆動型トランジスタ(MOSFET)のターンオン・オフ時の電圧変化(dV/dt)と電流変化(di/dt)を緩和して、ノイズとサージ電圧の発生を抑制する電源回路を提供する。

【解決手段】トランス2に流れる電流をスイッチングさせるためのMOSFET1のゲート抵抗値を、スイッチング期間内で、MOSFET1のドレイン電圧Vdsの変化の検出と共に切り替える、MOSFET1のゲート電圧Vgは、MOSFET1のゲート電圧の最大定格Vgmax以下とする。

(もっと読む)

電力変換装置

【課題】本発明の課題は、電力変換装置における温度検出素子の時間変化率を検出し、温度上昇の事前予測によりフェールセーフをかけることで、発熱半導体素子の発熱抑制とモジュールケースの冷却構造最適化を実現することである。

【解決手段】上記課題を解決するために、前記半導体素子のモジュールケースまたは素子自体の温度の時間変化率を検出する検出手段と、素子のゲート抵抗値を可変にする抵抗可変回路とを設け、前記検出温度の時間変化率が所定の設定値以上になったと判断されたときは、ゲート抵抗値を前記抵抗可変回路により低減することを特徴とする電力変換装置を提供する。

(もっと読む)

ドライブ回路

【課題】ベース電流による電力損失を低減するドライブ回路を提供する。

【解決手段】BJT21のベース端子にベース電流を供給するドライブ回路1は、BJT21のベース電流を生成するベース回路部30と、制御端子に供給される制御電圧に基づき、ベース電流を生成するための駆動電圧をベース回路部30に供給するドライブ部10と、BJT21のベース端子とBJT21のエミッタ端子との間に発生する第1のベース−エミッタ間電圧Vbeを検出し、検出した第1のベース−エミッタ間電圧Vbeに応じたベース電流をBJT21に供給するように制御電圧を制御して、ドライブ部10に供給するベース電流制御部50とを備える。

(もっと読む)

駆動装置

【課題】電圧駆動型素子を駆動状態と非駆動状態の間で遷移させるときの遷移期間において、電圧駆動型素子のゲート電圧を柔軟に制御するための技術を提供する。

【解決手段】駆動装置1は、電圧駆動部3と電流駆動部4を備えている。電圧駆動型素子2を駆動状態と非駆動状態の間で遷移させるときの遷移期間のうちの一部の区間では、電圧駆動部3を利用した電圧駆動型素子2のゲート電圧Vgの制御が停止され、電流駆動部4を利用した電圧駆動型素子2のゲート電圧Vgの制御が実行されるように構成されている。

(もっと読む)

スイッチング回路

【課題】大電流を制御可能なスイッチング回路において、部品点数を少なくしたコンパクトな構成にて、スイッチング損失を低減するとともにサージ電圧を抑制することができるスイッチング回路を提供する。

【解決手段】高電圧ラインL1と低電圧ラインL2との間においてMOSFET30,31,32,33が並列接続され、ゲート抵抗50,51,52,53の第1の端子がMOSFET30〜33のゲート電極に接続されている。MOSFET30,31,32,33毎に設けられたゲート抵抗50,51,52,53の第2の端子がゲート電圧印加ラインL3を介してパルス発生回路60と接続されている。パルス発生回路60により、ゲート抵抗50〜53を介してMOSFET30〜33のゲート電極にパルス状のゲート電圧が印加される。ゲート電圧印加ラインL3と高電圧ラインL1との間の1箇所にコンデンサ70が接続されている。

(もっと読む)

リンギング抑制回路

【課題】より簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、NチャネルMOSFET7を接続し、制御回路14は、伝送線路3を介して伝送される差動信号のレベルがハイからローに変化したことを検出すると、NチャネルMOSFET7を一定期間オンさせる。すなわち、差動信号のレベルが遷移する期間にNチャネルMOSFET7が導通することで信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーを吸収させてリンギングの発生を確実に抑制する。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

ゲート駆動回路

【課題】 簡便な回路構成で、高速に動作するゲート駆動回路を提供することである。

【解決手段】 パワー半導体素子のゲート端子に正電圧を印加するためのNPNトランジスタと、パワー半導体素子のゲート端子に負電圧を印加するためのPNPトランジスタと、NPNトランジスタと、PNPトランジスタとに直列に接続された遮断用抵抗器と、遮断用抵抗器に、正極がパワー半導体素子のゲート端子側となるように並列に接続された遮断用抵抗器切換え半導体スイッチとを備えたゲート駆動回路である。

(もっと読む)

半導体デバイス駆動回路及び半導体装置

【課題】電源電圧が変動しても半導体デバイスのオン動作及びオフ動作を安定して駆動できる半導体デバイス駆動回路を得る。

【解決手段】ドライブ回路10は、入力回路11より得られる制御信号S11に基づき、インバータG4から電源電圧VCCにより決定される“H”(オンレベル)、あるいは接地電圧GNDにより決定される“L”(オフレベル)の出力電圧VOUT1を駆動信号として半導体デバイスQ1のゲートに出力する。基準電源部14は抵抗R1及びR2の直列接続により、電源電圧VCC,接地電圧GND間の電位差を所定の分圧比率(抵抗R1及びR2による抵抗比)で分圧して得られる電圧が基準電圧VREF1として得られる。バッファ回路8は基準電圧VREF1により決定される基準信号となる出力電圧VOUT2を半導体デバイスQ1のソースに付与する。

(もっと読む)

ゲートタイミング制御回路

【課題】半導体スイッチ,負荷電流,温度,主回路構成等によるサージ電圧の波形に応じて半導体スイッチの動作タイミングを調整することなく、各半導体スイッチの電圧分担を均等化させる。

【解決手段】直列接続された複数の半導体スイッチA,Bに出力されるゲート信号のタイミングを調整するゲートタイミング制御回路3において、コンパレータ4,4により、各半導体スイッチA,BのVce検出(A),(B)と、予め設定されたしきい値とを比較してVce検出における立ち上がりのタイミングを示すVce信号(A),(B)を出力する。そして、時間差制御部8において、ゲート信号に基づいて、前記各Vce信号(A),(B)の変化のタイミングが整合するように生成されたゲート出力(A),(B)をゲートドライバ2に出力する。

(もっと読む)

絶縁ゲート型スイッチング素子のゲートの電位を制御する半導体装置、及び、回路

【課題】 絶縁ゲート型スイッチング素子のゲートの電位を制御する半導体装置であって、低速スイッチング用と高速スイッチング用とで共通して使用可能な半導体装置を提供する。

【解決手段】 絶縁ゲート型スイッチング素子のゲートの電位を制御する信号を出力する半導体装置であって、第1信号出力端子を有しており、第1電位と第1電位よりも高い第2電位の間で変動する基準信号の入力を受けるか、または、内部で前記基準信号を生成することが可能であり、前記基準信号が第1電位にあるときには第3電位となり、前記基準信号が第2電位にあるときには第3電位よりも高い第4電位となる信号を第1信号出力端子に出力する第1動作と、前記基準信号が第1電位にあるときには第4電位となり、前記基準信号が第2電位にあるときには第3電位となる信号を第1信号出力端子に出力する第2動作とを切り換えて実行することができる。

(もっと読む)

21 - 40 / 350

[ Back to top ]