国際特許分類[H05K3/46]の内容

電気 (1,674,590) | 他に分類されない電気技術 (122,472) | 印刷回路;電気装置の箱体または構造的細部,電気部品の組立体の製造 (64,965) | 印刷回路を製造するための装置または方法 (27,705) | 多重層回路の製造 (6,503)

国際特許分類[H05K3/46]に分類される特許

31 - 40 / 6,503

貫通電極付き配線基板の製造方法

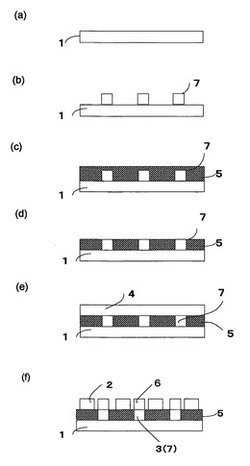

【課題】微細な貫通電極孔を備え且つ熱伝導性の高いガラス製インターポーザの製造方法を提供することを目的とした。

【解決手段】少なくとも、金属製の支持基板1上に金属凸部7を形成する工程と、金属製の支持基板1及び金属凸部7をSiO2を主成分とする絶縁層5で被覆する工程と、金属凸部7を被覆する絶縁層5を除去し金属凸部7表面を露出させる工程と、絶縁層5と露出した金属凸部7の上に第一の導体層4を設ける工程と、第一の導体層4に金属凸部を含むパターン形成を行う工程と、をこの順に有することを特徴とする貫通電極付き配線基板の製造方法である。

(もっと読む)

金属箔張基板製造用仮基板および金属箔張基板の製造方法

【課題】金属箔張基板を製造するのに用いられる仮基板であって、金属箔のシワの発生が抑制された高品質な金属箔張基板を製造可能な金属箔張基板製造用仮基板、および高品質な金属箔張基板を効率よく製造する方法を提供すること。

【解決手段】金属箔張基板製造用仮基板1は、プリプレグを硬化させてなる仮基板本体11と、仮基板本体11上に配置された下地層12と、下地層12を介して仮基板本体11上に設けられ、下地層12の平面視の大きさより大きな金属箔13と、を有し、金属箔13の一部をビルドアップ配線層9等の他の基板に移転させて配線基板(金属箔張基板)5を製造するのに用いられる仮基板であって、仮基板本体11は、経糸/緯糸の1インチ当たりの質量比が0.8〜1.35であり、かつ、単位面積当たりの質量が208〜260g/m2であるガラス織布を含んでいる。

(もっと読む)

多層基板

【課題】高性能な高周波伝送特性を実現したうえで、ビルドアップ接続の簡単化を図ることができる。

【解決手段】第1及び第2の誘電体層10,11の層面側の中心位置の周囲に所定位置ずらして放射状に配置した4個のビルドアップ接続部18を設けた接続用導体パターン17を有する高周波線路16を形成して、この第1及び第2の誘電体層10,11間に該第1及び第2の誘電体層10,11のビルドアップ接続部18がビルドアップ接続される4個のビルドアップ接続部18を所定角度ずらせて放射状に配置した接続用導体パターン17を有した第1乃至第3の中間誘電体層12〜14を積層配置してビルドアップ接続するように構成したものである。

(もっと読む)

セラミック回路基板の製造方法

【課題】 セラミック積層基板と導体の焼収縮差により焼成後に導体との間に生じていた空隙形成を防ぐことにより、セラミック積層基板と導体双方の密着性を高めることができるセラミック積層回路基板の製造を可能とすることを目的とする。

【解決手段】 ガラス粒子およびアルミナ粒子からなるセラミックス原料粉末、焼結助剤、可塑剤等を溶剤によりスラリー化してグリーンシートを形成するセラミックス回路基板の製造方法であって、低融点ガラスと、有機物からなるフィラーを添加することを特徴とする。前記フィラーは、例えばアクリル樹脂またはメラミン樹脂とする。

(もっと読む)

部品内蔵配線板の製造方法

【課題】複数種の部品が混載で埋設、実装される場合であっても大きな生産性と低コストを実現できる部品内蔵配線板の製造方法を提供すること。

【解決手段】第1の絶縁板上に、端子パッドを有する半導体チップと端子パッドに電気的に接続されたグリッド状配列の表面実装用端子とを備えた半導体素子を実装するための第1のランドと、表面実装用のチップ部品を実装するための第2のランドとを形成し、第1、第2のランド上にクリームはんだを適用し、クリームはんだを介して第1、第2のランド上に半導体素子およびチップ部品をそれぞれ載置し、クリームはんだをリフローすべく加熱して、半導体素子およびチップ部品を第1、第2のランドにそれぞれ接続し、第1の絶縁板とは別の第2の絶縁板中に、第1、第2のランドにそれぞれ接続された半導体素子およびチップ部品を埋め込むように、第1の絶縁板に積層状に第2の絶縁板を一体化する。

(もっと読む)

樹脂組成物

【課題】硬化時における反りを低減でき、絶縁信頼性に優れ、半導体素子の表面保護膜、層間絶縁膜、プリント配線板用保護絶縁膜、層間絶縁膜などの材料として好適に使用できる樹脂組成物、樹脂組成物を用いた樹脂フィルム及びそれらを用いた配線板を提供すること。

【解決手段】本発明の樹脂組成物は、(A)テトラカルボン酸二無水物成分とポリエーテル構造及び少なくとも2つの末端アミン構造を有するジアミン成分とを重合させて得られた高分子化合物と、(B)酸化防止剤と、を含有し、高分子化合物は、分子内にエステル構造及びスルホン酸基を有しないことを特徴とする。

(もっと読む)

コンデンサモジュール内蔵配線基板

【課題】製造コストが安く、接続信頼性に優れたコンデンサモジュール内蔵配線基板を提供すること。

【解決手段】コンデンサモジュール内蔵配線基板10は、半導体チップ21を表面実装するための複数の端子パッド44が基板主面51上に設けられるとともに、BGA用パッド48が基板裏面52上に設けられている。ガラス基板102とそのガラス基板102の第2面106上に実装される複数のチップコンデンサ103とによってコンデンサモジュール101が構成される。コンデンサモジュール101は、基板主面51上に設定された半導体チップ搭載領域23の直下にて、チップコンデンサ103を実装していない第1面105側を基板主面51側に向けた状態で内蔵される。

(もっと読む)

半導体パッケージ及びその製造方法

【課題】本発明は、半導体パッケージ及びその製造方法に関する。

【解決手段】本発明の実施形態による半導体パッケージは、第1側面を有する電気素子と、電気素子が位置するキャビティを有するコア基板と、を含み、コア基板は、コア基板の厚さ方向に対して傾き、キャビティを定義する第2側面を有する。

(もっと読む)

半導体装置内蔵基板モジュール及びその製造方法

【課題】特定の機能を備えた半導体装置の高集積化及び小型化を図ることができるとともに、部品実装に係る製造工程の簡略化や効率化を図ることができる半導体装置内蔵基板モジュール、及び、その製造方法を提供する。

【解決手段】半導体装置内蔵基板モジュール10は、コア基板21に、ウエハレベルCSP構造の半導体装置30が内蔵された基板装置部20と、所望の機能を有する機能部であるコイル部50とが、一体的に形成されるとともに、これらが、積層配線を構成する配線層やビア、貫通電極を介して、相互に電気的に接続された構成を有している。

(もっと読む)

多数個取りセラミック基板およびセラミック基板

【課題】 絶縁層が光の反射層となることができ、個片のセラミック基板への分割も容易な多数個取りセラミック基板および個片のセラミック基板を提供することにある。

【解決手段】 複数の基板領域2を有する母基板1と、母基板1の上面に、基板領域2の境界に沿って設けられた分割溝3とを備えており、母基板1が、第1のセラミック焼結体からなる絶縁層1aと、第1のセラミック焼結体よりも結晶化温度が低い第2のセラミック焼結体からなる拘束層1bとが交互に、最上層が絶縁層1aとなるように積層されて形成されているとともに、母基板1の上面に分割溝3に沿って、第2のセラミック焼結体からなる帯状拘束層4が付着している多数個取りセラミック基板9である。帯状拘束層4により、分割溝3が形成された部分における絶縁層1aの収縮を抑制して分割溝3の変形を抑制できる。そのため、分割が容易な多数個取りセラミック基板9を提供できる。

(もっと読む)

31 - 40 / 6,503

[ Back to top ]