Fターム[5E346DD11]の内容

多層プリント配線板の製造 (97,916) | 各層形成の方法 (10,210) | 導体層形成の方法 (4,026)

Fターム[5E346DD11]の下位に属するFターム

導体性シート等、導電材の接着 (1,288)

塗布 (582)

気相 (344)

メッキ (1,757)

ワイヤ布線 (9)

Fターム[5E346DD11]に分類される特許

1 - 20 / 46

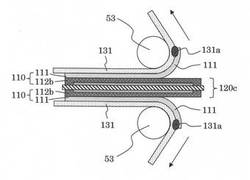

真空積層装置及びこれを用いた絶縁層の形成方法

【課題】支持ベースフィルムに絶縁樹脂層が形成された絶縁樹脂フィルムを配線回路基板に積層し、支持ベースフィルムを剥離して配線回路基板上に絶縁層を形成する積層装置のランニングコストを低くし、効率的かつ品質的に安定して支持ベースフィルムの剥離を可能にする。

【解決手段】上下1対の搬送フィルム131によって連結された一貫ラインの積層装置で、搬送フィルム巻取りユニットに超音波溶着機構を備える。基板は上下の搬送フィルム131で挟まれた状態で処理して絶縁層112bを積層する。配線回路基板120c上に残った、支持ベースフィルム111と搬送フィルム131とを超音波溶着にて接合し、搬送フィルム巻き取りガイドローラー53により、超音波溶着部131aを起点として、搬送フィルム131と支持ベースフィルム111とを配線回路基板120cから剥離する。

(もっと読む)

コンデンサ素子及びコンデンサ内蔵基板

【課題】コンデンサ内蔵基板に生じるインダクタンスを小さくすることが可能なコンデンサ素子、及び該コンデンサ素子を具えたコンデンサ内蔵基板を提供する。

【解決手段】本発明に係るコンデンサ素子は、第1電極層11と第2電極層12との間に誘電体層13が介在したコンデンサ素子1であって、第1電極層11は、第2電極層12側の表面111の一部が該第2電極層12によって覆われ、第1電極層11が金属箔により形成される一方、第2電極層12が金属薄膜又は金属箔により形成されている。本発明に係るコンデンサ内蔵基板は、前記コンデンサ素子1と絶縁基板2とを具え、該絶縁基板2内にコンデンサ素子1を埋設することにより絶縁基板2にコンデンサ素子1が内蔵されている。

(もっと読む)

チップインダクタ内蔵配線基板

【課題】チップインダクタ内蔵配線基板において、チップインダクタの漏れ磁束に起因したノイズとしての高周波電流の配線層への影響を低減し、配線基板に実装された他の回路部品や電子部品に対する電位変動や電源供給の変動を抑制して、これら回路部品及び電子部品の動作を良好に保持する。

【解決方法】相対向して配置される一対の第1の配線層及び第2の配線層と、前記第1の配線層及び前記第2の配線層間に配設されてなる絶縁層と、前記絶縁層内に配設されるとともに、前記第1の配線層に実装されてなるチップインダクタとを具え、前記第2の配線層は安定電位を供給する配線層であり、前記第2の配線層の前記チップインダクタと相対向する領域において非連続の複数の開口部が形成され、前記領域が前記非連続の複数の開口部によって画定されるようにして、チップインダクタ内蔵配線基板を構成する。

(もっと読む)

部品集合体

【課題】高精度に、かつ、容易に主基板に内蔵することのできる部品集合体を提供する。

【解決手段】線膨脹係数αCが小さい複数のコンデンサ52を配列して内蔵する集合体基板の部品内蔵層の線膨脹係数αBが、集合体基板が埋設される部品内蔵基板1の部品内蔵層5の線膨張係数αAより小さく形成されているため、例えばリフローにおける加熱や、雰囲気の温度変動により各部材が膨脹することにより生じる応力を緩和することができ、各部材間における電気的な接続部分に応力が集中することにより各接続部分に不具合が生じることを防止でき、コンデンサ52に対する電気的接続の信頼性の向上を図ることができる。

(もっと読む)

電子素子内蔵型印刷回路基板

【課題】コア基板のキャビティ加工方法を提供する。

【解決手段】本発明に係るコア基板のキャビティ加工方法は、コア基板の一面に回路パターンにより区画される第1加工領域を形成する工程と、コア基板の他面に回路パターンにより区画される第2加工領域を形成する工程と、コア基板の一面から第1加工領域を全て除去してキャビティを加工する工程と、を含む。

(もっと読む)

微細配線パッケージ

【課題】電子部品の端子面を均一な高さに設定することにより、各端子に接続する導通孔による端子と配線との電気的接続を容易し、各部の位置ずれ等を生じにくい微細配線パッケージを得る。

【解決手段】一方の面に搭載した、各々複数の端子を有する高さの異なる複数の電子部品(12、14、16)と、電子部品の端子の表面を所定の平面上に揃えるように、これらの電子部品を、電極端子形成面が露出し且つ電子部品の側面の一部を覆うように、封止する封止樹脂(22)と、電子部品及び封止樹脂の表面上に形成した、電子部品の端子に電気的に接続する導体層(44)と、電子部品の電極端子形成面及び封止樹脂上に形成された配線層を覆う絶縁樹脂層(24)と、封止樹脂と絶縁樹脂層との間に形成した補強板(46)とを含む。

(もっと読む)

セラミック多層基板の製造方法

【課題】複雑な形状のキャビティや粗密を有するセラミック多層基板を歪みを生じることなく製造できるセラミック多層基板の製造方法を得ること。

【解決手段】グリーンシートが圧着された積層体3、4a〜4dを形成する積層体形成工程と、積層体3、4a〜4dの各々を、グリーンシートと同じ組成のペースト5で任意の積層方向に接着して、積層体の集合体を形成する接着工程と、積層体の集合体を乾燥させて、揮発成分をペースト5から除去する工程と、積層体の集合体を焼成する工程とを有する。

(もっと読む)

電圧変換モジュール素子、及び電圧変換モジュール

【課題】電圧変換用ICの雑音除去性能を劣化させることなく、電圧変換用ICを多層配線板中に内蔵させた、新規な構成の電圧変換モジュール素子及び電圧変換モジュールを提供する。

【解決方法】多層配線板における複数の配線パターンの、内方に位置する配線パターンの一つに実装された電圧変換を行うための電圧変換用ICと、 前記複数の配線パターンの少なくとも一つにおいて、前記電圧変換用ICの入力側における入力端子及びグランド端子と電気的に接続するようにして実装されたコンデンサとを具える電圧変換モジュール素子及び電圧変換モジュールにおいて、前記コンデンサの、前記電圧変換用ICの前記入力端子及び前記グランド端子までの接続長の合計を1mm以下とする。

(もっと読む)

コイル内蔵基板

【課題】外部への不要な磁束漏洩が防止され、基板の内部または外面に形成されている配線などの導体に対するノイズの重畳が抑制されたコイル内蔵基板を構成する。

【解決手段】コイル内蔵基板101はコイル導体形成層20と非磁性体層31,32を備えている。コイル導体形成層20は、コイル導体9と磁性体とが積層された磁性体層である。非磁性体層31は電子部品搭載面側(第1主面側)に形成され、表面導体膜7を含む。非磁性体層32は実装先の配線基板に対する実装面側(第2主面側)に形成され、表面導体膜7を含む。コイル導体形成層20と非磁性体層31との間には透磁率の高い磁性体層41を備えている。また、コイル導体形成層20と非磁性体層32との間には透磁率の高い磁性体層42を備えている。

(もっと読む)

電子部品内装型プリント基板の製造方法

【課題】別のビアホールの加工が要らなく、回路設計の自由度を高めることができる電子部品内装型プリント基板の製造方法を提供する。

【解決手段】(A)一面に支持テープと支持基板が付着され、空洞115が厚さ方向に形成されたベース基板110を準備する段階、(B)活性面がベース基板110の一面と一致するように空洞115内に電子部品120を配置する段階、(C)ベース基板110の他面全体にRCC(Resin Coated Copper Foil)またはプリプレグ(prepreg)絶縁材130を積層して電子部品120を埋め込む段階、及び(D)電子部品120の活性面が露出されるように、支持テープと支持基板を除去し、ベース基板110の一面に電子部品の接続端子125と接続する接続パターン145を含む第1回路層140を形成する段階を含んでなる、電子部品内装型プリント基板の製造方法である。

(もっと読む)

電子部材ならびに電子部品とその製造方法

【課題】本発明は、接合材料を微細ピッチで供給し、信頼性が高く電気的な接続が可能な電子部材を提供することを目的とする。

【解決手段】酸化銅から銅へ還元する際、酸化銅内に多数の金属銅の核が形成し、元の外形を維持したまま形骸化して還元され、生成する銅の曲率は大きくなる。この微粒子化メカニズムを利用することで、酸化銅を粒子状ではなく、緻密な層状で提供しても接合が可能となる。また、耐マイグレーション耐性の高い銅を用いることで従来の銀よりも高い信頼性を有する接合が可能となる。本発明は、電気信号を入出力する電極または電気信号を接続するための接続端子を備えた電子部材であって、電極または接続端子の最表面が酸化銅層であることを特徴とする。

(もっと読む)

セラミック基板及びその製造方法並びにイメージセンサーパッケージ及びその製造方法

【課題】本発明は、セラミック基板及びその製造方法並びにイメージセンサーパッケージ及びその製造方法を提供する。

【解決手段】本発明のセラミック基板は、上部面に第1溝が形成され、第1溝に第2溝が形成され、第2溝に貫通孔が形成されたセラミックボディーと、第1溝に形成された第1電極パッドと、セラミックボディーの上部面、下部面及びこれら両面のうちのいずれかに形成され、第1電極パッドに電気的に接続された第2電極パッドと、を含むことを特徴とする。

(もっと読む)

配線板及びその製造方法

【課題】ビア及び配線パターンを容易に形成することが可能な配線板の製造方法を提供する。

【解決手段】第1の金属層の第1の配線パターン113〜119及びビア111,112が形成された面を第1の絶縁層100の上面と対向させ、第2の金属層の第2の配線パターン121〜127が形成された面を第1の絶縁層100の下面と対向させる工程と、第1の配線パターン113〜119及びビア111,112を第1の絶縁層100の上面から圧入するとともに第2の配線パターン121〜127を第1の絶縁層100の下面から圧入することにより第1の絶縁層100の上部に第1の配線パターン113〜119を埋設し、第1の絶縁層100の下部に第2の配線パターン121〜127を埋設し、ビア111,112を第2の配線パターン122,126と圧着する工程とを含む。

(もっと読む)

配線基板、その製造方法および電子機器

【課題】大容量値で占有面積が小さく、高さも比較的小さく、端子接続不良の懸念がない容量素子内蔵タイプの配線基板を提供する。

【解決手段】配線基板内の基板樹脂層6にキャパシタCAPが埋め込まれている。キャパシタCAPは、第1容量電極2、誘電体膜3および第2容量電極4を有する。第1容量電極2は、凸状段差部材23等による凸状段差が連続する形状の面を有する。誘電体膜3は面を被覆しており、面の凸状段差間に誘電体膜を介在させた状態で補強電極部材42(第2容量電極4の一部)の電極材が充填される。補強電極部材42は、凸状段差の面形状を維持し補強する補強部材を兼用する。

(もっと読む)

多層プリント回路基板の製造方法

【課題】多層プリント基板の厚さを減少させるうえ、生産工程を短縮し、生産効率を増大させることが可能な多層プリント基板およびその製造方法の提供する。

【解決手段】多数の回路層および多数の絶縁層を含むビルドアップ層(108)、バンプがプリントされた前記ビルドアップ層(108)の一面の最外層回路層に形成される絶縁樹脂層(101)、および前記ビルドアップ層(108)の他面の最外層に形成される半田レジスト層(112)を含むことを特徴とし、一面にバンプがプリントされた絶縁樹脂層(101)の他面にビルドアップ層(108)、および半田レジスト層(112)を順次積層することにより製造される、多層プリント基板を提供する。

(もっと読む)

実装基板及びその製造方法

【課題】静電容量素子を内蔵する実装基板において実装基板の大きさを制限し小型化する。

【解決手段】樹脂基板の表面に凹凸形状Aを形成し、樹脂基板の凹凸形状の表面を被覆するように導電体を直接堆積して下部電極20を形成し、下部電極の表面を被覆するように誘電体を直接堆積して誘電体膜21を形成し、誘電体膜の表面を被覆するように導電体を直接堆積して上部電極22を形成し、上部電極の上層に樹脂層を形成し、樹脂層の上層に配線を形成する。

(もっと読む)

フレキシブルプリント配線板

【課題】本発明は、伝送損失を改善してデータ伝送の高速化に無理なく対応できるとともに、容易に製造できるフレキシブルプリント配線板を得ることにある。

【解決手段】フレキシブルプリント配線板は、第1の絶縁層と、信号ラインおよびグランドラインを有する導体層と、導体層に積層され、グランドラインの上に開口された開口部を有する第2の絶縁層と、信号ラインを覆うように第2の絶縁層に積層されるとともにグランドラインに電気的に接続されたグランド層と、グランド層を覆う第3の絶縁層と、を含む。グランド層は、開口部の底に露出されたグランドラインを覆うように開口部に充填された第1の導電性ペーストと、第1の導電性ペーストおよび第2の絶縁層を連続して覆うように塗布された第2の導電性ペーストとを備えている。第2の導電性ペーストは、第1の導電性ペーストよりも体積抵抗率が小さい。

(もっと読む)

多層積層回路

【課題】設計の自由度が高く、多くの機能を盛り込んでも、小型化を維持することができる多層集積回路を提供すること。

【解決手段】複数の受動素子用導体層11および複数の配線用導体層12の各層間にセラミック層10を介在させた多層積層回路1であって、受動素子用導体層11および配線用導体層12の少なくとも1層は、当該多層積層回路1の主面表面Saからセラミック層10を貫通するビア13を介して接続され、少なくとも主面表面Sa上でビア13に接続して外部接続が可能な電極を含む外部電極14が主面表面Sa上に形成されるとともに、主面表面Sa上に外部電極14の少なくとも1組を接続する外部配線用導体17が形成される。

(もっと読む)

回路基板、複合部品及びその製造方法

【課題】製造コストを低く抑えることができる回路基板、複合部品及びその製造方法を提供する。

【解決手段】回路基板12、電子部品14及び保護層16を備えている複合部品10。基板本体13は、主面S1,S2を有する板状をなし、かつ、主面S1において電子部品14が実装される実装領域Eを有している。識別マーク18a,18bは、主面S1上であって、かつ、z軸方向から平面視したときに、主面S1の角に接するように設けられている。保護層16は、主面S1及び電子部品14を覆っている。

(もっと読む)

多層基板中に縦方向に構成された共振素子およびこれらを用いたフィルタ

本発明による共振素子は、多層基板と、信号ヴィア導体と、複数のグランドヴィアとを具備する。ここで、多層基板は、誘電体によって絶縁された複数の導体層を含む。信号ヴィア導体は、多層基板を貫通する。複数のグランドヴィアは、多層基板を貫通し、信号ヴィア導体の周囲に配置されている。多層基板は、第1の導体層と、第2の導体層と、波型導体層とを具備する。ここで、波型導体層は、第1および第2の導体層の間に配置されている。波型導体層は、波型信号プレートと、波型グランドプレートとを具備する。ここで、波型信号プレートは、信号ヴィア導体に接続されている。波型グランドプレートは、複数のグランドヴィアに接続されて、誘電体によって波型信号プレートから絶縁されている。 (もっと読む)

1 - 20 / 46

[ Back to top ]