Fターム[5F003BF01]の内容

バイポーラトランジスタ (11,930) | エミッタ・ベース接合 (716) | JE平面パターン (74)

Fターム[5F003BF01]の下位に属するFターム

分割、格子状、くし歯状、リング (24)

Fターム[5F003BF01]に分類される特許

1 - 20 / 50

半導体装置

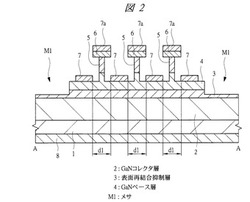

【課題】窒化物半導体を用いたメサ型の半導体装置のp型層の抵抗を低減する。また、窒化物半導体を用いたメサ型の半導体装置に高い値でばらつくオン抵抗が生じることを防ぐ。

【解決手段】窒化物半導体からなり、所定のベース電極間隔を有するヘテロ接合バイポーラトランジスタにおいて、GaNベース層4およびGaNコレクタ層2の間に表面再結合抑制層3を設け、GaNベース層4を貫通して表面再結合抑制層3の途中深さまで開口するメサM1を形成することでGaNベース層4を分離する。

(もっと読む)

半導体デバイス

【課題】高い電流増幅率と高いアーリー電圧を両立することができ、CMOSトランジスタとともに製造する場合でもより少ない製造工程により製造することができる半導体デバイスを提供する。

【解決手段】基板P11の表面に形成された第1導電型のベースP14と、ベースの表面に形成された第2導電型のエミッタN23と、ベースの表面においてエミッタと離間して配置され、エミッタから第1の種類のキャリアを受け取るとともに、その第1の種類のキャリアをベースへ注入する、第2導電型のドープ領域N24と、ベースを挟んで、エミッタおよびドープ領域の反対側に形成された、第2導電型のコレクタN15とを備える。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧が確保でき、大きな放電電流を流すことが可能なESD保護特性のすぐれたESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3でPN接合ダイオード35を形成する。P+型埋め込み層3はP+型引き出し層5と一体となりN−型エピタキシャル層4を貫通させアノード電極10と接続される。P+型埋め込み層3等で囲まれたN−型エピタキシャル層4にN+型拡散層7と該N+型拡散層7と接続され、これを取り囲むP+型拡散層6を形成する。N+型拡散層7、P+型拡散層6はカソード電極9に接続される。P+型拡散層6をエミッタ、N−型エピタキシャル層4をベース、P+型引き出し層5等をコレクタとする寄生PNPバイポーラトランジスタ38とPN接合ダイオード35でESD保護素子を構成する。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3で形成するPN接合ダイオード35と、P型拡散層6と接続するP+型埋め込み層3aをエミッタ、N−型エピタキシャル層4をベース、P+型埋め込み層3をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構築する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それを取り囲むN+型拡散層7はカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、その放電電流I1によりP+型埋め込み層3よりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタの形成領域において半導体層の下部に絶縁層を有する基板が用いられた半導体装置において、バイポーラトランジスタの電流増幅率を向上させる。

【解決手段】バイポーラトランジスタは、半導体層1cに形成されたコレクタ5、ベース7、エミッタ9、ベース用高濃度オーミック拡散層11及びコレクタ用高濃度オーミック拡散層13、並びに半導体層1c上に形成されたゲート絶縁膜15及びゲート電極17を備えている。ベース7は、絶縁層1bに達する深さで形成され、上方から見てゲート電極17と一部重複して形成され、ゲート電極17下でコレクタ5に隣接して形成されている。ベース7は、ベース7側のゲート電極17の端部からコレクタ5側に向かってP型不純物濃度が低くなる濃度傾斜をもっている。

(もっと読む)

炭化珪素半導体装置

【課題】エミッタ層からコレクタ層を経由してベース層へ移動する電荷の移動を阻止し、エミッタ層からコレクタ層を経由してベース層に注入される電荷を無くすことで、コレクタ層における欠陥の成長を防止することが可能な炭化珪素半導体装置を提供する。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素半導体基板により構成された炭化珪素半導体装置であり、第1の導電型のコレクタ層102と、コレクタ層の上部に設けられた第2の導電型のベース層104と、ベース層の一部として設けられたベース電極105と、ベース層上に設けられベース電極と離間して設けられたエミッタ層107と、ベース電極からエミッタ層に対して移動する電荷の経路において、コレクタ層内に設けられた、コレクタ層内における電荷の経路を遮断する絶縁体層112とを有する。

(もっと読む)

バイポーラ半導体素子

【課題】表面欠陥を低減でき、オン電圧ドリフトを抑制できるバイポーラ半導体素子を提供する。

【解決手段】このSiC GTOによれば、メサ状のp型アノードエミッタ層5の長側面5Bが延在している方向を、〈11−20〉方向としたオフ方向から角度φ=60°だけ傾斜させた方向とした。これにより、長側面5Bは、{01−10}面となり、{11−20}面である短側面5Cに比べて、表面欠陥が入りにくくなる。また、長側面5Bの延在方向を、上記オフ方向から角度φ=60°だけ傾斜させたことで、長側面5Bの延在方向とオフ方向とが一致している場合(φ=0°)に比べて、メサ状のp型アノードエミッタ層5の長側面5Bに現れる{0001}面の層の数を減らすことができて、{0001}面の層内に入る表面欠陥を減少できる。

(もっと読む)

半導体装置

【課題】 放熱性を改善したバイポーラトランジスタを有する半導体装置を提供することにある。

【解決手段】 複数のバイポーラトランジスタQuが配列される半導体装置であって、エミッタ配線L3は幅広部と細長部とを有し、細長部におけるバイポーラトランジスタ素子数が、幅広部が配置された配列の外縁に沿う方向に配列されたバイポーラトランジスタ素子数よりも少なくなるように配置する。

【効果】エミッタ配線の寄生抵抗によるエミッタ−ベース間電圧ばらつきを低減する。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

電流増幅素子

【課題】なだれ増倍を利用して電流を直接増幅することが可能であると共に、リニアモード動作において、高感度と応答速度の速さとを両立させることができる電流増幅素子を提供する。

【解決手段】電流増幅素子は、半導体基板の表面に平面視が円形となるように中心軸の周りに対称に形成されたn型半導体ウエル(n−ウエル)104、n−ウエル内に同心円状に形成されたp型半導体領域112、p型半導体領域内に同心円状に形成されたn型半導体領域112、及び順バイアス電圧と逆バイアス電圧とを印加するための複数の電極を備えている。n−ウエルの内側の面は、中心軸から予め定めた距離の範囲内では基板裏面に向って半径が小さくなると共に、範囲より外側では基板裏面に向って半径が大きくなるように形成されている。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】CMOS回路側の仕様で不純物領域の深さや濃度が制約を受けるような場合でもhFEの向上を可能とする。

【解決手段】1つのバイポーラトランジスタが、横型の主トランジスタ部と、縦型の補助トランジスタ部とから形成されている。横型の主トランジスタ部は、エミッタ領域31と、ベース領域14Bの表面側部分とコレクタ側部領域13Bとを電流チャネルとして動作する。縦型の補助トランジスタ部は、エミッタ領域31と、その底面に接するベース領域14Bの深部側部と、コレクタ深部領域12Bとを電流チャネルとして動作する。

(もっと読む)

高周波増幅器

【課題】回路面積を増加させることなく、動作状態のトランジスタからの発熱を抑制することによって、小型化及び低コスト化を図ることができる高周波増幅器を提供する。

【解決手段】複数の単位トランジスタ3が並列に接続されたトランジスタ列からなり、高周波を増幅する増幅素子と、トランジスタ列の隣り合った単位トランジスタ3のフィンガ間にそれぞれ形成された出力整合回路の回路素子2とを備える。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製法

【課題】高い電流増幅率を有し、高周波特性および素子寿命に優れたヘテロ接合バイポーラトランジスタおよびその製法を提供すること。

【解決手段】半絶縁性基板1上に、n型半導体より成る真性エミッタ層16と、p型ドーパントを高濃度でドーピングされ、真性エミッタ層16よりも狭いバンドギャップを有する半導体より成るベース層9と、ベース層9と同じ半導体より成るコレクタ層10とを、この順序で積層して成るへテロ接合バイポーラトランジスタにおいて、真性エミッタ層16の周囲に、高抵抗領域15が設けられ、高抵抗領域15と真性エミッタ層16との間に、真性エミッタ層16の半導体と同じ半導体から成るガードリング領域17が設けられ、真性エミッタ層16とベース層9との接合面が、ガードリング領域17の上面よりも下に位置することを特徴とするヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

ESD保護素子

【課題】ESD耐量を向上させたESD保護素子を提供する。

【解決手段】本発明によるESD保護素子は、バイポーラトランジスタを用いたESD保護素子である。バイポーラトランジスタは、第1端子(Pad)に接続されるコレクタ拡散層7とエミッタ端子とを備えるバイポーラトランジスタと、第2端子(GND)からエミッタ拡散層4を介してコレクタ拡散層7に至る複数の電流経路上のそれぞれに設けられた電流制御抵抗11とを具備する。

(もっと読む)

非単結晶半導体間隔部分がベース・リンク長を制御するバイポーラ接合トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体構成体がバイポーラトランジスタ(101)及び間隔構成体(265−1又は265−2)を包含している。

【解決手段】 該トランジスタはエミッタ(241)、ベース(243)、コレクタ(245)を有している。該ベースはベースコンタクト部分(243−1)、該エミッタの下側で且つ該コレクタの物質上方に位置されているイントリンシックベース部分(243I−1)、該イントリンシックベース部分とベースコンタクト部分との間に延在しているベースリンク部分(243L−1)を包含している。該間隔構成体は、間隔コンポーネント及び上部半導体表面に沿って延在する分離用誘電体層(267−1又は267−2)を包含している。該間隔コンポーネントは、該ベースリンク部分の上方で該誘電体層上に位置されており、好適には多結晶半導体物質であるほぼ非単結晶の半導体物質の横方向間隔部分(269−1又は269−2)を包含している。該横方向間隔部分の両側の第1及び第2下部端部(305−1及び307−1)は該ベースリンク部分の両側の第1及び第2上部端部(297−1及び299−1)に対して横方向に適合し、その長さを決定し且つそれにより制御する。

(もっと読む)

電流シフト領域を有する半導体デバイスおよび関連方法

半導体デバイスは、第1の伝導形を有する半導体バッファ層と、バッファ層の表面上にあって第1の伝導形を有する半導体メサとを含む。さらに第2の伝導形を有する電流シフト領域が半導体メサと半導体バッファ層との間の隅に隣接して設けられ、第1と第2の伝導形が互いに異なる伝導形である。関連する方法も開示される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、エミッタ拡散層等を形成する際のマスクずれにより、デバイスサイズが縮小され難く、高耐圧化が達成され難いという問題があった。

【解決手段】本発明の半導体装置では、エミッタ領域としてのP型の拡散層18の周囲には、LOCOS酸化膜14、15、N型の拡散層22、23が形成される。N型の拡散層22、23の周囲には、コレクタ領域としてのP型の拡散層19、20が、N型の拡散層22、23と離間して形成される。この構造により、P型の拡散層18〜20、N型の拡散層22、23が位置精度良く形成され、ベース領域幅Wb1が狭められ、高耐圧の横型PNPトランジスタが形成される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】トランジスタを短絡させることなく、シリサイド層を形成することができる半導体装置の提供。

【解決手段】バイポーラトランジスタ形成領域100と、CMOSトランジスタ形成領域200とを分離し、絶縁層52a,52bを形成し、上方に導電層56a,56bを形成し、側壁54a,54bを形成して、バイポーラトランジスタ形成領域100に、短絡防止部50aを形成すると同時に、CMOSトランジスタ形成領域200にゲート50bを形成する。バイポーラトランジスタのエミッタ領域40a、コレクタ領域40bおよびベース領域42aおよびCMOSトランジスタのソース領域40c,42bおよびドレイン領域40d,42cを形成し、各領域の上にシリサイド層60を形成する。短絡防止部50aは、エミッタ領域40a、コレクタ領域40bおよびベース領域42aのうち、いずれか2つの領域の間に位置する半導体基板10の上方に形成される。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】半導体集積回路装置の設計工数を低減する。

【解決手段】SOI基板1の半導体層において、互いに完全に電気的に分離された複数の単位バイポーラトランジスタQuを並列接続することにより、大電流容量を必要とするバイポーラトランジスタを構成する。また、所望の電流容量を与えるトランジスタは、幾何学的寸法が、実質的に同一サイズである複数の単位バイポーラトランジスタを、互いに電気的に並列接続することにより構成する。

(もっと読む)

トランジスタ構造および半導体装置

【課題】パワー半導体素子として、動作時の熱暴走および熱破壊が防止でき、且つ、安全動作領域SOAが拡大されるトランジスタを提供する。

【解決手段】第1導電型のコレクタ層2と、前記コレクタ層上に島状に形成され且つ前記第1導電型と異なる第2導電型のベース層3と、前記ベース層上に少なくとも1つの島状に形成され且つ前記第1導電型のエミッタ層4a,4bと、前記ベース層と電気的に接続されベースコンタクト9を形成するベース電極と、前記エミッタ層と電気的に接続されエミッタコンタクト10を形成するエミッタ電極と、前記コレクタ層と電気的に接続されたコレクタ電極と、を有し、前記エミッタ層上に形成され且つ前記第1導電型の第1抵抗層11が、平面的に見て、前記ベースコンタクトを包囲するように形成されることを特徴とするトランジスタ構造。

(もっと読む)

1 - 20 / 50

[ Back to top ]