Fターム[5E346AA04]の内容

多層プリント配線板の製造 (97,916) | 多層の形状、構造 (21,562) | 基台の形状、構造 (1,878) | 基板内に配線を有するもの (256)

Fターム[5E346AA04]に分類される特許

41 - 60 / 256

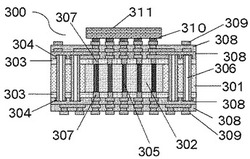

ハイブリッドコア基板とその製造方法、半導体集積回路パッケージ、及びビルドアップ基板とその製造方法

【課題】半導体集積回路を実装する際に、リフローなどの熱履歴で発生する基板の反りが、最小限に小さく抑制されたハイブリッドコア基板、それを用いた半導体集積回路パッケージ、ビルドアップ基板を提供する。

【解決手段】複数の開口部を有するコア基板に、実装する半導体チップと略同一のサイズの複数のセラミック基板302を勘合させ、さらにその表層にコア基板より弾性率の低い絶縁層303を積層したハイブリッドコア基板とすることで、該基板を半導体チップのはんだ接合法による実装に用いても、基板の反りを最小限に抑えることができ、かつ加工性に富むビルドアップ基板を得ることができる。

(もっと読む)

回路板とその製造方法

【課題】同時に導電ペーストバイアおよび金属バイアを備える回路板を製造する回路板の製造方法、並びに同時に導電ペーストバイア及び金属バイアを備える回路板を提供する。

【解決手段】回路板が第1配線構造および第2配線構造を含む。第1配線構造が、第1誘電層と第1配線層と第2配線層と金属バイアとを含む。第1誘電層が互いに対向する第1表面および第2表面を有する。第1配線材料層が第1表面上に配置される。第2配線材料層が第2表面上に配置される。金属バイアが第1誘電層中に配置され、第1配線材料層および第2配線材料層を電気接続する。第2配線構造が第1配線構造上に配置される。第2配線構造が第3配線層と第2誘電層と導電ペーストバイアとを含む。第2誘電層が第1表面上に配置され、第1配線層を被覆する。第3配線層が第2誘電層上に配置される。導電ペーストバイアが第2誘電層中に配置され、第1配線層および第3配線層を電気接続する。

(もっと読む)

半導体パッケージ

【課題】複数のシリコン基板同士の電気接続長を短くして、寄生容量を最小にするとともに、パッケージ基板全体の反りを抑制して接続信頼性を有する半導体パッケージを提供する。

【解決手段】半導体パッケージ9は、半導体素子を備えた複数のシリコン基板1を内蔵する半導体パッケージにおいて、第1のシリコン基板にシリコン貫通ヴィア2を備え、パッケージ基板を形成するコア基板10の基材の線膨張係数が、3〜8ppm/℃である。

(もっと読む)

ハイブリッド基板およびその製造方法

【課題】ビルドアップ基板の製造に好適な基板を提供すること。

【解決手段】本発明のハイブリッド基板は、複数のセラミック基板から成るセラミック基板集合体、セラミック基板集合体の両面に対向配置され、補強材と樹脂とから少なくとも構成された絶縁樹脂層、および、絶縁樹脂層上に配置された金属層を有して成る。特に本発明のハイブリッド基板においては、複数のセラミック基板が、対向配置された絶縁樹脂層間の同一平面上に沿ってタイリングされている。

(もっと読む)

部品内蔵多層配線板およびその製造方法

【課題】配線板の表面および裏面に実装される電子部品を1回の接続工程で製造可能とした部品内蔵多層配線板およびその製造方法を提供する。

【解決手段】実施形態の部品内蔵多層配線板は、第1の印刷配線板と、第1の印刷配線板と同じ大きさの第2の印刷配線板と、第1の印刷配線板の表層に実装される第1電子部品と、第1の印刷配線板と第2の印刷配線板の間に内蔵され、第1電子部品と対向する前記第1の印刷配線板の裏層に実装される第2電子部品とを有する。そして、第1の印刷配線板の第1電子部品および第2電子部品の両端に設けられるスルーホールを用いて、第1の印刷配線板と第1電子部品との接続時に、第1の印刷配線板と第2電子部品との接続を同時に行う。

(もっと読む)

電子装置及びその製造方法

【課題】多層配線が簡易な方法によって低コストで形成される電子装置の製造方法を提供する。

【解決手段】第1配線層30の上に、絶縁層22の上に金属層32aが積層された積層膜CFを形成する工程と、積層膜CFの上に開口部23aが設けられたレジスト23を形成する工程と、レジスト23の開口部23aを通して金属層32aをエッチングすることにより金属層32aに開口部32xを形成する工程と、ウェットブラスト法により、金属層32aの開口部32xを通して絶縁層22をエッチングすることにより、第1配線層30に到達するビアホールVHを形成する工程と、ビアホールVHに導電性ペースト40又ははんだからなるビア導体を形成することにより、第1配線層30と第2配線層32となる金属層32aとをビア導体で接続する工程とを含む。

(もっと読む)

多層プリント配線板

【課題】 高周波領域のICチップ、特に3GHzを越えても誤動作やエラーの発生しないパッケージ基板を提供する。

【解決手段】 コア基板30上の導体層34Pを厚さ30μmに形成し、層間樹脂絶縁層50上の導体回路58を15μmに形成する。導体層34Pを厚くすることにより、導体自体の体積を増やすし抵抗を低減することができる。更に、導体層34を電源層として用いることで、ICチップへの電源の供給能力を向上させることができる。

(もっと読む)

積層回路基板および基板製造方法

【課題】接着層の絶縁性が劣化することを防止するとともに、接合の信頼性が低下することを防止することを課題とする。

【解決手段】積層回路基板1は、基板10Aおよび基板10Bの接続ランド12同士が導電材料13により接合され、複数の配線パターン11が電気的に結合された多層構造のプリント配線基板である。また、積層回路基板1は、基板10Aと基板10Bとの間に、ランド12同士を接合するための貫通孔31が形成されたプレート30を有する。プレート30は、導電材料13を形成する位置に対応する貫通孔31があり、貫通孔31の径の大きさが導電材料13の充填径よりも大きい。

(もっと読む)

積層回路基板、接着シート、積層回路基板の製造方法および接着シートの製造方法

【課題】ボイドの発生を防止しつつ、ランド間を接合することを課題とする。

【解決手段】積層回路基板は、表面に第1ランドが形成されている第1配線基板と、表面に第2ランドが形成されている第2配線基板とで形成される。さらに、積層回路基板は、第1配線基板と第2配線基板との間に配置され、第1ランドと第2ランドを導電性材料にて電気的に接合する接着層を有する。そして、接着層は、中心層を成す誘電材料の粘度が表裏層を成す誘電材料の粘度よりも高く形成される。

(もっと読む)

変性シアネートエステル系樹脂組成物を用いた絶縁ワニス及びその樹脂フィルム製造法

【課題】耐熱性、耐湿性、耐溶剤性及び耐薬品性が良好で、かつ印刷配線板の薄形・軽量化と高密度化に有効なビルドアップ積層方式に適した絶縁フィルムであって、高周波帯域での誘電率と誘電正接が低く高周波回路の低損失性を実現でき、しかも耐クラック性及び回路充填性などの成形性が良好な変性シアネートエステル系硬化性樹脂組成物を用いた絶縁ワニス及びフィルムの製造法を提供する。

【解決手段】(A)シアネートエステル化合物、(B)フェノール類化合物、(C)ポリフェニレンエーテル樹脂、(D)充填材及び(E)エポキシ樹脂を必須成分として含有する樹脂組成物からなる絶縁ワニス。

(もっと読む)

多層配線基板

【課題】 大電流を流すことができ、かつ、電源ノイズを低減することが可能な多層配線基板を提供する。

【解決手段】 多層配線基板1は、電源回路と三端子コンデンサ50の入力端子50aとを接続する第1電源パターン11、及び三端子コンデンサ50の出力端子50bとIC60の電源端子60aとを接続する第2電源パターン12を含む第1配線層10と、第1電源パターン11と第1ビア40により接続され、該第1ビア40と三端子コンデンサ51の入力端子51aとを接続する第3電源パターン21、及び三端子コンデンサ51の出力端子51bと第2ビア46の他端とを接続する第4電源パターン22を含む第2配線層20と、グランド層30と、三端子コンデンサ50のグランド端子50c,50dとグランド層30とを接続する第4ビア41,42と、三端子コンデンサ51のグランド端子51c,51dとグランド層30とを接続する第5ビア43,44とを備える。

(もっと読む)

セラミック多層配線基板の製造方法

【課題】各セラミック層に挟まれる多数の側面電極を備えたセラミック多層配線基板を製造するのに、多数個取り用のグリーンシートを積層圧着してなる未焼成セラミック積層体とし、これを配線基板部位相互間の境界線で切断して未焼成配線基板とし、その側面に側面電極形成用のメタライズインク部位を露出させたものとし、これを焼成する場合で、側面電極の層間方向の端面と、これが接すべき各セラミック層の端面との間に剥離が生じるのと、側面電極が基板側面から凹むのを防ぐ。

【解決手段】 グリーンシート201の側面電極形成用のビアホール211に充填した柱状メタライズインク部位30の端面、又はその端面が接すべきグリーンシート201の面の対応部位に、メタライズインクをパッド層を38,39なすよう補填印刷しておく。これにより圧着後の未焼成セラミック積層体の切断前、その内部のインクを高圧にする。

(もっと読む)

部品内蔵配線板、部品内蔵配線板の製造方法

【課題】部品内蔵によっても配線板としての信頼性が低下しにくい部品内蔵配線板およびその製造方法を提供すること。

【解決手段】端子を有する電気/電子部品と、電気/電子部品の表面の少なくとも一部に密着して該電気/電子部品の少なくとも一部分を埋め込んだ板状絶縁層と、この板状絶縁層の上面上に設けられた第1の配線パターンと、板状絶縁層の上面に対向する下面上に設けられた、電気/電子部品の実装用のランドを含む第2の配線パターンと、電気/電子部品の端子と第2の配線パターンのランドとを電気的、機械的に接続する、すずおよび金を含むはんだ接続部材と、を具備し、第2の配線パターンが、基層と、該基層上位置選択的に積層された、はんだ接続部材と該基層との間に挟まれて位置するニッケル金属層とを有する。

(もっと読む)

配線基板の製造方法

【課題】半導体素子を搭載する配線基板において、コア用の絶縁板に形成されたスルーホール直上にビルドアップ用のビアホール形成ができ、コア用の配線導体においてもその幅や間隔を20μm以下とした高密度な微細配線を有し、かつ厚みが140μm以下のコア用の絶縁板を使用可能な薄型の配線基板の製造方法を提供すること。

【解決手段】スルーホール7を有するコア用の絶縁板1のスルーホール7内壁のみにスルーホール7と同軸の貫通孔を有するように第1のめっき導体層13を被着させ、次に貫通孔内および絶縁板1の上下面に、貫通孔内を充填するとともにコア用の絶縁板1の上下面において配線導体4を形成する第2のめっき導体層14を被着する。

(もっと読む)

電子部品内蔵基板、電子回路モジュール、および電子部品内蔵基板の製造方法

【課題】 従来よりも厚みの小さな電子部品内蔵基板を提供する。

【解決手段】 本発明の電子部品内蔵基板100は、少なくとも一方の主面に収納部4が形成されたコア基板10と、収納部4の底面に固定された電子部品6と、コア基板10の主面上に形成された樹脂層7と、樹脂層7を貫通して形成され樹脂層内導電ビア8a、8bとを備えた構成からなる。

(もっと読む)

配線基板内蔵用コンデンサ、及び配線基板

【課題】配線基板における樹脂材との密着性を向上することができる配線基板内蔵用コンデンサを提供すること。

【解決手段】セラミックコンデンサ101のコンデンサ本体104における側面106a〜106dには、セラミック誘電体層105を構成するセラミックが露出するとともに、コンデンサ本体104の厚さ方向に延びる凹部107が複数形成されている。コンデンサ本体104の側面106aにおける複数の凹部107は、厚さ方向に沿った長さがコンデンサ本体104の厚さよりも小さく、側面側から見たときの基端部107aの幅が先端部107bの幅よりも大きい。凹部107の先端部107bは、側面側から見て丸みを帯びた形状を有している。

(もっと読む)

多層セラミック基板の製造方法

【課題】表面電極と、内部電極や内部回路などの内部導体との間の絶縁性を確保することが可能で、信頼性の高い多層セラミック基板を確実に製造できるようにする。

【解決手段】セラミック積層体20の焼成工程で、セラミック積層体の、表面電極パターン11が形成された主面と、収縮抑制層3との間に、セラミック積層体を構成する第1のセラミックグリーン層1よりも収縮開始温度が低い第2のセラミックグリーン層2を配置した状態で焼成を行った後、第2のセラミックグリーン層が焼成されてなる第2のセラミック層と、収縮抑制層とを除去する。

第2のセラミックグリーン層として、収縮開始温度が、第1のセラミックグリーン層の収縮開始温度よりも20℃以上低いものを用いる。

第2のセラミックグリーン層に含まれるセラミック材料としては、ガラス材料のみからなるものを用いる。

また、前記ガラス材料は、結晶化しないガラスからなるものを用いる。

(もっと読む)

多層配線基板、及び多層配線基板の製造方法

【課題】電気的接続の高い信頼性を有するビアホール導体により層間接続された、Pbフリーのニーズに対応することができる多層配線基板を提供することを目的とする。

【解決手段】絶縁樹脂層と絶縁樹脂層の両面にそれぞれ配設された配線とこれらの配線間を電気的に接続するためのビアホール導体とを有し、ビアホール導体は金属部分と樹脂部分とを含み、金属部分は、配線間を接続する銅粒子の結合体を含む第一金属領域と、錫,錫‐銅合金,及び錫‐銅金属間化合物等を主成分とする第二金属領域と、ビスマスを主成分とする第3金属領域と、を有し、結合体を形成する銅粒子同士が互いに面接触することにより面接触部を形成し、第二金属領域の少なくとも一部分が第一金属領域に接触している多層配線基板である。

(もっと読む)

多層配線基板の製造方法

【課題】支持基材に対して積層を行って分離した後の積層体を擬似的なコア基板として用い、積層数を容易に増やすことが可能な多層配線基板の製造方法を実現する。

【解決手段】本発明の多層配線基板の製造方法は、板状の支持基材11上に樹脂絶縁層20〜23と導体層30〜32とを交互に積層して中間積層体を形成し、その表面側の全面に金属めっきを施した後に中間積層体と支持基材11を分離し、分離後の積層体10bに対し樹脂絶縁層と導体層とを交互に積層して配線積層部を形成することで多層配線基板が得られる。これにより、従来のコアレス配線基板よりも積層数を容易に増やすことが可能な多層配線基板を実現することができる。

(もっと読む)

プリント配線基板

【課題】 複数のグランドを持ち、これらのグランド上に配置されたデバイス間で高速信号伝送を行う場合のグランドからの伝導ノイズ抑制可能なプリント配線基板を提供すること。

【解決手段】 表面層に配置されノイズ吸収体がその上に配されたブリッジに複数のグランドが直接的にまたは高周波的に接続され、前記複数のグランドの一つを基準電位とする第1のデバイスと、前記第1のデバイスのグランド以外の前記複数のグランドの1つを基準電位とする第2のデバイスとを連結する高速信号配線がプリント配線基板の層方向の隣接層に配線され伝送線路構造を形成することを特徴とするプリント配線基板を主な発明とする。

(もっと読む)

41 - 60 / 256

[ Back to top ]