Fターム[5F003BH01]の内容

バイポーラトランジスタ (11,930) | 電極、配線 (1,046) | 電極平面パターン (119)

Fターム[5F003BH01]の下位に属するFターム

くし歯状電極 (35)

Fターム[5F003BH01]に分類される特許

1 - 20 / 84

半導体装置

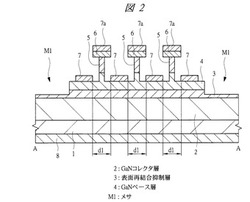

【課題】窒化物半導体を用いたメサ型の半導体装置のp型層の抵抗を低減する。また、窒化物半導体を用いたメサ型の半導体装置に高い値でばらつくオン抵抗が生じることを防ぐ。

【解決手段】窒化物半導体からなり、所定のベース電極間隔を有するヘテロ接合バイポーラトランジスタにおいて、GaNベース層4およびGaNコレクタ層2の間に表面再結合抑制層3を設け、GaNベース層4を貫通して表面再結合抑制層3の途中深さまで開口するメサM1を形成することでGaNベース層4を分離する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】断線等の問題を抑制しつつ逆メサの段差に配線を設けることができる半導体装置の製造方法を提供する。

【解決手段】エッチングにより半導体基板に逆メサ段差部を形成する。逆メサ段差部の下段における半導体基板の表面に、電極を設ける。逆メサ段差部内を埋めるように当該逆メサ段差部の高さよりも厚い絶縁膜を設ける。逆メサ段差部内に絶縁膜を残すように、絶縁膜積層工程で積層した絶縁膜に対してエッチバックを行う。電極に接続する配線を、逆メサ段差部に残された絶縁膜の上方に設ける。このとき、電極とのコンタクトをとる部分を対象にして、層間絶縁膜に対し開口を形成する。開口形成後、配線を、層間絶縁膜上であって逆メサ段差部の上方の領域に蒸着する。コンタクト開口を介して、配線が電極と接続する。

(もっと読む)

半導体デバイス

【課題】高い電流増幅率と高いアーリー電圧を両立することができ、CMOSトランジスタとともに製造する場合でもより少ない製造工程により製造することができる半導体デバイスを提供する。

【解決手段】基板P11の表面に形成された第1導電型のベースP14と、ベースの表面に形成された第2導電型のエミッタN23と、ベースの表面においてエミッタと離間して配置され、エミッタから第1の種類のキャリアを受け取るとともに、その第1の種類のキャリアをベースへ注入する、第2導電型のドープ領域N24と、ベースを挟んで、エミッタおよびドープ領域の反対側に形成された、第2導電型のコレクタN15とを備える。

(もっと読む)

積層電池および積層電池システム

【課題】従来の捲回電池は、電池内部の温度の上昇を抑制することが困難であった。電池内部に冷媒を流したパイプ等を設ければ、電池寸法が大きくなる。更には、従来の電池は電池価格に大きな影響を及ぼす負極の量が多く、電池価格の低減を図ることが困難であった。

【解決手段】正極および負極を筒状外装体の軸方向に積層して、正極もしくは負極の一方の電極の外径を外装体の内径より大きくすることにより、正極もしくは負極を外装体に密に接触させることにより、電極の熱伝達の向上を図り、電池の温度上昇を抑制する。更には、負極規制とすることにより高価な水素吸蔵合金の使用量を減らして、電池価格の低減を図る。

(もっと読む)

炭化珪素半導体装置

【課題】エミッタ層からコレクタ層を経由してベース層へ移動する電荷の移動を阻止し、エミッタ層からコレクタ層を経由してベース層に注入される電荷を無くすことで、コレクタ層における欠陥の成長を防止することが可能な炭化珪素半導体装置を提供する。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素半導体基板により構成された炭化珪素半導体装置であり、第1の導電型のコレクタ層102と、コレクタ層の上部に設けられた第2の導電型のベース層104と、ベース層の一部として設けられたベース電極105と、ベース層上に設けられベース電極と離間して設けられたエミッタ層107と、ベース電極からエミッタ層に対して移動する電荷の経路において、コレクタ層内に設けられた、コレクタ層内における電荷の経路を遮断する絶縁体層112とを有する。

(もっと読む)

半導体装置及び電力増幅器

【課題】トランジスタの占有面積をほとんど増やすことなく、かつ、HBTとHFETとを接続する配線による悪影響を受けないBi−HFET(半導体装置)を提供する。

【解決手段】基板101上に形成されたHFET160と、HFET160上に形成されたHBT170とを備え、HFET160は、チャネル層102と、コンタクト層104とを有し、HBT170は、HFET160のコンタクト層104と接続、又は、一体化されたサブコレクタ層107と、コレクタ層108と、ベース層109と、エミッタ層110と、エミッタキャップ層111と、エミッタコンタクト層112とを有し、コレクタ層108、ベース層109及びエミッタ層110は、メサ形状の構造体であるベースメサ領域830を構成し、ゲート電極202は、第一のコレクタ電極203とベースメサ領域830との平面的な間に設けられたリセス領域820内に形成されている。

(もっと読む)

半導体装置

【課題】デバイスサイズの縮小、シリーズ抵抗の低減、及びリーク電流の抑制を可能とする半導体装置を提供することを目的とする。

【解決手段】本発明は、デバイス動作にとって、本来は不要な電位段差を発生させる層をデバイスの構造内にあえて挿入したものである。この電位段差は、バンドギャップの小さな半導体がメサ側面に露出しても、その部分の電位降下量を抑制し、デバイス動作に不都合なリーク電流を低減できる、という機能をもたらす。この効果は、ヘテロ構造バイポーラトランジスタ、フォトダイオード、及び電界吸収形光変調器などに共通して得られる。また、フォトダイオードにおいては、リーク電流が緩和されるのでデバイスのサイズを縮小することが可能となり、シリーズ抵抗の低減による動作速度の改善のみならず、デバイスを高密度にアレイ状に配置できるという利点も生まれる。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】電流利得や電流利得遮断周波数などの他の素子性能を劣化させることなく、ヘテロ接合バイポーラトランジスタのオン電圧が効果的に低減できるようにする。

【解決手段】基板101の上に、サブコレクタ層102、コレクタ層103、ベース層104、第1エミッタ層105、第2エミッタ層106、および、キャップ層107が順次積層されており、第2エミッタ層106は、第1エミッタ層105に対してウェットエッチング法により選択的に除去される半導体材料によって形成され、かつ、第2エミッタ層106を構成する半導体が不純物添加によって縮退している。加えて、このHBTの第1エミッタ層105は、ベース層104の側に配置されて不純物が添加された第1半導体層151と、第2エミッタ層106の側に第1半導体層151に接して配置されて不純物が無添加の第2半導体層152とから構成されている。

(もっと読む)

半導体装置

【課題】 放熱性を改善したバイポーラトランジスタを有する半導体装置を提供することにある。

【解決手段】 複数のバイポーラトランジスタQuが配列される半導体装置であって、エミッタ配線L3は幅広部と細長部とを有し、細長部におけるバイポーラトランジスタ素子数が、幅広部が配置された配列の外縁に沿う方向に配列されたバイポーラトランジスタ素子数よりも少なくなるように配置する。

【効果】エミッタ配線の寄生抵抗によるエミッタ−ベース間電圧ばらつきを低減する。

(もっと読む)

半導体装置

【課題】支持基板に接地電極を備えることなく、第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供する。

【解決手段】支持基板10を、第1導電型領域10aと第2導電型領域10bとを有し、第1素子形成領域20にノイズが印加されてノイズが伝播されたときの当該ノイズの伝播経路中に、第1、第2導電型領域10a、10bで構成されるPNP接合またはNPN接合を有するものとする。このような半導体装置では、PNP接合またはNPN接合の間に構成される空乏層により、第1、第2素子形成領域20、30の間でノイズが伝播することを抑制することができる。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】HBTによる段差を低減し、接合面積をより小さくできるようにする。

【解決手段】半絶縁性のInPからなる基板101の上に形成されたアンドープInPからなる第1半導体層102と、第1半導体層102の上に接して形成された第1導電型のInPからなるエミッタ層103と、第1半導体層102の上に接して形成された第2導電型のInGaAsからなるベース層106と、第1半導体層102の上に接して形成されたInGaAsからなるコレクタ層107とを少なくとも備える。加えて、エミッタ層103,ベース層106,およびコレクタ層107は、これらの順に第1半導体層102の平面上で配列して接続されている。

(もっと読む)

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

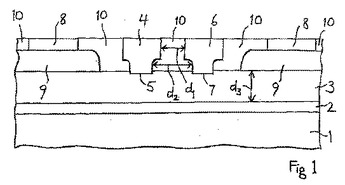

横方向のエミッタおよびコレクタを有するバイポーラトランジスタならびに製造方法

バイポーラトランジスタは、半導体材料からなる基板(1)と、基板内の高移動度層(2)と、高移動度層に隣接したドナー層(3)とを含む。エミッタ端子(4)がドナー層上のエミッタコンタクト(5)を形成し、コレクタ端子(6)がドナー層上のコレクタコンタクト(7)を形成する。ベース端子(8)が高移動度層に導電接続される。当該トランジスタは、GaAsのHEMT技術またはBiFET技術で製造可能である。  (もっと読む)

(もっと読む)

半導体装置

【課題】電力破壊を抑制できる半導体装置を提供すること。

【解決手段】ベース領域12の表面に設定されたベースコンタクト領域14において、ベース電極15がベース領域12に接合されている。ベースコンタクト領域14の境界部の下方には、エミッタ領域13と同じ導電型を有するN型領域21がベースコンタクト領域14を包囲するように形成されている。言い換えれば、ベースコンタクト領域14の境界部の下方において、P型のベース領域12およびN型領域21によりPN型の寄生ダイオードが形成されている。

(もっと読む)

大面積ナノ可能マクロエレクトロニクス基板およびその使用

【課題】複数の半導体デバイスを有する電子的な基板を得るための方法および装置。

【解決手段】ナノワイヤ薄膜が、基板上に形成される。ナノワイヤ薄膜は、動作電流レベルを達成するのに十分なナノワイヤの密度を有するように形成される。複数の半導体領域が、ナノワイヤ薄膜に画定される。コンタクトが、半導体デバイス領域において形成され、それによって、電気的な接続を複数の半導体デバイスに提供する。さらに、ナノワイヤを製造するための様々な材料、p型ドーピングナノワイヤおよびn型ドーピングナノワイヤを含む薄膜、ナノワイヤヘテロ構造、発光ナノワイヤヘテロ構造、ナノワイヤを基板上に配置するためのフローマスク、ナノワイヤを成膜するためのナノワイヤ噴霧技術、ナノワイヤにおける電子のフォノン散乱を減少または除去するための技術、および、ナノワイヤにおける表面準位を減少させるための技術が、説明される。

(もっと読む)

高周波増幅器

【課題】回路面積を増加させることなく、動作状態のトランジスタからの発熱を抑制することによって、小型化及び低コスト化を図ることができる高周波増幅器を提供する。

【解決手段】複数の単位トランジスタ3が並列に接続されたトランジスタ列からなり、高周波を増幅する増幅素子と、トランジスタ列の隣り合った単位トランジスタ3のフィンガ間にそれぞれ形成された出力整合回路の回路素子2とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、容量素子の誘電体膜の膜厚がフォトレジストの剥離の際に一部除去され、その容量値がばらつき、耐圧特性が劣化するという問題があった。

【解決手段】本発明の半導体装置では、容量素子1の下部電極8上面に誘電体膜としてのシリコン窒化膜12が形成され、シリコン窒化膜12上面に上部電極15が形成される。上部電極15は、シリコン窒化膜12を保護する多結晶シリコン膜13とシリコン膜14の積層構造から成る。この構造により、フォトレジストの剥離の際等にシリコン窒化膜12の一部が除去され、容量素子1の容量値がばらつきや耐圧劣化が防止される。

(もっと読む)

バイポーラ型半導体装置およびその製造方法

【課題】高速化されたバイポーラ型半導体装置およびその製造方法を提供する。

【解決手段】

コレクタ領域10と、コレクタ領域10上に配置されたベース領域12と、ベース領域12上に配置されたエミッタ領域14と、ベース領域12上に配置され、エミッタ領域14と共通に形成されたエミッタパッド領域34と、ベース領域12上に配置され、複数のベースコンタクトCBを介してベース領域12と接続されたベース電極20と、エミッタ領域14上に配置されたエミッタ電極18と、ベース領域12近傍のエミッタパッド領域34上に配置されたエミッタパッド電極24とを備えるバイポーラ型半導体装置およびその製造方法であり、さらにエミッタパッド領域34上に配置された絶縁層26を備えていても良く、その際、エミッタパッド電極24は、絶縁層26上に配置される。

(もっと読む)

電流シフト領域を有する半導体デバイスおよび関連方法

半導体デバイスは、第1の伝導形を有する半導体バッファ層と、バッファ層の表面上にあって第1の伝導形を有する半導体メサとを含む。さらに第2の伝導形を有する電流シフト領域が半導体メサと半導体バッファ層との間の隅に隣接して設けられ、第1と第2の伝導形が互いに異なる伝導形である。関連する方法も開示される。  (もっと読む)

(もっと読む)

1 - 20 / 84

[ Back to top ]