Fターム[5F082BA47]の内容

Fターム[5F082BA47]に分類される特許

161 - 180 / 369

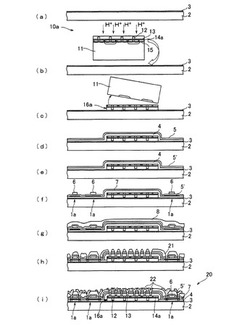

半導体装置の製造方法

【課題】非単結晶Si薄膜と単結晶Si薄膜デバイスとを形成し、高性能なシステムを集積化した半導体装置の製造方法を提供する。

【解決手段】絶縁基板2上に、単結晶Si薄膜トランジスタ16aと非単結晶Si薄膜トランジスタ1aとが形成された半導体装置20の製造方法において、表面に酸化膜、ゲートパターン、不純物イオン注入部が形成された後に平坦化されており、所定の深さに所定の濃度の水素イオンが注入された水素イオン注入部15を備えた単結晶Si基板10aを熱処理によって絶縁基板2上に接合し、さらに水素イオン注入部15において熱処理により劈開剥離した後、非晶質Si薄膜5を形成する。

(もっと読む)

半導体装置

【課題】面積の増加を抑制可能なESD保護回路を有する半導体装置を提供する。

【解決手段】入力端子11及び出力端子21を有する高周波信号の処理部と、スパイラルをなして連続したp側領域であるスパイラル状p側領域17、スパイラル状p側領域17と同様形状をなして連続したn側領域であるスパイラル状n側領域19、及びスパイラル状p側領域17とスパイラル状n側領域19とが接合した同様形状のスパイラルをなして連続したpn接合を有し、スパイラルの一端部となるスパイラル状n側領域19の端部が入力端子11に接続され、スパイラルの他端部となるスパイラル状p側領域17の端部が接地端子に接続されたESD保護素子とを備えている。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタ構造を有する静電破壊保護素子のホールド電圧を従来に比して高くするとともに、当該素子のサイズを抑える技術を提供することを目的とする。

【解決手段】エピタキシャル層2の表面にベース領域(P不純物層4)が形成され、P不純物層4の表面にエミッタ領域(N+不純物層5)が形成され、エピタキシャル層2とN+不純物層6とから成るコレクタ領域が構成されている。ベース電極8とベース領域(P不純物層4)の接続部が、ベース領域(P不純物層4)のコレクタ電極10側の端部とエミッタ領域(N+不純物層5)との間に位置する。つまり、コレクタ・ベース・エミッタの順で各電極が構成されている。ベース電極8とエミッタ電極9とは不図示の配線を介して接続されている。また、エピタキシャル層2を複数の島領域に分離するためのP+分離層11が形成されている。

(もっと読む)

半導体装置

【課題】 エミッタ-ベース間に発生する順方向電圧の温度特性を利用するバイポーラトランジスタにおいて、素子面積を縮小することを目的とする。

【解決手段】 エミッタ-ベース間に発生する順方向電圧の温度特性を利用するバイポーラトランジスタにおいて、第二の導電型であるベース電極用高濃度不純物領域と、第一の導電型であるコレクタ電極用高濃度不純物領域とを直接に接触させ、不要な分離領域を形成しないことで素子面積を縮小する。

(もっと読む)

半導体装置及びその製造方法

【課題】 高い耐圧性と低いオン抵抗を実現する両導電型能動素子を備えた集積型半導体装置を提供する。

【解決手段】 半導体装置において、一導電型を有するシリコン基板を保持基板とし、保持基板の上に、埋め込み絶縁膜と、半導体層とを有するSOI基板の半導体層に、電子及び正孔をそれぞれ主キャリアとするコンプリメンタリ型能動素子が集積される。能動素子に印加した電圧が横方向に印加される一導電型の不純物層の近傍に、埋め込み絶縁膜を介して一導電型を有する保持基板内に対向して配置される逆導電型の領域が設けられ、一導電型を有する保持基板と逆導電型の領域との間に、電源電圧に相当する電圧が逆バイアスで印加され、保持基板と前記埋め込み絶縁膜との界面に空乏層が広がる。

(もっと読む)

半導体装置とその製造方法

【課題】 複数個の半導体素子を備えている半導体装置において、その半導体装置のサイズを小さくする技術を提供する。

【解決手段】 不純物注入工程では、半導体基板9の表面にn型半導体領域13とp型半導体領域14が隣接して出現する関係に不純物の注入範囲を管理して、不純物を半導体基板9に注入する。熱処理工程では、半導体基板9を加熱して半導体基板9に注入した不純物12、14を活性化する。トレンチ形成工程では、半導体基板9の表面に隣接して出現しているn型半導体領域13とp型半導体領域14の双方を分断して一巡するととともに半導体基板9の表面から半導体基板9の裏面に向けて不純物の注入範囲12、14を貫通する深さにまで伸びているトレンチ15を形成する。絶縁膜形成工程では、トレンチ15内に絶縁膜を形成する。

(もっと読む)

半導体装置

【課題】 コレクタ・エミッタ間の耐圧が異なる複数のバイポーラトランジスタを同一基板上に容易に混載可能な技術を提供ことにある。

【解決手段】 同一基板上に高周波バイポーラトランジスタと高耐圧バイポーラトランジスタとを混載した半導体装置において、高周波バイポーラトランジスタと高耐圧バイポーラトランジスタは、同一膜厚のエピタキシャル成長層上に形成されており、また、同一プロセスにより形成された同一の不純物プロファイルを持つ埋め込みコレクタ領域を備えた構造であり、高周波バイポーラトランジスタのベース直下には埋め込みコレクタ領域が存在し、高耐圧バイポーラトランジスタのベース直下には埋め込みコレクタ領域及びSIC領域が存在せずに、高耐圧バイポーラトランジスタのベース領域とコレクタプラグ領域との距離が高周波バイポーラトランジスタの同距離と比べて等しいか大きいことを特徴としている。

(もっと読む)

合併したバイポーラ回路およびCMOS回路とその製造法

【課題】高特性の合併したバイポーラ回路とCMOS回路とをCMOS処理工程だけのコストで製造する方法および回路を提供する。

【解決手段】BiCMOS集積回路を製造する方法は、バイポーラ・トランジスタのベース領域211とNチヤンネルMOSトランジスタのP形ウエル212とを1つの注入段階で作成する段階と、バイポーラ・トランジスタのコレクタ接触体ウエル213とPチヤンネルMOSトランジスタのN形ウエル208とを1つの注入段階で作成する段階とを有する。

(もっと読む)

トランジスタ素子

【課題】電流利得が高いトランジスタ素子を提供する。

【解決手段】基板2上にヘテロバイポーラトランジスタ3が形成され、該ヘテロバイポーラトランジスタ3上に高電子移動度トランジスタ4が形成されたトランジスタ素子1において、上記ヘテロバイポーラトランジスタ3のベース層8の層厚が120nm以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】チップ面積を従来に比して小さくすることが可能な、半導体素子の分離技術を提供することを目的とする。

【解決手段】N−半導体層3の表面にN+半導体層4、P半導体層5,N+半導体層6を形成する。次に、N+半導体層4の内側に開口部を有するレジスト層7を形成する。次に、当該レジスト層7をマスクとして半導体基板1を選択的にエッチングしてN+半導体層4を分断する溝8を形成する。分断されたN+半導体層4をN+半導体層4a,4bとする。次に、溝8の内部をシリコン酸化膜等の絶縁膜9で埋設する。次に、P半導体層5(ベース領域),N+半導体層6(エミッタ領域),N+半導体層4a,4b(コレクタ領域)、の各表面に至るコンタクトホールを有するシリコン酸化膜10を形成する。次に、各コンタクトホール内にベース電極11,エミッタ電極12,コレクタ電極13を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の中の不純物領域を熱拡散する際に、その横方向拡散を抑制して半導体集積回路の微細化を実現する。

【解決手段】絶縁膜2上に第2のホトレジスト5を形成する。第2のホトレジスト5は、P型の不純物領域4の両側に、P型の不純物領域4に部分的にオーバーラップする領域に第2の開口部K2を有するように形成される。第2のホトレジスト5をマスクとして、絶縁膜2をエッチングし、更にその下の半導体基板1の表面をエッチングすることで、P型の不純物領域4を部分的に除去する。そして、第2のホトレジスト5をマスクとして、P型の不純物領域4が除去された半導体基板1の表面に、リン(P+)をイオン注入して、P型の不純物領域4に隣接したN型の不純物領域6を形成する。その後、第2のホトレジスト5を除去した後に、P型の不純物領域4及びN型の不純物領域6の熱拡散を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の中に分離領域を熱拡散により形成する際に、その横方向拡散を抑制して、半導体集積回路の微細化を実現する。

【解決手段】第3のホトレジスト24をマスクとして、第3の開口部K3から、ボロン(B+)をエピタキシャル層21にイオン注入してP型の不純物領域25を形成する。そして、シリコン酸化膜23上に、P型の不純物領域25と部分的にオーバーラップする領域に第4の開口部K4(リン注入領域)を有する第4のホトレジスト26を形成する。第4のホトレジスト26をマスクとして、P型の不純物領域25が除去されたエピタキシャル層21の表面にリン(P+)をイオン注入して、P型の不純物領域25に隣接したN型の不純物領域28を形成する。その後、熱拡散を行うことにより、エピタキシャル層21の中にP型の上分離領域29が形成され、この上分離領域29と下分離領域22とは連結されて分離領域30が形成される。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタを含む半導体装置において、耐圧を向上させる。

【解決手段】バイポーラトランジスタを含む半導体装置100において、ベース領域を、第1のベース領域114およびその周囲に設けられ、第1のベース領域114よりも不純物濃度の低い第2のベース領域116の二層構造とする。第2のベース領域116は、第1のベース領域114よりも浅く形成されている。

(もっと読む)

半導体装置とその製造方法

【課題】 ボディ領域の導電型とベース領域の導電型が異なるユニポーラトランジスタとバイポーラトランジスタを同一の半導体基板に簡単に作り込む。同一深さでの不純物イオンの注入密度が場所によって相違する不純物注入パターンを一度の不純物注入工程で得る。

【解決手段】 活性層14の第1区画領域20にはp型の深層7aをリサーフ領域27とするとともにn型の浅層6aをドリフト領域26とするユニポーラ型の半導体素子2が形成されており、第2区画領域40にはp型の深層7aを埋め込みコレクタ領域47とするとともにn型の浅層6aをベース領域46とするバイポーラ型の半導体素子4が形成されている。同一深さでの不純物イオンの注入密度が場所によって相違する注入パターンを形成するために、一方の領域にフィールド酸化膜を形成しておいて両領域に同時に不純物イオンを注入する。

(もっと読む)

半導体装置

【課題】可制御電流が大きく、低損失のパワー半導体装置に適したアセンブリ構造を提供すること。

【解決手段】金属基板125と、絶縁板126と、金属膜7とを備える。金属基板125上に、ワイドギャップ半導体層からなるバイポーラスイッチング素子20を備える。金属膜7上に、n型ワイドギャップ半導体層を含むダイオード素子13を備える。バイポーラスイッチング素子20の低電位側の主電極32は、金属基板125に直接に半田付けされている。一方、バイポーラスイッチング素子20の高電位側の主電極29は、金属膜7に配線34、7aを介して電気的に接続されている。ダイオード素子13の低電位側の主電極32は、金属膜7に直接に半田付けされている。一方、ダイオード素子13の高電位側の主電極6は、金属基板125に配線8を介して電気的に接続されている。

(もっと読む)

半導体装置

【課題】オン抵抗を大幅に低減することが可能な新しい動作原理に基づく半導体装置を提供する。

【解決手段】この半導体装置1は、n+型のシリコン基板2と、シリコン基板2上に配置されたp型の半導体層3と、半導体層3上に配置され、複数のトレンチ4aを有するとともに、隣接するトレンチ4a間の各領域がチャネル10となるn型の半導体層4と、半導体層4のトレンチ4aに配置された埋め込み電極6とを備え、シリコン基板2、半導体層3および半導体層4により、バイポーラトランジスタが形成されており、埋め込み電極6が負電位である場合に、トレンチ4aから隣接するトレンチ4aにわたって空乏層11が形成されることにより、チャネル10がオフ状態となり、埋め込み電極6が正電位である場合に、隣接するトレンチ4a間の全ての領域において、空乏層11が形成されないことにより、チャネル10がオン状態となる。

(もっと読む)

垂直型電流制御型シリコン・オン・インシュレータ(SOI)デバイス及びそれを形成する方法

【課題】 CMOS集積回路(IC)のための静電放電(ESD)保護デバイスとして用いるのに適した電流制御シリコン・オン・インシュレータ(SOI)デバイスを提供すること。

【解決手段】 垂直型シリコン制御整流器(SCR)、垂直型バイポーラ・トランジスタ、垂直型キャパシタ、抵抗器及び/又は垂直型ピンチ抵抗器のようなデバイスを有するシリコン・オン・インシュレータ(SOI)集積回路(IC)チップ、及びそれらのデバイスを作製する方法である。デバイスは、SOI表面層及び絶縁体層を通って基板に達するシード孔内に形成される。例えばN−型埋め込み拡散部が、基板内のシード孔を通って形成される。ドープされたエピタキシャル層が、埋め込み拡散部上に形成され、このドープされたエピタキシャル層は、例えばP−型層及びN−型層などの多数のドープ層を含むことができる。ドープされたエピタキシャル層上に、例えばP−型のポリシリコンを形成することができる。コンタクト・ライナ内に、埋め込み拡散部へのコンタクトが形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】コレクタ耐圧の低下を防止し、コレクタ抵抗を低減させることが可能な半導体装置及びその製造方法を提供する。

【解決手段】半絶縁性GaAs基板101の第1領域上に形成されたHBTと、半絶縁性GaAs基板101の第2領域上に形成されたHFETとを備え、HBTは、第1領域上に順次形成された、第1導電型のエミッタ層103、エミッタ層103よりバンドギャップの小さい第2導電型のベース層104、第1導電型又はノンドープのコレクタ層105、及びコレクタ層105より高不純物濃度の第1導電型のサブコレクタ層106を有し、HFETは、エミッタ層103の一部により構成された電子供給層110と、電子供給層110の下方に形成されたチャネル層102とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】同一半導体基板上にフォトダイオードとトランジスタとを混載した半導体装置の動作速度の更なる高速化と、フォトダイオードにおけるパルスの応答遅延の改善を図る。

【解決手段】第一導電型の半導体基板と、この半導体基板上に形成された第一導電型のエピタキシャル層と、第一導電型のエピタキシャル層上に形成された第二導電型のエピタキシャル層と、第一導電型のエピタキシャル層内に形成された第二導電型のコレクタ領域を有するトランジスタと、第一導電型のエピタキシャル層上に第二導電型の半導体領域を形成してなるフォトダイオードとを有する半導体装置において、コレクタ領域の下方における半導体基板表面の不純物濃度を、コレクタ領域と第一導電型のエピタキシャル層との接合により生じる空乏層の下端が半導体基板に達する不純物濃度とし、フォトダイオードの下方における半導体基板に、トラップ準位を形成した。

(もっと読む)

半導体集積回路

【課題】バルクシリコン基板で動作が確認されている設計資産を最小限のレイアウト変更によりSOIデバイスへ流用し、プロセスコストが増加しない完全空乏型MOSトランジスタと混載可能な半導体集積回路を提供する。

【解決手段】バルクシリコンデバイスの設計資産を利用して、SOIデバイスの回路を形成する半導体集積回路であって、バルクシリコンデバイスにおけるバイポーラトランジスタを、埋め込み酸化膜012上に形成するダイオードD1、D2に変えて回路構成したことを特徴とする。

(もっと読む)

161 - 180 / 369

[ Back to top ]