Fターム[5F082BA47]の内容

Fターム[5F082BA47]に分類される特許

101 - 120 / 369

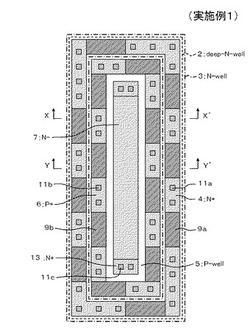

半導体装置

【課題】制御電極層のない素子のレイアウトサイズを増加させることなく、CMPによる平坦化での過研磨を防ぐことができる半導体装置を提供すること。

【解決手段】半導体基板上に配されるとともに拡散層で構成された拡散層抵抗7と、拡散層抵抗7の外周を囲むように配されるとともに拡散層で構成されたPウェルコンタクト6と、Pウェルコンタクト6の外周を囲むように配されるとともに拡散層で構成されたNウェルコンタクト4と、を備えた抵抗セルを有する半導体装置であって、Pウェルコンタクト6及びNウェルコンタクト4は、それぞれ複数に分断されており、隣り合うPウェルコンタクト6間の領域に制御電極層9bが配されてPウェルコンタクト6と制御電極層9bが交互に配置され、隣り合うNウェルコンタクト4間の領域に制御電極層9aが配されてNウェルコンタクト4と制御電極層9aが交互に配置されている。

(もっと読む)

半導体デバイス用基板、半導体デバイス装置、設計システム、製造方法、および設計方法

【課題】結晶薄膜の膜質および膜厚を均一にする。

【解決手段】半導体デバイスを形成するためのデバイス用薄膜と、デバイス用薄膜を囲み、デバイス用薄膜の前駆体が結晶に成長することを阻害する阻害部と、前駆体が結晶に犠牲成長することによって形成された犠牲成長部であって、デバイス用薄膜の周辺に阻害部で隔てられて設けられた犠牲成長部と、犠牲成長部の上部を覆い、かつデバイス用薄膜の上部を露出する保護膜を備えた。保護膜はポリイミドであってもよい。

(もっと読む)

ESD保護回路およびESD保護回路を有する半導体集積回路

【課題】正・負のどちらのサージ電圧に対してもESD保護回路として対応することができ、かつ素子面積の小さいESD保護回路を提供する。

【解決手段】ESD保護回路は、コレクタ111が第1の端子T1に接続され、エミッタ112が第2の端子T2に接続され、ベース113が抵抗120を介して第2の端子T2に接続されたバイポーラトランジスタ110と、ドレイン101がベース113に接続され、ソース102と、ゲート103と、バックゲート104が第2の端子T2に接続されたnMOSトランジスタ100を有する。

(もっと読む)

n型ベースを有するバイポーラトランジスタ及びその製造方法

【解決手段】ベースコンタクト接続部(12)、エミッタ部(4、5)及びコレクタ部がn層(3)上に配置され、当該n層は、更なるnpnバイポーラトランジスタために用いることができる。当該コレクタ部はエミッタ部に対して側方に配置され、当該エミッタ部及びコレクタ部の少なくとも一方は、当該n層の表面領域上でショットキーコンタクト(14)を備える。 (もっと読む)

トランジスタ型保護素子、半導体集積回路およびその製造方法

【課題】保護素子のターンオン電圧を決める制約を少なくする。

【解決手段】半導体基板1、Pウェル2、ゲート電極4、ソース領域5、ドレイン領域6および抵抗性降伏領域8を有する。抵抗性降伏領域8はドレイン領域6に接し、ゲート電極4直下のウェル部分と所定の距離だけ離れたN型半導体領域からなる。ドレイン領域6または抵抗性降伏領域8に接合降伏が発生するドレインバイアスの印加時に抵抗性降伏領域8に電気的中性領域(8i)が残るように、抵抗性降伏領域8の冶金学的接合形状と濃度プロファイルが決められている。

(もっと読む)

静電気保護素子

【課題】表示パネル駆動用の半導体集積装置に適した、保持電圧が高い静電保護素子を提供する。

【解決手段】静電保護素子は、P型半導体基板1の表面側に形成されたNウェル領域2と、Nウェル領域の上に形成された第1のP型高濃度不純物領域8と、P型半導体基板の表面上に形成されたN型高濃度不純物領域5と、Nウェル領域とP型半導体基板1との境界を跨いでNウェル領域と前記P型半導体基板との双方に接触して形成された第2のP型高濃度不純物領域6とを備えている。すなわち、第2のP型高濃度不純物領域6がP型半導体基板1と接触するため、P型半導体基板1におけるP型不純物の濃度が高くなり、従って静電気保護素子の保持電圧が高くなる。

(もっと読む)

ポリエミッタ型バイポーラトランジスタ、BCD素子、ポリエミッタ型バイポーラトランジスタの製造方法及びBCD素子の製造方法

【課題】複合高電圧素子工程を用いたポリエミッタ型バイポーラトランジスタ及びその製造方法、BCD(複合高圧)素子及びその製造方法を提供する。

【解決手段】実施の形態に係るポリエミッタ型バイポーラトランジスタは、半導体基板100の上側の一部に形成された埋込層110と、上記半導体基板の上に形成されたエピ層120と、上記エピ層に形成され、上記埋込層と連結されるコレクタ領域130と、上記エピ層の上側の一部に形成されたベース領域140と、上記ベース領域の基板の表面に形成され、ポリシリコン材質からなるポリエミッタ領域170と、を含む。実施の形態に係るBCD素子は、ポリシリコン材質からなるポリエミッタ領域を含むポリエミッタ型バイポーラトランジスタを含み、上記バイポーラトランジスタと同一な単一ウエハ上に形成されたCMOSとDMOSのうちの1つ以上のMOSを含む。

(もっと読む)

静電気保護素子

【課題】特殊な工程や、保護抵抗の挿入なしに被保護回路を保護できる静電気保護素子を提供する。

【解決手段】P型の半導体基板1と、半導体基板1に形成された、N型の第1不純物層3を備える。第1不純物層3内には、ゲートとして動作するP型の第2不純物層5を備える。第2不純物層5には、カソードとして動作するN型の第3不純物層6を備える。また、第2不純物層5から一定距離離間した第1不純物層3内には、N型の第4不純物層4を備える。第4不純物層4内には、アノードとして動作するP型の第5不純物層8と、N型の第6不純物層9とを備える。そして、本静電気保護素子は、第4不純物層4の不純物濃度が第1不純物層3の不純物濃度よりも高く、かつ第4不純物層4の底部が第2不純物層5の底部より深くなっている。

(もっと読む)

発光素子チップ、露光装置および画像形成装置

【課題】本発明は、発光素子アレイの構造を利用して信号線の引き回しの複雑化を軽減した発光素子チップを提供する。

【解決手段】発光素子チップ51aは、GaAs系の半導体で構成され、基板200上に形成されたpnpn構造からなる、発光部120の発光サイリスタ401と、設定部130の転送サイリスタ402と、制御部140の論理演算素子403とを備え、基板200上にp型の第1半導体層201とn型の第2半導体層202と、p型の第3半導体層203と、n型の第4半導体層204とを積層し、その後、予め定められた箇所をエッチングして形成される。

(もっと読む)

半導体装置とその製造方法

【課題】 エミッタ注入効率が大きく、差動増幅回路の入力トランジスタとして利用可能で、かつBi−CMOSプロセスにおいてMOSトランジスタと同一基板上に搭載することが可能なバイポーラトランジスタの構造とその製造方法を提供する。

【解決手段】 半導体基板1上に第二導電型の深いウェル層2が形成され、深いウェル層2よりは浅い所定の深さで第一導電型の埋め込み層3が形成され、バイポーラトランジスタのエミッタ領域が、第一導電型の埋め込み層3の上に、第二導電型のウェル層4、及びMOSトランジスタのソース・ドレイン領域と同時形成される高濃度の第二導電型の不純物層15の2層構造として形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】外部からの高周波ノイズに対して誤動作しにくい半導体装置およびその製造方法を提供する。

【解決手段】n型コレクタ層11上に配置されたp型ベース層12bと、p型ベース層12b上に配置されたn型エミッタ層13bと、p型ベース層12b上にp型ベース層12bを包囲するように配置されたn型ベースコンタクト層21と、n型コレクタ層11上にp型ベース層12bと離隔して配置されたp型アノード層12cと、n型エミッタ層13bに接続されたエミッタ電極16cと、p型ベース層12bおよびn型ベースコンタクト層21に接続されたベース電極16aと、p型アノード層12cに接続され、かつエミッタ電極16cと共通接続されたアノード電極16bと、エミッタ電極16cとベース電極16a間に接続された第1抵抗R1と、ベース電極16aに接続された第2抵抗R2とを備える。

(もっと読む)

ハイブリッド基板回路

【課題】3−5集積回路とシリコン集積回路とは別々の集積回路上に設けられてきた。3−5集積回路とシリコン集積回路等の相違する基板を必要とする複数の回路を1つの集積回路において組み合わせることを可能にするハイブリッド基板回路を提供すること。

【解決手段】ハイブリッド基板回路は、第1半導体材料の第1領域と、埋め込み酸化層および埋め込み酸化層の上方の第2半導体材料を含んでいる第2領域と、第1半導体材料内に形成された第1回路と、第2半導体材料内に形成された第2回路と、第1回路と第2回路との間のシャロー・トレンチ・アイソレーション領域103と、を含んでいる。第1半導体材料はシリコンを含み、第2半導体材料はシリコンを含んでいない。第1回路はCMOS回路101であり、第2回路は高電子移動度トランジスタ回路102である。

(もっと読む)

トランジスタデバイス及びその製造方法

トランジスタデバイス(600)の製造方法であって、この製造方法が、基板(102)中に溝(106)を形成するステップと、この溝(106)を電気絶縁材料(202)により部分的にのみ充填するステップと、部分的にのみ充填された溝(106)を介して前記トランジスタデバイス(600)のバイポーラトランジスタ(608)のコレクタ領域(304)にインプラント処理するステップとを有するトランジスタデバイスの製造方法を提供する。  (もっと読む)

(もっと読む)

ESD保護素子および該ESD保護素子を設けた半導体装置

【課題】 本発明の目的はESD保護素子の平面サイズの増大を図ることなく、良好なESD特性を得る。

【解決手段】 第1導電型の第1半導体領域1と、所定の間隔を有してそれぞれ設けられた第1電極11および第2電極12と、第1半導体領域の表面側に設けられた第2導電型の第2半導体領域2と、当該領域の表面側にそれぞれ設けられた第1導電型の第3半導体領域3および第4半導体領域4と、第3半導体領域内であって当該領域の表面側に設けられて、第1電極と電気的に接続された第2導電型の第5半導体領域5と、第4半導体領域内であって当該領域の表面側に設けられて、第2電極と電気的に接続された第2導電型の第6半導体領域6と、を備えており、第2半導体領域、前記第3半導体領域および前記第4半導体領域は、それぞれが浮遊電位に保たれていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】同一基板上に形成された縦型PNPトランジスタとNPNトランジスタの両方の特性向上が図られた半導体装置を提供する。

【解決手段】半導体装置はPNPトランジスタ50を備えている。PNPトランジスタ50は、第1のP型コレクタ領域3bと、第1のP型コレクタ領域3bの底面を覆い、第1のP型コレクタ領域3bの不純物濃度のピークよりも深い位置に不純物濃度のピークを有する第1のN型埋め込み領域2と、第1のP型コレクタ領域3b上に形成された第2のP型コレクタ領域5bとを備えている。第1のP型コレクタ領域3bの側面もN型領域に囲まれている。このため、PNPトランジスタ50におけるパンチスルーの発生が抑えられるとともに、コレクタ領域内のキャリア通過経路を短くしてコレクタ抵抗の低減を図ることができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】トランジスタを短絡させることなく、シリサイド層を形成することができる半導体装置の提供。

【解決手段】バイポーラトランジスタ形成領域100と、CMOSトランジスタ形成領域200とを分離し、絶縁層52a,52bを形成し、上方に導電層56a,56bを形成し、側壁54a,54bを形成して、バイポーラトランジスタ形成領域100に、短絡防止部50aを形成すると同時に、CMOSトランジスタ形成領域200にゲート50bを形成する。バイポーラトランジスタのエミッタ領域40a、コレクタ領域40bおよびベース領域42aおよびCMOSトランジスタのソース領域40c,42bおよびドレイン領域40d,42cを形成し、各領域の上にシリサイド層60を形成する。短絡防止部50aは、エミッタ領域40a、コレクタ領域40bおよびベース領域42aのうち、いずれか2つの領域の間に位置する半導体基板10の上方に形成される。

(もっと読む)

半導体双方向スイッチング装置

【課題】本発明は、スーパージャンクション構造を有し双方向スイッチングが可能な半導体双方向スイッチング装置を提供する。

【解決手段】二つの主電極の両方に電子とホールの制御部を設け、スーパージャンクションを構成するn形半導体層とp形半導体層における電流を制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】追加部材を形成することなく表面保護膜の端部での剥がれを防止でき、チップエッジからの水分浸入を防止して信頼性(耐湿性)を向上できる半導体装置を提供する。

【解決手段】この半導体装置では、エピタキシャル層4Aを覆う表面保護膜11が高抵抗GaAs層(素子間絶縁層)5の外周側の外周エピタキシャル層4A−1の一部を覆って上記一部に接しているので、表面保護膜11の端部の密着性が向上して外部からの水分侵入を防止できる。

(もっと読む)

半導体装置

【課題】絶縁ゲートバイポーラトランジスタのスイッチング特性および低オン抵抗を維持しつつ耐圧特性を改善しかつ占有面積を低減する。

【解決手段】絶縁ゲートバイポーラトランジスタ(IGBT:2)のターンオフ時のホール流入を抑制するPチャネルMOSトランジスタ(PQ)のゲート電極ノード(6)に対し、IGBTのオフ状態時においてゲート絶縁膜に印加される電圧を緩和する電圧緩和素子(1)を設ける。

(もっと読む)

接合型電界効果トランジスタ

【課題】 基板が低濃度の半導体基板のみからなるJ−FETは、静電破壊耐量は高いが、ノイズ電圧が大きく、ノイズ特性のばらつきも大きい問題があった。一方、ノイズ対策として、高濃度の半導体基板に低濃度の半導体層を積層した基板構造のJ−FETでは、ゲート抵抗の低減によりノイズ電圧を小さくできノイズ特性も安定する反面、静電破壊耐量が劣化する問題があった。

【解決手段】 高濃度半導体基板に低濃度の第1半導体層と、第1半導体層より高濃度の第2半導体層を積層する基板構造とする。これにより静電破壊耐量を劣化させない範囲でノイズ特性のばらつきを抑え、ノイズ電圧を小さくすることができる。また同時にノイズ特性に影響を与えない範囲で静電破壊耐量を向上させることができる。従って、従来構造と比較して市場要求に比較的柔軟に対応できるJ−FETを提供できる。

(もっと読む)

101 - 120 / 369

[ Back to top ]