Fターム[5F082BC11]の内容

Fターム[5F082BC11]の下位に属するFターム

ショットキ (20)

Fターム[5F082BC11]に分類される特許

61 - 80 / 184

接合型電界効果トランジスタ

【課題】 基板が低濃度の半導体基板のみからなるJ−FETは、静電破壊耐量は高いが、ノイズ電圧が大きく、ノイズ特性のばらつきも大きい問題があった。一方、ノイズ対策として、高濃度の半導体基板に低濃度の半導体層を積層した基板構造のJ−FETでは、ゲート抵抗の低減によりノイズ電圧を小さくできノイズ特性も安定する反面、静電破壊耐量が劣化する問題があった。

【解決手段】 高濃度半導体基板に低濃度の第1半導体層と、第1半導体層より高濃度の第2半導体層を積層する基板構造とする。これにより静電破壊耐量を劣化させない範囲でノイズ特性のばらつきを抑え、ノイズ電圧を小さくすることができる。また同時にノイズ特性に影響を与えない範囲で静電破壊耐量を向上させることができる。従って、従来構造と比較して市場要求に比較的柔軟に対応できるJ−FETを提供できる。

(もっと読む)

接合型電界効果トランジスタ

【課題】 基板が低濃度の半導体基板のみからなるJ−FETは、静電破壊耐量は高いが、ノイズ電圧が大きく、ノイズ特性のばらつきも大きい問題があった。一方、ノイズ対策として、高濃度の半導体基板に低濃度の半導体層を積層した基板構造のJ−FETでは、ゲート抵抗の低減によりノイズ電圧を小さくできノイズ特性も安定する反面、静電破壊耐量が劣化する問題があった。

【解決手段】 高濃度半導体基板の条件を、所望の静電破壊耐量が得られる比抵抗及び厚みとし、これに低濃度の半導体層を積層した基板構造とする。これにより静電破壊耐量を劣化させない範囲でノイズ特性のばらつきを抑え、ノイズ電圧を小さくすることができる。また同時にノイズ特性に影響を与えない範囲で静電破壊耐量を向上させることができる。従って、従来構造と比較して市場要求に比較的柔軟に対応できるJ−FETを提供できる。

(もっと読む)

保護回路

【課題】 プロセスの微細化や低電圧化に伴うデバイス破壊耐性の低下に対して、外来サージ等により電源間に高電圧が印加されることに起因した静電破壊やラッチアップから半導体集積回路装置を保護する保護回路を提供する必要がある。

【解決手段】 電源VDDにソース端子が接続され電源GNDを基準として制御回路2が生成した制御信号VG1にゲート端子が接続されたP型MOSトランジスタMP1のドレイン端子は、電源GNDに一端が接続された抵抗R1のもう一端と電源VDDと電源GNDにそれぞれドレイン端子とソース端子が接続されたN型MOSトランジスタMN1のゲート端子に内部信号VG2として接続された構成にて、電源間に任意電圧以上の電圧が印加された場合に電源間を短絡する。

(もっと読む)

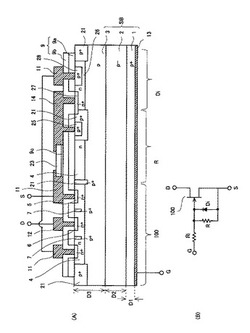

半導体装置、及び該半導体装置を用いたエネルギー伝達装置

【課題】ドレイン電極をソース電極に対して負バイアスすることがあっても、半導体集積回路においてラッチアップが発生することを防止できるエネルギー伝達装置、及び該エネルギー伝達装置を実現可能な半導体装置を提供する。

【解決手段】第1の半導体基板に形成された半導体装置24と、第2の半導体基板の表面に形成された第2導電型の逆電流防止層、及び第2の半導体基板中に形成され逆電流防止層を覆う第1導電型のウェル層を含む逆電流防止ダイオード41を備えた半導体集積回路48と、直流電圧源52と、変圧器60とを備え、変圧器60は、半導体装置24及び直流電圧源52と直列に接続される一次巻線53と、負荷と接続される第1二次巻線54とを含み、変圧器60の第1二次巻線54から負荷へ電力が供給されるように構成されている。半導体装置24の第2ドレイン電極(TAP電極)は、半導体集積回路48の逆電流防止層と電気的に接続している。

(もっと読む)

半導体装置

【課題】クランプダイオードにおいて、リーク電流を抑制しながら、その動作電圧を下げることを可能にする。

【解決手段】N−型の半導体層2の表面には、P−型の拡散層5が形成されている。P−型の拡散層5の表面にN+型の拡散層6が形成されている。P−型の半導体層5の表面にはN+型の拡散層6に隣接してP+型拡散層7が形成されている。P−型の拡散層5に隣接したN−型の半導体層2の表面にはN+型の拡散層8が形成されている。N+型の拡散層6上の絶縁膜9にはコンタクトホールが開口され、このコンタクトホールを通して、N+型の拡散層6と電気的に接続されたカソード電極10が形成されている。P+型の拡散層7及びN+型の拡散層8上の絶縁膜9には、それぞれコンタクトホールが開口され、各コンタクトホールを通して、P+型の拡散層7とN+型の拡散層8とを接続する配線11(アノード電極)が形成されている。

(もっと読む)

サージ保護素子

【課題】周辺温度や使用環境に依らずに安定したブレークダウン電圧を与え得るサージ保護素子を提供する。

【解決手段】サージ保護素子10は、第1の導電型の不純物を含むベース領域21と、第2の導電型の不純物を含む第1半導体領域23と、第2の導電型と同じ導電型の不純物を含む第2半導体領域24と、この第2半導体領域24よりも低い不純物濃度を有する高抵抗領域22とを有する。第1半導体領域23はベース領域21の上面側で接合され、第2半導体領域24はベース領域21の下面側で接合されている。高抵抗領域22は、ベース領域21および第2半導体領域24の双方に電気的に接続されている。

(もっと読む)

半導体装置

【課題】正のサージが印加された場合に、従来の半導体装置よりもブレークダウン電圧を高くすることなくサージ電流による発熱を抑制することができ、サージ保護素子が破壊されることを防止することができる半導体装置を提供する。

【解決手段】コレクタ層7に第1のトレンチ8を形成し、第1のトレンチ8の底面および側壁のうち底面側の端部を覆い、第1のトレンチ8の底面からコレクタ層7の裏面方向と第1のトレンチ8の底面と平行な方向、および第1のトレンチ8の底面の端部からコレクタ層7の表面方向に不純物を拡散させることにより高濃度層9を形成する。

(もっと読む)

半導体装置及び半導体集積装置

【課題】部品点数の削減及び実装面積を小さくすることができる半導体装置及び半導体集積装置を提供する。

【解決手段】トランジスタQ1に形成されたコレクタ電極は、リードフレームによりコレクタ端子Tcに直接接続してあり、エミッタ電極は、ボンディングワイヤによりエミッタ端子Teに直接接続してある。また、トランジスタQ1のベース電極には、抵抗素子R1を介して接続された第1ベース端子Tb1と、ベース電極に直接接続した第2ベース端子Tb2とを備えている。また、トランジスタQ1のベース電極とエミッタ電極との間には抵抗素子R2を接続してある。トランジスタ装置10は、外部との接続用の端子を4つ備える4端子構造を有する。

(もっと読む)

集積回路装置および電子機器

【課題】 外付け部品を用いることなく、入力端子に印加される負極性のサージ電圧による集積回路の破壊および誤動作を防止することができる集積回路装置および電子機器を提供する。

【解決手段】 ESD保護素子11は、エミッタが入力端子13に接続され、コレクタが電源Vccに接続され、ベースが抵抗素子112を介して入力端子13に接続されているNPNトランジスタ111と、一端がトランジスタ111のベースに接続され、他端が入力端子13に接続されている抵抗素子112とを備えている。さらに、集積回路1は、P型半導体から成る基板と、Nウェルを一部に有し、隣接するNウェルの間にP型半導体から成るP型半導体部が介在されて構成されている複数の回路形成素子とを備える。集積回路1を形成する回路形成素子のうち入力端子13に接続されている回路形成素子は、Nウェルを除く残余の部分である。

(もっと読む)

半導体装置

【課題】1チップサイズが小さく、しかも安価に具現できる高性能な半導体装置を提供すること。

【解決手段】この半導体装置は、一半導体基板構造(エピタキシャル層11を有するP型半導体基板10)上で過電圧に対するゲート電極保護のためのツェナダイオード(保護素子)2が一つの素子領域E2においてDMOSトランジスタ1に接続されて構成された素子一体化構造となっている。ツェナダイオード2は、DMOSトランジスタ1のドレイン電極領域内のDMOSトランジスタ1とは異なる濃度(或いは同濃度であっても良い)で分離された拡散領域(ツェナダイオード2形成用のP型拡散領域)上に形成されて成る。又、この半導体装置の場合、一つの素子領域E2の両側にだけ素子分離領域E1を設ければ良いので、素子領域E2及び素子分離領域E1の両方が可能な限り少ない個数で占有面積の小さな構造を持つ。

(もっと読む)

保護回路

【課題】素子の個数を減らして実装面積を小さくすることができる保護回路を得る。

【解決手段】ダイオードD11(第1ダイオード)のアノードが端子Tに接続されている。ダイオードD12(第2ダイオード)のアノードがGNDに接続され、カソードがダイオードD11のカソードに接続されている。トランジスタQ11のコレクタが端子Tに接続され、エミッタがGNDに接続されている。ダイオードD11,D12のカソードからトランジスタQ11のベースに向けて順方向にダイオードD13〜D15(第3ダイオード)が直列に接続されている。

(もっと読む)

複合半導体装置

【課題】同一の半導体層上に、半導体素子とセンサ素子とが形成され、半導体素子の温度が、高い応答速度でセンサ素子により検出される複合半導体装置を提供すること。

【解決手段】同一の半導体層上に、FRDとSBDとが並存するように形成した複合半導体装置は、

FRD11が、N型の第1半導体層1と、第1半導体層1上に島状に形成され、且つ、第1半導体層1とPN接合が形成されるP型の第2半導体層2と、第2半導体層2上に形成され第2半導体層2と電気的に接続される第1電極5と、で構成され、

SBD12が、第1半導体層1と、第1半導体層1上に形成され、且つ、第1半導体層1との間にショットキー接合が形成される第2電極6と、で構成され、

第2電極6、又は、第2電極6と接触する伝熱板が、平面的に見て第1電極5と重なるように延伸して形成されている。

(もっと読む)

半導体装置

【課題】本発明は、高電圧が印加される電源端子と、電源端子と電気的に接続されたクランプ回路と、クランプ回路と電気的に接続され、低電圧で駆動する内部回路とを備えた半導体装置に関し、半導体装置の面内におけるクランプ回路の占有面積を小さくして、半導体装置の小型化を図ることを課題とする。

【解決手段】高電圧VDD1が印加される電源端子11と電気的に接続されたクランプ回路13と、クランプ回路13と電気的に接続され、高電圧VDD1よりも低い基準電圧VREFで駆動する内部回路14と、を備えた半導体装置10であって、NPN型バイポーラトランジスタ21を用いてクランプ回路13を構成すると共に、NPN型バイポーラトランジスタ21のエミッタと電源端子11とを電気的に接続し、NPN型バイポーラトランジスタ21のコレクタを接地し、NPN型バイポーラトランジスタ21のベースとNPN型バイポーラトランジスタ21のコレクタとを電気的に接続した。

(もっと読む)

温度検出システム

【課題】本発明は、パワー半導体デバイスの温度測定を精度良く行う温度検出システムを提供する事を目的とする。

【解決手段】パワー半導体デバイスと、該パワー半導体デバイスの温度を検出するチップ温度検出素子と、該パワー半導体デバイスのロスを決める特性であるロス関連特性値を取得するロス関連特性値取得手段と、該ロス関連特性値から該パワー半導体デバイスの温度と該チップ温度検出素子の検出した温度との差分値を演算する差分値演算手段と、該チップ温度検出素子の検出した温度と該差分値とを足し合わせ補正後温度信号を生成する補正後温度信号生成部と、該補正後温度信号を外部へ出力する出力部とを備える。

(もっと読む)

半導体装置

【課題】応答性に優れ、瞬間的な動作や過大入力がある場合においてもダイオード素子の順方向動作時の損失増加や過剰電流による絶縁ゲートトランジスタ素子の破壊を防止できる小型の半導体装置を提供する。

【解決手段】絶縁ゲートトランジスタ素子21とダイオード素子22とが同じ半導体基板に形成され、絶縁ゲートトランジスタ素子21とダイオード素子22が逆並列に接続されてなる半導体装置60であって、ダイオード素子22に電流が流れた場合に、絶縁ゲートトランジスタ素子21のゲート(G)端子の電位を下げて、該絶縁ゲートトランジスタ素子21のゲートをオフする第1制御トランジスタ素子ST1が、前記半導体基板に形成されてなる半導体装置60とする。

(もっと読む)

静電気保護回路及びそれを備えた半導体装置

【課題】新たな素子を追加することなく、基本的な構成のSCR素子のみで、高いSCRトリガー電流をもつSCR素子を備えた静電気保護回路を提供する。

【解決手段】PNPバイポーラトランジスタ7のエミッタとベースがアノード端子5に、コレクタがNPNバイポーラトランジスタ8のベースに接続されている。NPNバイポーラトランジス8タのエミッタがカソード端子6に、ベースが第1抵抗R1を介してカソード端子6に、コレクタが第2抵抗R2を介してPNPバイポーラトランジスタ7のベースに接続されている。

(もっと読む)

半導体集積回路

【課題】電源線又は接地線に印加されるサージ電圧による静電破壊を防止し、また、デジタル回路とアナログ回路の間のノイズ干渉を防止した半導体集積回路を提供する。

【解決手段】第1の島領域105に第1の静電破壊保護ダイオードD1と第1の静電破壊保護バイポーラトランジスタT1を設けることで、第1の接地線102にサージ電圧が印加されたときに、第1の静電破壊保護ダイオードD1と第1の静電破壊保護バイポーラトランジスタT1がオンして、デジタル回路100を静電破壊から保護する。また、第1の分離層SP1は、デジタル回路100より第1の接地パッド101に近接した位置P1で第1の接地線102にコンタクトされ、第2の分離層SP2は、アナログ回路200より第2の接地パッド201に近接した位置P2で第2の接地線202にコンタクトされる。これにより、デジタル回路100とアナログ回路200とのノイズ干渉が防止される。

(もっと読む)

電流供給回路

【課題】通常とは逆方向に負荷回路側から電流が流れ込んだ場合でも回路内のトランジスタを保護し得る電流供給回路を提供する。

【解決手段】

このように本実施形態に係るドライバ回路20では、一点鎖線内のように、保護回路として、一対のトランジスタ21P,22Pで構成されたカレントミラー回路の出力側(トランジスタ22P側)にトランジスタ23Pを直列に介在させるとともに、このトランジスタ23Pのベースと入力側(トランジスタ21P側)との間でベース電流が流れる方向に順方向を向けたダイオード25を介在させ、また順方向電圧VFがトランジスタ23Pのベース−エミッタ間電圧VBE以上に設定されたツェナーダイオード24や、ダイオード25の順方向電圧VF以上にその順方向降下電圧が設定されたツェナーダイオード26を、カレントミラー回路の入力側に介在させる。

(もっと読む)

高速トリガーESD保護デバイスおよびその設計方法

【課題】ICに現れるオーバーシュートが低減可能なESD保護デバイス、およびその設計方法の提供。

【解決手段】主ESDデバイス10と、低減された電圧で、ESD電流を流すために、主ESDデバイスのトリガーノードに接続されたトリガーデバイス20とを含むESD保護回路の設計方法。このトリガーデバイス20は、ESD電流のための最初の電流経路中に配置される。この最初の電流経路中に、オフ状態からオン状態にトリガーされる少なくとも1つのトリガー要素を有する。この要素のトリガー速度が考慮され、その設計はそのトリガー速度が増加するように最適化される。更に、少なくとも1つのトリガー要素が、速いトリガー速度を得るために、所定のタイプ、好適にはゲート型ダイオードタイプから選択されESD保護回路。

(もっと読む)

ダイオード温度センサ素子とこれを用いた温度測定装置

【課題】広範囲の温度領域で高精度であり、極めて小さく形成できる高速応答可能な二端子のダイオード温度センサ素子を提供すると共に、これを用いた安価で高速応答可能な温度計測装置を提供する。

【解決手段】バイポーラトランジスタの2個のpn接合のうち、一方のpn接合を短絡してダイオードとして取り扱い、このダイオードをダイオード温度センサとして用い、バイポーラトランジスタを形成している半導体チップ内で、一方のpn接合を短絡してあり、外部には、二端子として取り出すようにしたダイオード温度センサ素子と、これを用いた温度計測装置を提供する。

(もっと読む)

61 - 80 / 184

[ Back to top ]