Fターム[5J055GX02]の内容

Fターム[5J055GX02]に分類される特許

101 - 120 / 1,507

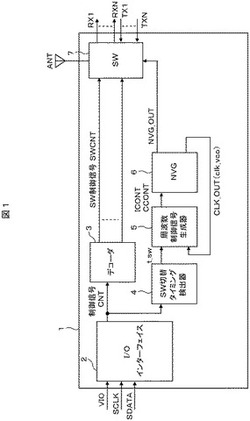

高周波スイッチモジュール

【課題】スイッチポート切替時間が短く、かつ低消費電力、低面積を同時に満たす高周波スイッチモジュールを提供する。

【解決手段】デコーダ3は、前記スイッチポートを切替える制御信号CNTに応答し、スイッチ7を制御するためのスイッチ制御信号SWCNTを生成して、スイッチ切替タイミング検出器は、スイッチ制御信号SWCNTに応答し、スイッチ切替え検出信号t_swを生成し、周波数制御信号生成器は、スイッチ切替え検出信号t_swに応答し、周波数制御信号ICONT、CCONTを生成し、負電圧発生回路は、周波数制御信号ICONT、CCONTに応答し、前記負電圧発生回路内で生成したクロック信号の周波数を2つ以上のそれぞれ異なる周波数に切替つつ、負電圧出力信号NVG_OUTを生成し、スイッチ7は、スイッチ制御信号SWCNTと前記負電圧出力信号NVG_OUTに応答し、複数の高周波信号ポート間の経路を切替える。

(もっと読む)

半導体装置

【課題】本発明は、第1状態と第2状態との二つの状態のうち、第1状態に初期化し、初期化した第1状態に対応する電位の信号を生成することが可能な半導体装置を提供する。

【解決手段】本発明は、“0”(第1状態)と“1”(第2状態)との二つの状態のうち、“0”に初期化し、初期化した“0”に対応する電位の信号Aを生成することが可能な半導体装置10である。半導体装置10は、並列に複数接続され、“0”と“1”との二つの状態を保持することが可能なフリップフロップ回路2と、複数のフリップフロップ回路2と接続し、複数のフリップフロップ回路2のうち、少なくとも一つのフリップフロップ回路2で保持する状態が“0”の場合、“0”に対応する電位の信号を生成し、出力するAND回路3とを備える。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】入力端子IN1から印加される電圧に応じてオンオフするトランジスタT3を介して、入力電圧Vin2がトランジスタT2のゲートに入力される。そのため、入力電圧Vin1,Vin2がともにハイとなったときだけ、トランジスタT1,T2の双方のゲートにオン電圧が印加される。

(もっと読む)

スイッチ制御回路、及び印刷装置

【課題】スイッチがオフ状態(非導通状態)である場合の消費電力を低減する。

【解決手段】スイッチ制御回路は、制御端子に印加される電圧に基づいて、第1の電源線VDDから供給される電力を出力状態と非出力状態との間で切り替えるP−FET11と、第1の電源線VDDと制御端子との間に接続される抵抗R1と、制御端子と第2の電源線との間に、第1のコンデンサーC1と第2のコンデンサーC2が直列に接続されているコンデンサー分圧回路13と、第1のコンデンサーC1と並列に接続され、自素子の両端間の電位差が、予め定められた閾値以上である場合に導通状態になり、電位差が閾値未満である場合に非導通状態になる制御素子(ZD)と、第2のコンデンサーC2と並列に接続され、自スイッチの両端間を導通状態と非導通状態との間で切り替えるスイッチSWと、を備える。

(もっと読む)

スイッチおよびそのスイッチを用いたスイッチ回路

【課題】スイッチ用のトランジスタに発生する寄生ダイオードを介して内部に流入するESDによる負電流から内部回路を保護する。

【解決手段】第4nチャネルMOSFET(Mn4)は、ソース端子とバーグゲート端子間が接続されている。スイッチ素子は、第4nチャネルMOSFET(Mn4)のソース端子とグラウンド電位との間に接続され、第4nチャネルMOSFET(Mn4)のオフ時に第4nチャネルMOSFET(Mn4)のソース端子をグラウンド電位にする。保護回路40は、第4nチャネルMOSFET(Mn4)のソース端子と上記スイッチ素子の入力端子の接続点と、グラウンド電位との間に設けられ、静電気放電による第4nチャネルMOSFET(Mn4)のドレイン端子から流入する負電流をグラウンド電位に流す。

(もっと読む)

選択可能閾値リセット回路

【課題】低電圧試験のためのリセット回路及び方法を提供する。

【解決手段】低電圧試験回路125と、システム100および200と、集積回路パッケージ104および204における回路127の低電圧試験を実行する方法が、電源電圧の一部分である電圧を生成する電圧分割ラダー320、一部分を基準電圧と比較する比較器310、電圧分割ラダーのトポロジーを制御し、それによって一部分の値を変更するスイッチ350を含む、選択可能閾値リセット回路125を含み、スイッチは製品試験装置102および202からの信号によって制御され、信号は、選択可能閾値リセット回路のリセット閾値を標準リセット閾値未満に低減されるようにして、標準リセット閾値未満の電源電圧で回路を試験することを可能にする。

(もっと読む)

入出力回路

【課題】回路規模の増大を抑制しながら、コネクタに接続されたチャージャーの種類を的確に認識する。

【解決手段】電源検出回路12は、VBUS端子への外部からの給電を検出する。チャージャー検出回路14は、DP端子およびDM端子の電圧を検出することにより、チャージャーの種類を特定する。チャージャー検出回路14は、DP端子およびDM端子の少なくとも一方のオープン、プルアップ、プルダウンまたは両端子間のショートを検出する。

(もっと読む)

負荷駆動装置

【課題】短絡保護のためのクランプ電圧の設定に基づいて、損失を抑制することが可能な負荷駆動装置を提供する。

【解決手段】IGBT1の温度、出力電流、ミラー電流もしくはゲート閾値電圧Vthを検出し、これらのいずれかに基づいてミラー電圧Vmirrorのバラツキに応じたクランプ電圧を演算する。これにより、クランプ電圧をその状況下でのミラー電圧Vmirrorに対応する値に低く抑えることが可能となり、クランプ電圧をミラー電圧Vmirrorのバラツキの最大値、つまりすべての環境変化等を含めた最大値を考慮して設計する場合と比較して、クランプ電圧を小さく抑えられる。したがって、クランプ時にIGBT1を損失が大きくなることを抑制しつつ、短絡耐量を向上することが可能となる。

(もっと読む)

スイッチング回路

【課題】スイッチング回路のデッドタイム制御における電力効率を向上させる。

【解決手段】スイッチング制御部2は、パルス信号Aがロウレベルの時に、Pチャンネル電界効果トランジスタM3のドレイン電位G1が立ち上がったのを検出してから、Nチャンネル電界効果トランジスタM4のドレイン電位G2が立ち上がるように、スイッチング部Wを制御し、パルス信号Aがハイレベルの時に、Nチャンネル電界効果トランジスタM4のドレイン電位G2が立ち下がったのを検出してから、Pチャンネル電界効果トランジスタM3のドレイン電位G1が立ち下がるように、スイッチング部Wを制御する。

(もっと読む)

電圧変換回路及び不揮発性半導体記憶装置

【課題】チャージポンプ回路を駆動するクロックバッファ回路に流れる瞬時電流を抑制すること。

【解決手段】

第1のトランジスタ(T11)のドレインを第1のキャパシタ(C11)によって第1の制御信号(DCLK10)に応じて昇圧駆動する第1のバッファと、第1のトランジスタ(T11)のゲートを第2のキャパシタ(C12)によって第2の制御信号(GCLK10)に応じて昇圧駆動する第2のバッファとから構成される電圧変換回路おいて、

第1のバッファは,第1の制御信号(DCLK10)の遷移時の駆動能力が,第2の制御信号(GCLK10)の遷移時の駆動能力よりも低いことを特徴とする電圧変換回路。

(もっと読む)

パワー半導体スイッチの制御回路及びその制御方法

【課題】寄生容量の影響を最少化させることのできる、パワー半導体スイッチの改良された制御方法及び制御装置を提供する。

【解決手段】パワー半導体スイッチの制御接続端信号を生成するための信号処理ユニットを備えた、パワー半導体スイッチを制御する制御回路において、少なくとも一つの半導体素子が、定められたパワー半導体スイッチのコレクタ・エミッタ電圧を越えた時に、導通作動され、半導体素子の出力端が導電性の接続線を通じて抵抗直列回路の抵抗の間の接続点と、或いは信号処理ユニットと接続されている抵抗直列回路の出力端と接続されており、半導体素子のブレークダウン電圧が、半導体素子の出力端の電位が、パワー半導体スイッチがスイッチオン状態にある時のパワー半導体スイッチの制御接続端の電位よりも高くなるように選ばれている。

(もっと読む)

パワーオンリセット回路

【課題】パワーオン時における回路電源電圧の変化の緩急に拘らず、非動作電圧から動作電圧へ変化時にリセット信号を確実に出力するパワーオンリセット回路を提供する。

【解決手段】本発明に係るパワーオンリセット回路は、回路電源電圧を受けて充電を行う充電回路と、回路電源電圧を受けて出力電圧を出力する動作電圧設定回路と、前記充電回路の出力する充電電圧、及び、前記動作電圧設定回路の出力する出力電圧を判定して、パワーオンリセット信号を出力する電圧判定回路とを備える。

(もっと読む)

出力回路および出力制御システム

【課題】回路面積の縮小を図りつつ、待機電流をカットオフすることが可能な出力回路を提供する。

【解決手段】出力回路は、第1の電源にソースが接続された出力pMOSトランジスタを備える。出力回路は、第1の出力pMOSトランジスタのドレインと接地との間に接続された出力nMOSトランジスタを備える。出力回路は、出力pMOSトランジスタのドレインと前記出力nMOSトランジスタのドレインとの間に接続された出力端子を備える。出力回路は、前記出力pMOSトランジスタのオン/オフを制御するための第1のゲート制御信号を第1のゲート制御端子から出力する第1のレベルシフタ回路を備える。出力回路は、前記出力nMOSトランジスタのオン/オフを制御するための第2のゲート制御信号を第2のゲート制御端子から出力する第2のレベルシフタ回路と、を備える。

(もっと読む)

レベル変換バススイッチ

【課題】レベル変換時の信号の立ち上がりを速くすることのできるレベル変換バススイッチを提供する。

【解決手段】実施形態のレベル変換バススイッチは、低電圧レベル信号が伝送される低電圧レベル信号線と高電圧レベル信号が伝送される高電圧レベル信号線との間に、低電圧レベルの制御信号により導通が制御されるMOSトランジスタ型のスイッチ1が接続され、高電圧レベル信号線と高電圧電源線VccBとの間に、プルアップ抵抗2が接続される。このレベル変換バススイッチでは、加速回路3が、高電圧レベル信号の立ち上がりをプルアップ抵抗2による立ち上がりよりも速くし、加速期間制御回路4が、加速回路3の作動期間を制御する。

(もっと読む)

出力バッファー回路

【課題】出力バッファーの面積・体積・部品点数の増加を抑制するとともに、ドライブ能力を向上させることが可能な出力バッファー回路を提供する。

【解決手段】第一駆動信号LINを伝達する第一入力経路4a、第二駆動信号RINを伝達する第二入力経路4b、第一入力経路4aと対応する第一出力バッファー6a及び第二入力経路4bと対応する第二出力バッファー6bを備える出力バッファー回路1において、入力経路切り替え手段8が、ステレオモード及びモノラルモードのうち、モノラルモードでは、第一入力経路4aと第一出力バッファー6a及び第二出力バッファー6bとを電気的に接続させ、出力経路切り替え手段10が、第一出力バッファー6a及び第二出力バッファー6bと、第一入力経路4a及び第一出力バッファー6aと対応する第一負荷2aとを、電気的に接続させる。

(もっと読む)

高周波スイッチモジュール

【課題】マルチバンドパワーアンプへ接続される小型の高周波スイッチモジュールを構成する。

【解決手段】高周波スイッチモジュール10は、アンテナANTに共通端子PIC0が接続する第1スイッチ素子11と、マルチバンドパワーアンプ40に共通入力端子PICt0が接続する第2スイッチ素子30を備える。第2スイッチ素子30の個別出力端子PICt2は、第1のローパスフィルタ12を介して第1スイッチ素子11の個別端子PIC11に接続し、第2のローパスフィルタ13とハイパスフィルタ102の直列回路を介して第1スイッチ素子11の個別端子PIC12に接続する。第2スイッチ素子30の個別出力端子PICt1は位相回路101とSAWデュプレクサ14を介して第1スイッチ素子11の個別端子PIC13に接続し、位相回路101とSAWデュプレクサ15を介して第1スイッチ素子11の個別端子PIC14に接続する。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタ

ル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配

線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続さ

れ、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、

前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トラ

ンジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジス

タのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする

。

(もっと読む)

半導体スイッチ及び無線機器

【課題】端子切替時の歪みの増加を抑制した半導体スイッチ及び無線機器を提供する。

【解決手段】実施形態によれば、電源回路と、駆動回路と、スイッチ部と、補正回路と、を備えた半導体スイッチが供給される。前記電源回路は、電源電位と異なる第1の電位を生成する。前記駆動回路は、前記第1の電位と異なる第2の電位と前記第1の電位とが供給され、端子切替信号に基づいて前記第1の電位及び前記第2の電位の少なくとも一方を出力する。前記スイッチ部は、前記駆動回路の出力に応じて共通端子と高周波端子との接続を切り替える。前記補正回路は、前記端子切替信号の変化を検出し、前記第1の電位の極性と等しい極性の電荷を前記駆動回路に供給して前記第1の電位を補正する。

(もっと読む)

リセット回路および半導体装置

【課題】 クロックゲーティング状態にあるときにも、初期化対象の論理回路の初期値を後段の論理回路に出力する。

【解決手段】 クロックに同期して動作する論理回路をリセットするリセット回路は、論理回路の出力信号を受け、論理回路がリセットされたときの出力信号の初期値と論理回路から受けた出力信号とのいずれかを出力する出力選択部と、論理回路をリセットするためのリセット信号を受け、出力選択部から初期値がリセット信号に応答して出力されるように出力選択部を制御する制御部とを有している。

(もっと読む)

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

101 - 120 / 1,507

[ Back to top ]