Fターム[5J055GX02]の内容

Fターム[5J055GX02]に分類される特許

61 - 80 / 1,507

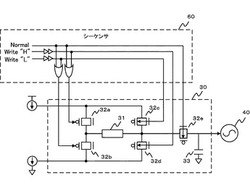

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

低Vf逆導通FET回路及び多機能FET回路用IC

【課題】内部ダイオード又は外部ダイオードを使用せずに、逆方向へ導通可能なMOS−FET回路を提供すること。

【解決手段】MOS−FET(10)と、このMOS−FET(10)のドレインをマイナス入力に接続し、ソースをプラス入力に接続したオペアンプ(15)と、このオペアンプ(15)の出力を一方の入力とし、ゲート端子(14)を他方の入力とした第一OR回路(17)とからなり、前記第一OR回路(17)の出力を前記MOS−FET(10)のゲートに接続した。

(もっと読む)

スイッチモジュールおよびそれを用いた試験装置

【課題】半導体スイッチの低周波数領域での歪み特性を改善する。

【解決手段】制御ポートP3には、制御電圧VCが入力される。伝送路10は、入力ポートP1と出力ポートP2の間を接続する。シャントスイッチ20は、伝送路10と接地端子の間に設けられる。シャントスイッチ20は、そのドレイン、ソースの一方が伝送路10と接続され、そのドレイン、ソースの他方が接地端子に接続されるFET22を備える。第1抵抗R1は、FET22のゲートと制御ポートP3の間に設けられる。第2抵抗R2は、FET22のゲートと伝送路10の間に設けられる。

(もっと読む)

電流制御用半導体素子およびそれを用いた制御装置

【課題】ゲインa、およびオフセットbの変動を動的に補正することで、1チップのIC内で高精度な電流検出が可能な電流制御用半導体素子、およびそれを用いた制御装置を提供することにある。

【解決手段】

同一半導体チップ上に、トランジスタ4と、電流−電圧変換回路22とADコンバータ23とを有する。参照電流生成回路6,6’は、負荷2の電流に電流パルスIcを重畳して、ADコンバータが出力する電圧デジタル値を変動させる。ゲインオフセット補正部8は、参照電流生成回路6,6’による電圧デジタル値の変動を信号処理して、ADコンバータ23が出力する電圧デジタル値と負荷の電流デジタル値の線形関係式におけるゲインa,a’及びオフセットb,b’を動的に取得する。電流デジタル値演算部12は、ゲインオフセット補正部8により取得されたゲイン及びオフセットを用いて、ADコンバータが出力する電圧値を補正する。

(もっと読む)

RFアンテナスイッチ回路、高周波アンテナ部品及び移動通信機器

【課題】スイッチング素子の個数を減らし、スイッチング素子を送受信時共有して、RFアンテナスイッチのサイズを減らすと共に、小型化及びワンチップ化にさらに応じるRFアンテナスイッチ回路、高周波アンテナ部品及び移動通信機器を提供する。

【解決手段】アンテナ1と、少なくとも一つの送信段2及び少なくとも一つの受信段3を備える複数の入出力段と、少なくとも一つの送信段2とアンテナ1側の共通ノード4、5との間の送信経路上に配置され、制御信号によって信号を伝達する少なくとも一つの送信スイッチブロック10と、受信段3と共通ノード4、5との間の受信経路上に配置され、制御信号によって伝達する少なくとも一つの受信スイッチブロック30、30a、30bと、スイッチング素子を共有して各々の送信及び受信動作と同期してオン動作する共用送受信スイッチブロック50とを含む。

(もっと読む)

スイッチング素子の制御装置

【課題】実際に発生しているフライバックエネルギーを定量的に評価した上で保護動作を行うことができるスイッチング素子の制御装置を提供する。

【解決手段】NチャネルMOSFET2を介してコイル1に供給される電流をセンスMOSFET6及び検出用抵抗素子21により検出し、NチャネルMOSFET2をターンオフさせた際に発生し、ドレインに印加される逆起電圧をクランプ回路3によってクランプする。電流検出回路24は、クランプ回路3に発生するクランプ電圧によりNチャネルMOSFETがターンオンした際に、検出用抵抗素子21に流れる電流を複数の閾値と比較し、保護動作部26は、電流検出回路24の比較結果により、前記電流がNチャネルMOSFET2をターンオフさせた時点からの時間経過に対応する特定の閾値を超えていると判定されると、逆起電圧に基づくエネルギーを減少させるようにNチャネルMOSFET2の制御状態を変更する。

(もっと読む)

電流駆動型半導体スイッチの駆動回路

【課題】従来の電流駆動型半導体スイッチ8の駆動回路は、駆動回路における電力損失を抑制するためにスイッチやスイッチを制御するための手段が必要となり部品点数が増える。

【解決手段】電源1と電流駆動型半導体スイッチ8のベース又はゲート端子の間に接続される負の温度特性を有する第1の可変抵抗10と、前記電流駆動型半導体スイッチ8のコレクタ又はドレイン電流による動作損失により過熱される熱伝導部11を備え、前記第1の可変抵抗10を前記熱伝導部11により熱が供給されるように配置する。

本発明により、簡単な構成で部品点数を増やすことなく駆動回路における電力損失を抑制することができる。

(もっと読む)

アナログスイッチ回路およびマルチプレクサ回路

【課題】 外部端子の雑音の影響を抑制しつつ、リーク電流を低減する。

【解決手段】 アナログスイッチ回路は、第1ノードと第2ノードとの間に配置された第1スイッチと、第2ノードと第3ノードとの間に配置された第2スイッチと、所定の電圧が供給される第4ノードと第2ノードとの間に配置された第3スイッチと、少なくとも2種類の制御信号を受け、第1スイッチおよび第2スイッチをオンし、かつ、第3スイッチをオフする第1制御と、第1スイッチ、第2スイッチおよび第3スイッチをオフする第2制御と、第1スイッチおよび第2スイッチをオフし、かつ、第3スイッチをオンする第3制御とのいずれかを、制御信号の組み合わせに基づいて実施する制御部とを有している。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

スイッチング素子の保護回路

【課題】窒化物FETを高速スイッチング動作させることができ、且つ、サージ電圧から窒化物FETを保護することができるスイッチング素子の保護回路。

【解決手段】直列に接続された高圧側素子M1及び低圧側素子M2と、高圧側素子をオンオフさせる信号を出力するハイサイドプリドライバ11と、高圧側素子と逆のオンオフ状態になるように低圧素子をオンオフさせる信号を出力するローサイドプリドライバ12と、高圧側素子と低圧側素子の接続点に制御端子が接続されたスイッチング素子Tr1と、スイッチング素子の一方の端子にカソードが接続されたダイオードD1と、ダイオードのアノードに入力端子が接続され、ダイオードのブレーク時にスイッチング素子の制御端子に電流を供給するとともに、低圧側素子のオフを指示する信号をローサイドプリドライバに供給する制御器21とを備える。

(もっと読む)

電源回路

【課題】カレントミラー回路によって、複数の回路を電流駆動させる場合に、各回路の動作に対するばらつきを低減することができる電源回路を提供する。

【解決手段】FET1、2、3と、スイッチング素子であるスイッチ6〜9とで電源回路を構成している。FET1、2、3でカレントミラー回路を構成している。スイッチ6、7、8、9によって選択回路50が構成される。選択回路50は、スイッチ6〜9の切り替えにより、ミラー電流Ib2をオペアンプ4又はオペアンプ5のいずれかに供給し、さらに、ミラー電流Ib1をオペアンプ4又はオペアンプ5のいずれかに供給する。すなわち、ミラー電流Ib1とミラー電流Ib2とを入れ替えて交互に、オペアンプ4、5にそれぞれ供給する。

(もっと読む)

制御信号発生回路およびそれを用いた半導体装置

【課題】半導体装置の制御に好適な制御信号発生回路を提供する。

【解決手段】ジョンソンカウンタ31は、フリップフロップFF1〜FF4およびゲート回路41〜44を含み、順次入力されるスタート信号ST1〜ST4に応答してそれぞれ制御信号C1〜C4を「H」レベルにした後、順次入力されるストップ信号SP1〜SP4に応答してそれぞれ制御信号C1〜C4を「L」レベルにする。したがって、多数のフリップフロップを用いることなく、所望の時間間隔で制御信号C1〜C4を順次「H」レベルにし、順次「L」レベルにすることができる。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

駆動装置

【課題】電圧駆動型素子を駆動状態と非駆動状態の間で遷移させるときの遷移期間において、電圧駆動型素子のゲート電圧を柔軟に制御するための技術を提供する。

【解決手段】駆動装置1は、電圧駆動部3と電流駆動部4を備えている。電圧駆動型素子2を駆動状態と非駆動状態の間で遷移させるときの遷移期間のうちの一部の区間では、電圧駆動部3を利用した電圧駆動型素子2のゲート電圧Vgの制御が停止され、電流駆動部4を利用した電圧駆動型素子2のゲート電圧Vgの制御が実行されるように構成されている。

(もっと読む)

電力変換装置

【課題】本発明の課題は、電力変換装置における温度検出素子の時間変化率を検出し、温度上昇の事前予測によりフェールセーフをかけることで、発熱半導体素子の発熱抑制とモジュールケースの冷却構造最適化を実現することである。

【解決手段】上記課題を解決するために、前記半導体素子のモジュールケースまたは素子自体の温度の時間変化率を検出する検出手段と、素子のゲート抵抗値を可変にする抵抗可変回路とを設け、前記検出温度の時間変化率が所定の設定値以上になったと判断されたときは、ゲート抵抗値を前記抵抗可変回路により低減することを特徴とする電力変換装置を提供する。

(もっと読む)

自動補正機能付き周期タイマ

【課題】 衛星搭載コンポーネントのうち、衛星内部に配信される基準タイミングに同期して周期動作を行うようなコンポーネントでは、オシレータが有するクロック精度誤差のため、周期タイミングにずれが生じることがあり、これを回避する自動補正機能付き周期タイマを得る。

【解決手段】 基準タイミングの間隔を内部クロックによりカウントし、カウント値に従ってコンポーネントの周期タイミングを生成する。ユーザは予め周期タイミングの設定を「基準タイミングに対する分割数」として2の冪乗の値で与えて与えておき、基準タイミングの間隔のカウント値を分割数に従いビットシフトすることで周期タイマのカウント値を算出し、周期タイミングを生成する。

(もっと読む)

半導体装置

【課題】ハーフブリッジ回路のメインスイッチング素子が同時オンになることを確実に防止する。

【解決手段】ローサイド側の入力信号を遅延させてローサイド側遅延信号として出力する遅延回路20と、ハイサイド側の入力信号からハイサイド側セット出力信号と予備リセット信号とを生成して出力するパルス発生回路12と、ローサイド側の入力信号がアクティブになってからローサイド側遅延信号がアクティブになるまでの期間、又は予備リセット信号がアクティブである期間にハイサイド側リセット出力信号をアクティブにするリセット信号生成回路30と、を備えるハーフブリッジドライバとする。

(もっと読む)

CMOSインバータを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路

【課題】CMOSインバータのP形MOSトランジスタのボディバイアスを変化させても、入力信号の立ち上がりと立ち下がりの伝搬遅延時間の差を、従来のものより小さく保てるマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路を提供する。

【解決手段】パスゲートM1、M2の出力に初段出力バッファとして低しきい値CMOSインバータINV1を接続したセレクター回路を基本構成とし、それを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路であって、パスゲートはそのボディ端子が可変電位をとるボディバイアス電源VBNに接続し、INV1のP形MOSトランジスタM3のしきい値電圧を可変にできるようにそのボディ端子は可変電位をとるボディバイアス電源VBPに接続し、そのN形MOSトランジスタM4はそのしきい値電圧を固定するためにそのボディ端子が固定電位をとる電源VSSに接続する。

(もっと読む)

光源駆動装置、光源装置、プロジェクタ、及び制御方法

【課題】製造コストを抑制しつつ、カラー発光及び白色発光の双方を行うことのできる光源駆動装置を実現する。

【解決手段】駆動装置10は、LED100、200、及び300に対して電流を供給可能な電流供給部15と、LED100及び200にそれぞれ接続された抵抗13及び抵抗14と、電流供給部15を、上記複数のLEDの何れか1つに対して、抵抗13及び抵抗14を介することなく選択的に接続または遮断するスイッチ部11と、電流供給部15を、上記抵抗が接続された各LEDに対して、上記抵抗を介して接続または遮断するスイッチ部12と、を備えており、第1の発光モードにおいて、上記複数のLEDの何れか1つをスイッチ部11により電流供給部15に接続し、第2の発光モードにおいて、スイッチ部12を接続状態に設定すると共に、上記抵抗が接続されていないLEDをスイッチ部11により電流供給部15に接続する。

(もっと読む)

半導体装置

【課題】貫通電流を少なくできる半導体装置を提供する。

【解決手段】データを出力する出力部を各々備えた複数の半導体チップと、出力部の各々と接続された配線と、配線を介して複数の半導体チップの各々からデータを受け付ける受付部と、を含み、出力部が順番に駆動する半導体装置にて、出力部の各々は、オン状態時の抵抗値を変更可能であり、自己の駆動開始時から自己の次に駆動を開始する出力部の駆動開始時の前のタイミングまでの第1期間の間は、オン状態時の抵抗値を第1抵抗値にしてデータを配線に出力し、第1期間が経過した時点から自己の駆動終了時までの第2期間の間は、オン状態時の抵抗値を第1抵抗値よりも大きい第2抵抗値にしてデータを配線に出力する。

(もっと読む)

61 - 80 / 1,507

[ Back to top ]