Fターム[5F003BE90]の内容

バイポーラトランジスタ (11,930) | エミッタ (1,226) | 形状、段付エミッタ、エミッタメサ (391)

Fターム[5F003BE90]に分類される特許

61 - 80 / 391

半導体基板

【課題】AlGaAs/InGaP界面の遷移層の形成を抑制する。

【解決手段】ヒ素化合物からなる第1半導体と、ヒ素化合物からなる第2半導体と、リン化合物からなる第3半導体とを含み、前記第2半導体と前記第3半導体とが接触しており、前記第1半導体と前記第3半導体との間に前記第2半導体が位置しており、前記第1半導体が第1原子を第1濃度で含有し、前記第2半導体が第1原子を第2濃度で含有し、前記第1原子が第1伝導型のキャリアを発生させ、前記第1濃度が、前記第1半導体にドープする前記第1原子の量を増加するに従い増加するキャリア数が飽和し始める前記第1原子の濃度以上の濃度であり、前記第2濃度が、前記第2半導体にドープする前記第1原子の量を増加するに従い増加するキャリア数が飽和し始める前記第1原子の濃度未満の濃度である半導体基板を提供する。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製法

【課題】高い電流増幅率を有し、高周波特性および素子寿命に優れたヘテロ接合バイポーラトランジスタおよびその製法を提供すること。

【解決手段】半絶縁性基板1上に、n型半導体より成る真性エミッタ層16と、p型ドーパントを高濃度でドーピングされ、真性エミッタ層16よりも狭いバンドギャップを有する半導体より成るベース層9と、ベース層9と同じ半導体より成るコレクタ層10とを、この順序で積層して成るへテロ接合バイポーラトランジスタにおいて、真性エミッタ層16の周囲に、高抵抗領域15が設けられ、高抵抗領域15と真性エミッタ層16との間に、真性エミッタ層16の半導体と同じ半導体から成るガードリング領域17が設けられ、真性エミッタ層16とベース層9との接合面が、ガードリング領域17の上面よりも下に位置することを特徴とするヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

ヘテロ接合バイポーラ・トランジスタ及びその製造方法

【課題】 ヘテロ接合バイポーラ・トランジスタ及びその製造方法を提供する。

【解決手段】 ヘテロ接合バイポーラ・トランジスタに関連する、半導体構造体及び半導体の製造方法が提供される。この方法は、同じ配線レベルにある金属導線によって接続される2つのデバイスを形成することを含む。2つのデバイスの第1のものの金属導線は、銅配線構造体上に金属キャップ層を選択的に形成することによって形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

高利得ワイドバンドギャップ・ダーリントン・トランジスタ及び関連する製造方法

パッケージ化電力電子デバイスが、ベース、コレクタ、及びエミッタ端子を有するワイドバンドギャップ・バイポーラ・ドライバ・トランジスタ(112)と、ベース、コレクタ、及びエミッタ端子を有するワイドバンドギャップ・バイポーラ出力トランジスタ(116)とを含む。出力トランジスタのコレクタ端子は、ドライバ・トランジスタのコレクタ端子に結合され、出力トランジスタのベース端子は、ドライバ・トランジスタのエミッタ端子に結合され、ダーリントン対をもたらす。平面図における出力トランジスタの面積は、ドライバ・トランジスタの面積より少なくとも3倍大きい。例えば、出力トランジスタのドライバ・トランジスタに対する面積比は、約3:1から約5:1までの間とすることができる。関連するデバイス及び製造方法についても説明される。 (もっと読む)

バイポーラ・トランジスタ及びその製造方法

【課題】 バイポーラ・トランジスタ構造体、バイポーラ・トランジスタを設計し製造する方法、及びバイポーラ・トランジスタを有する回路を設計する方法を提供する。

【解決手段】 バイポーラ・トランジスタを設計する方法は、バイポーラ・トランジスタの初期設計を選択するステップ(図25の240)と、バイポーラ・トランジスタの初期設計をスケーリングしてバイポーラ・トランジスタの縮小設計を生成するステップ(245)と、バイポーラ・トランジスタの縮小設計の応力補償が必要かどうかを、スケーリング後のバイポーラ・トランジスタのエミッタの寸法に基づいて判断するステップ(250)と、バイポーラ・トランジスタの縮小設計の応力補償が必要な場合に、縮小設計のトレンチ分離レイアウト・レベルのレイアウトを、縮小設計のエミッタ・レイアウト・レベルのレイアウトに対して調節して(255)バイポーラ・トランジスタの応力補償縮小設計を生成するステップ(260)と、を含む。

(もっと読む)

化合物半導体ウェーハの製造方法及び化合物半導体素子

【課題】電流利得がサブコレクタ層のキャリア濃度により大きく依存しないようにしたHBT用化合物半導体ウェーハの製造方法及びこれを利用した半導体素子を提供すること。

【解決手段】GaAs基板2上にサブコレクタ層41、コレクタ層42、ベース層43、及びエミッタ層44をMOCVD法を用いて気相成長させてHBT製造用の半導体ウェーハ1を製造する場合、サブコレクタ層41として、n型GaAs層をGaAs基板2上にV/III比を1.0を超え5以下の範囲として成長させるようにした。成長温度を620℃〜550℃の比較的低い温度で成長させるようにしてもよい。これによりサブコレクタ層41の結晶性を良好なものとし、サブコレクタ層41のキャリア濃度によって電流増幅率βが大きく変化するのを抑えることができる。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】高電流注入における高周波特性が改善されたダブルヘテロ接合バイポーラトランジスタを提供すること。

【解決手段】基板1上に、サブコレクタ層2、コレクタ層、ベース層4、エミッタ層5、キャップ層6が順次積層されたダブルヘテロ接合バイポーラトランジスタにおいて、前記コレクタ層が、第1の半導体層31と第2の半導体層32の積層構造から形成され、第1の半導体層31と第2の半導体層32がType−II型のヘテロ接合を形成し、第2の半導体層32とベース層4がホモ接合あるいはType−I型のヘテロ接合を形成することを特徴とするダブルヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】同一基板に形成されるHBTとFETとの相互影響を低減する。

【解決手段】第1半導体と、第1半導体の上方に形成された第2半導体とを備え、第2半導体は、P型の伝導型を示す不純物またはN型の伝導型を示す第1不純物原子と、第2半導体が第1不純物原子を有する場合のフェルミ準位を、第2半導体が第1不純物原子を有しない場合のフェルミ準位に近づける第2不純物原子とを有する半導体基板を提供する。一例として、当該第2半導体の多数キャリアは電子であり、第2不純物原子は、第1不純物原子を有する第2半導体のフェルミ準位を下降させる。第2半導体は3−5族化合物半導体であり、第2不純物原子が、ベリリウム、ボロン、炭素、マグネシウム、および亜鉛からなる群から選択された少なくとも1つであってもよい。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】エミッタ電子輸送特性やエミッタ注入効率を劣化させることなく、レッジ部を薄層化することが容易で、微細化に適したヘテロ接合バイポーラトランジスタを提供すること。

【解決手段】エミッタ層は、第1の半導体層11と、第2の半導体層12と、第3の半導体層13との積層構造からなり、第3の半導体層13は、第2の半導体層12に対してウェット・エッチングにより選択的に除去でき、第2の半導体層12は、第1の半導体層11に対してウェット・エッチングにより選択的に除去でき、第1の半導体層11と第3の半導体層13のバンドギャップはベース層4のバンドギャップよりも大きく、第2の半導体層12は不純物添加によって縮退しており、第3の半導体層13は不純物添加によって中性領域を形成しているヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

化合物半導体素子及びその製造方法

【課題】高速動作が可能でかつ、ESD耐性の高い化合物半導体素子及びその製造方法を提供すること。

【解決手段】本発明に係る化合物半導体素子は、電界効果トランジスタ又はヘテロ接合バイポーラトランジスタからなるトランジスタ部と、トランジスタ部と並列に接続されたESD保護部114と、を備え、ESD保護部114は、第1導電型の不純物を含有する第1及び第2の半導体層109、113と、第1及び第2の半導体層109、113の間に形成され、第1及び第2の半導体層109、113の禁制帯幅よりも禁制帯幅が広く、かつ、不純物濃度が1×1017cm−3以下である第3の半導体層111と、を備えるものである。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】バイポーラトランジスタにおいて、耐圧改善のためにコレクタ濃度を低くした際のトランジスタとしての性能低下を抑制する。

【解決手段】バイポーラトランジスタ100は、コレクタ層3上に、エピタキシャル成長されたヘテロ接合の真性ベース層50を有する。真性ベース層50は、分離層4に囲まれたコレクタ層3上に配置され、コレクタ層3の表面部に、N型不純物層30が形成されている。N型不純物層30の不純物濃度は、N型不純物層30の下方におけるコレクタ層3の不純物濃度よりも高い。N型不純物層30と真性ベース層50との間に、N型不純物層30及び真性ベース層50よりも不純物濃度が低いエピタキシャル成長層が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波帯域で動作する半導体装置の特性の低下を抑制しつつ、製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、電界効果型トランジスタと、ヘテロ接合バイポーラトランジスタと、ヘテロ接合バイポーラトランジスタのGaAsベース層7を用いて形成されたベースエピ抵抗素子28と、電界効果型トランジスタのInGaAsチャネル層4を用いて形成された配線部26と、配線部26とベースエピ抵抗素子28とを絶縁する高抵抗化領域27と、配線部26の水平方向の周囲を囲う絶縁性の素子分離領域24とを含む。また、ベースエピ抵抗素子28は、半絶縁性GaAs基板1の主面に垂直な方向から見て、配線部26と交差しているベースエピ抵抗素子領域29を有する。

(もっと読む)

トランジスタ素子

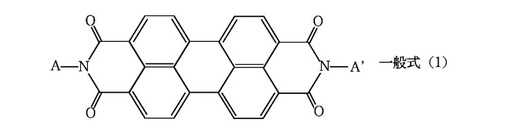

【課題】エミッタ電極−コレクタ電極間において、オフ電流が小さく、かつ、低電圧で大電流変調が可能であるオン/オフ比に優れたトランジスタ素子を提供すること。

【解決手段】エミッタ電極とコレクタ電極との間に、有機半導体層とシート状のベース電極とが設けられているトランジスタ素子において、該有機半導体層が、下記一般式(1)で表される化合物を含んでいるトランジスタ素子。 (もっと読む)

(もっと読む)

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】単一半導体基板上にHBTおよびFETのような異なる種類の複数デバイスを形成するに適した化合物半導体基板を提供する。

【解決手段】第1半導体110と、第1半導体上に形成された、電子捕獲中心または正孔捕獲中心を有するキャリアトラップ層130と、キャリアトラップ層上にエピタキシャル成長され、自由電子または自由正孔が移動するチャネルとして機能する第2半導体144と、第2半導体上にエピタキシャル成長したN型半導体/P型半導体/N型半導体で表される積層体、または前記第2半導体上にエピタキシャル成長したP型半導体/N型半導体/P型半導体で表される積層体を含む第3半導体160とを備える半導体基板。

(もっと読む)

集積装置

【課題】

形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な素子を用いた集積装置を提供すること。

【解決手段】

回路素子が長手方向に連続的又は間欠的に形成されている素子、回路を形成する複数の領域を有する断面が長手方向に連続的又は間欠的に形成されている素子を複数複数束ね、撚り合せ、織り込み又は編み込み、接合し、組み合わせて成形加工し又は不織状に成形したことを特徴とする。

(もっと読む)

有機縦型トランジスタ

【課題】キャリア移動度が高く、低駆動電圧で大電流変調を可能とする有機縦型トランジスタを提供すること。

【解決手段】有機縦型トランジスタ1は、基板7と、エミッタ電極2と、第1有機半導体層3と、ベース電極4と、第2有機半導体層5と、コレクタ電極6とを備え、第1および第2有機半導体層3,5は、正孔輸送材料で形成され、各層を形成する有機半導体材料は、その分子構造に平面部分を有し、各分子の平面部分が基板7に対して略平行に配列し、その分子の形成するπ軌道が上下の分子のπ軌道と重なりを有し、分子が積層される配列方向に、エネルギー−波数(E−k)の関係を示す所定のバンド分散幅を有したエネルギーバンドを形成する。エミッタ電極2は、正孔を第1および第2有機半導体層3,5に注入する電極であり、エミッタ電極2およびコレクタ電極6は仕事関数が大きい材料、ベース電極4は仕事関数が小さい材料で形成されている。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】エミッタ接地直流増幅率のばらつきを低減し、かつ抵抗の増大を防止できる、信頼性に優れるバイポーラトランジスタを得ること。

【解決手段】本発明は、N−型エピ層3aやP−型シリコン基板1aを含む半導体基板、N+型ポリシリコン層21a、タングステン層25、シリサイド層27a、シリサイド層39a、ベース電極36a、エミッタ電極36b及びコレクタ電極36cを少なくとも備える。半導体基板上に形成されたN+型ポリシリコン層21aはシリサイド層27aに覆われる。シリサイド層27a上の形成されたタングステン層25はシリサイド層39aに覆われる。

(もっと読む)

化合物半導体エピタキシャル基板

【課題】電流増幅率を向上させ、基板種に影響されず良好な特性のデバイスを製造できる化合物半導体エピタキシャル基板を提供すること。

【解決手段】GaAs基板2上に、サブコレクタ層41、コレクタ層42、ベース層43、エミッタ層44、エミッタコンタクト層46、47がこの順序で形成されている化合物半導体エピタキシャル基板1において、GaAs基板2とサブコレクタ層41との間に形成されるバッファ層3を酸素を含むAlx Ga1-x As (0≦X≦1)層とし、酸素を含むバッファ層3によりGaAs基板2に存在する欠陥の伝播を抑制し、ベース層43の結晶性を基板種によらず安定かつ良好にできるようにした。

(もっと読む)

61 - 80 / 391

[ Back to top ]