Fターム[5F003BE90]の内容

バイポーラトランジスタ (11,930) | エミッタ (1,226) | 形状、段付エミッタ、エミッタメサ (391)

Fターム[5F003BE90]に分類される特許

141 - 160 / 391

グラフェントランジスタ及び電子機器

【課題】グラフェントランジスタ及び電子機器に関し、グラフェン膜を用いたチャネル層の特性を各場所で最適化することにより、グラフェントランジスタの性能を向上する。

【解決手段】一層以上のグラフェンからなる炭素膜12をキャリアが走行する能動領域とするとともに、前記能動領域を構成する前記炭素膜のキャリアの走行方向に垂直な方向の幅を場所によって変化させる。

(もっと読む)

半導体基板および半導体基板の製造方法

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】単結晶Siの基板と、基板の上に形成され、開口領域を有する絶縁層と、開口領域の基板上にエピタキシャル成長されたGe層と、Ge層の上にエピタキシャル成長されたGaAs層と、を備え、Ge層は、超高真空の減圧状態にできるCVD反応室に基板を導入し、原料ガスを熱分解できる第1温度で第1のエピタキシャル成長を実施し、第1温度より高い第2温度で第2のエピタキシャル成長を実施し、第1および第2のエピタキシャル成長を実施したエピタキシャル層をGeの融点に達しない第3温度で第1のアニールを実施し、第3温度より低い第4温度で第2のアニールを実施して形成された半導体基板を提供する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】Siの基板と、基板上に結晶成長され、孤立した島状に形成されたGe層と、Ge層上に結晶成長された機能層と、を備える半導体基板を提供する。Ge層は、アニールした場合に、アニールの温度および時間において結晶欠陥が移動する距離の2倍を越えない大きさの島状に形成する。あるいはGe層は、アニールした場合に、アニールの温度において基板であるSiとの熱膨張係数の相違によるストレスが剥離を発生させない大きさの島状に形成する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】Siの基板と、基板上に結晶成長され、孤立した島状に形成されたGe層と、Ge層の上に結晶成長され、Pを含む3−5族化合物半導体層からなるバッファ層と、バッファ層の上に結晶成長された機能層と、を備える半導体基板を提供する。Ge層は、アニールした場合に、アニールの温度および時間において結晶欠陥が移動する距離の2倍を越えない大きさの島状に形成する。あるいはGe層は、アニールした場合に、アニールの温度において基板であるSiとの熱膨張係数の相違によるストレスが剥離を発生させない大きさの島状に形成する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】Siの基板と、基板の上に形成され、結晶成長を阻害する阻害層とを備え、阻害層は、基板の一部を覆う被覆領域と、被覆領域の内部に基板を覆わない開口領域とを有し、さらに開口領域に結晶成長されたGe層と、Ge層上に結晶成長された機能層と、を備える半導体基板を提供する。当該半導体基板において、Ge層は、結晶欠陥が移動できる温度および時間でアニールされることにより形成されてよい。

(もっと読む)

トランジスタ構造および半導体装置

【課題】パワー半導体素子として、動作時の熱暴走および熱破壊が防止でき、且つ、安全動作領域SOAが拡大されるトランジスタを提供する。

【解決手段】第1導電型のコレクタ層2と、前記コレクタ層上に島状に形成され且つ前記第1導電型と異なる第2導電型のベース層3と、前記ベース層上に少なくとも1つの島状に形成され且つ前記第1導電型のエミッタ層4a,4bと、前記ベース層と電気的に接続されベースコンタクト9を形成するベース電極と、前記エミッタ層と電気的に接続されエミッタコンタクト10を形成するエミッタ電極と、前記コレクタ層と電気的に接続されたコレクタ電極と、を有し、前記エミッタ層上に形成され且つ前記第1導電型の第1抵抗層11が、平面的に見て、前記ベースコンタクトを包囲するように形成されることを特徴とするトランジスタ構造。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】電流利得、高周波特性が良好であり、かつ微細化することができるようにする。

【解決手段】基板1上に、コレクタ層3、ベース層4、エミッタ層およびキャップ層9を順次積層する。エミッタ層が、ベース層4に接したバリア層14とキャップ層9に接したキャリア供給層13との積層構造から形成されている。バリア層14のバンドギャップが、キャリア供給層13のバンドギャップよりも大きく、バリア層14とキャリア供給層13とが、タイプI型のヘテロ接合を形成している。キャリア供給層13を構成する半導体が、不純物添加によって縮退している。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタの周りで電位変動が発生した場合であっても、該電位変動の影響を受け難く、耐圧等の他の特性と両立できる、安価な半導体装置を提供する。

【解決手段】埋め込み酸化膜12上のSOI層13に、埋め込み酸化膜12に達する絶縁トレンチ17が形成され、該絶縁トレンチ17により取り囲まれたSOI層13からなる第1絶縁分離領域Z1に、バイポーラトランジスタTr1が形成されてなる半導体装置100であって、第1絶縁分離領域Z1を取り囲む絶縁トレンチ17の外側のフィールド領域Fが、バイポーラトランジスタTr1に印加される最高電位Vmaxと同じ電位に設定されてなる半導体装置100とする。

(もっと読む)

電極構造、ヘテロ接合バイポーラトランジスタおよびそれらの製造方法

【課題】Auの拡散を抑制して、電流利得が突然劣化するのを防止する。

【解決手段】基板1上にサブコレクタ層2を形成し、サブコレクタ層2上にコレクタ層3を形成し、コレクタ層3上にベース層4を形成し、ベース層4上にエミッタ層5を形成し、エミッタ層5上にエミッタコンタクト層6を形成し、エミッタコンタクト層6上にTiからなるコンタクト用金属層7を形成し、コンタクト用金属層7上にWからなるAu拡散防止用のバリアメタル層8を形成し、バリアメタル層8上にTi/Pt/Au/Pt/Tiからなる低抵抗金属層9を形成し、エミッタ層5、エミッタコンタクト層6およびコンタクト用金属層7、バリアメタル層8、低抵抗金属層9からなるエミッタ電極の側面を覆うシリコン窒化膜10を形成する。

(もっと読む)

半導体を用いた電子デバイス

【課題】高耐圧電子デバイスおよび耐環境電子デバイスを提供する。

【解決手段】本発明においては、ダイオードやトランジスタ等の電子デバイス中で電子が走行する領域に、高純度の酸化モリブデンであって、その禁制帯幅が3.45eV以上であるような酸化モリブデンが用いられる。本発明によれば、高耐圧特性および高耐環境特性を有する電子デバイスが実現できる。

(もっと読む)

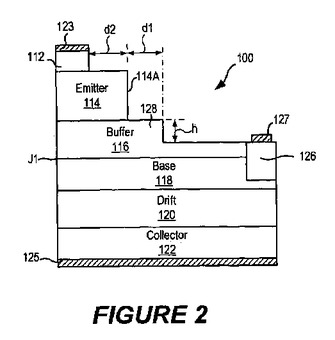

メサ構造とメサ段差を含むバッファ層とを備えた電力半導体デバイス

バイポーラ接合トランジスタが、第1の導電型を有するコレクタと、このコレクタ上の、第1の導電型を有するドリフト層と、このドリフト層上の、第1の導電型と反対の第2の導電型を有するベース層と、このベース層上の、低濃度でドープされ第1の導電型を有しベース層とp−n接合部を形成するバッファ層と、このバッファ層上の第1の導電型を有し側壁を有するエミッタメサとを含む。バッファ層は、エミッタメサの側壁の近傍でそこから横方向に間隔を置いて配置されたメサ段差を含み、エミッタメサの下のバッファ層の第1の厚さは、メサ段差外側のバッファ層の第2の厚さよりも厚い。  (もっと読む)

(もっと読む)

複合バイポーラトランジスタ、複合バイポーラトランジスタを用いた半導体デバイスおよび電子機器

【課題】コレクタ‐エミッタ間の飽和電圧を大きくすることなく、熱暴走時の破壊に至るまでの時間を長くする。

【解決手段】エミッタ電極パッド30近傍の領域外では、エミッタ電極パッド30から遠ざかるに連れて島状のベース層22の一辺を短くする一方、上記領域内においては、メッシュエミッタ層23周辺のベース層22および島状のベース層22にエミッタ層23と同じ導電型の拡散層31を形成し、この拡散層31の幅をエミッタ電極パッド30に近づくに連れて広くする。こうして、エミッタ電極パッド30から遠ざかるに連れて、バラスタ抵抗を含むベース抵抗を小さくする。その結果、エミッタ電極パッド30に近いユニットトランジスタほどベース電流が小さくなって電流の集中が緩和され、熱暴走による破壊が起こり難くなる。また、従来のベースにバラスタ抵抗を配置したメッシュエミッタトランジスタよりもコレクタ‐エミッタ間飽和電圧が大きくならない。

(もっと読む)

半導体装置および半導体集積回路装置

【課題】半導体集積回路装置の高集積化及び低コスト化を可能にする複数のトランジスタセルを含む半導体装置を提供することを第1の目的とし、高密度に集積化された小型の半導体集積回路装置を安価に提供する。

【解決手段】基板上に、それぞれ第1層、ベース層、及び、第2層を順に有し、前記第1層、及び、前記第2層の一方がコレクタ層であり、他方がエミッタ層であるトランジスタセルを複数含み、前記各トランジスタセルの前記第1層に接続される第1電極が、前記第1層に形成されたエッチング溝に形成された半導体装置において、前記エッチング溝は、その長手方向に沿った側面が順メサ面となっており、複数のトランジスタセル間の前記第1電極が、前記各順メサ面に交差するように設けられた、まとめ配線によって接続される半導体装置である。

(もっと読む)

半導体装置とその製造方法

【課題】 複数個の半導体素子を備えている半導体装置において、その半導体装置のサイズを小さくする技術を提供する。

【解決手段】 不純物注入工程では、半導体基板9の表面にn型半導体領域13とp型半導体領域14が隣接して出現する関係に不純物の注入範囲を管理して、不純物を半導体基板9に注入する。熱処理工程では、半導体基板9を加熱して半導体基板9に注入した不純物12、14を活性化する。トレンチ形成工程では、半導体基板9の表面に隣接して出現しているn型半導体領域13とp型半導体領域14の双方を分断して一巡するととともに半導体基板9の表面から半導体基板9の裏面に向けて不純物の注入範囲12、14を貫通する深さにまで伸びているトレンチ15を形成する。絶縁膜形成工程では、トレンチ15内に絶縁膜を形成する。

(もっと読む)

バイポーラ素子及びその製造方法

【課題】メサ型バイポーラトランジスタあるいはサイリスタでは、エミッタ層あるいはアノード層からベース層あるいはゲート層に注入されたキャリアが横方向に拡散し再結合する結果、小型化やスイッチング周波数の向上が困難であった。

【解決手段】エミッタ層あるいはアノード層を高濃度および低濃度からなる二層で構成し、この低濃度層と同一の不純物密度を有する同一の半導体からなる再結合抑制半導体領域をベース層またはゲート層と表面保護絶縁膜とに接して存在させるとともに、この再結合抑制半導体領域の幅をキャリアの拡散距離以上に設定する。このことにより、バイポーラトランジスタの小型化やサイリスタのスイッチング周波数向上を、性能を損なわず実現できる効果がある。また、上記バイポーラトランジスタの高濃度エミッタ層上に、正孔バリア層、伝導帯不連続緩和層、及びエミッタコンタクト層を順次積層することにより、電流増幅率を大幅に向上できる効果がある。

(もっと読む)

相分離が抑制されたIII族窒化物材料系を用いた半導体構造及び光検出器

【課題】レーザダイオード、トランジスタ、光検出器などの半導体構造に使用され、相分離を抑制または解消するとともに発光効率を向上させるIII族窒化物4元及び5元材料系並びに方法を提供する。

【解決手段】典型的な実施形態では、半導体構造は、ほぼ相分離なく形成された第1導電型のBAlGaN材料系を用いた4元材料層と、ほぼ相分離のないBAlGaN材料系を用いた4元材料活性層と、ほぼ相分離なく形成された逆導電型のBAlGaN材料系を用いた別の4元材料層を備えている。

(もっと読む)

選択的エピタキシまたは選択的注入の使用による、炭化ケイ素におけるセルフアライントランジスタおよびダイオードトポロジー

【課題】SiC内に縦型ダイオードおよびトランジスタを作る方法が提供される。

【解決手段】この発明に従った方法は、マスク(たとえば機構を素子にエッチングするために以前使用されたマスク)を選択的エピタキシャル成長または選択的イオン注入用に使用する。このように、静電誘導トランジスタおよびバイポーラ接合トランジスタのゲート領域およびベース領域が、セルフアラインプロセスで形成可能である。プレーナダイオードおよびプレーナエッジ終端構造(たとえばガードリング)を作る方法も提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】電流リーク及び寄生抵抗が抑制され、安定した電流利得を実現する半導体装置を提供する。

【解決手段】n型コレクタ層102上に、第一の半導体層110を成長させつつ、p型多結晶シリコン膜106、シリコン窒化膜108を含む積層膜からなる庇部の下面に露出したp型多結晶シリコン膜106の下方に第一の多結晶半導体層120を成長させ、その後第一の多結晶半導体層120を選択的に除去する。さらに第二の半導体層112、114、第三の半導体層116を成長させつつ、庇部の下面に露出したp型多結晶シリコン膜106の下方に第二の多結晶半導体層122、124、第三の多結晶半導体層126を、シリコン窒化膜108に接触しないように選択的に成長させ、第三の半導体層と、第三の多結晶半導体層を接触させる。

(もっと読む)

トランジスタ素子

【課題】電流利得が高いトランジスタ素子を提供する。

【解決手段】基板2上にヘテロバイポーラトランジスタ3が形成され、該ヘテロバイポーラトランジスタ3上に高電子移動度トランジスタ4が形成されたトランジスタ素子1において、上記ヘテロバイポーラトランジスタ3のベース層8の層厚が120nm以上である。

(もっと読む)

窒化物系半導体素子

【課題】オーミック電極と窒化物系半導体層とのオーミック特性が熱により劣化するのを抑制することが可能な窒化物系半導体素子を提供する。

【解決手段】この窒化物系半導体素子(窒化物系半導体レーザ素子)は、p側オーミック電極6に、約1nmの厚みを有するとともにp型コンタクト層5の主表面に接触して形成されるSi層6aと、Si層6a上に形成される約20nmの厚みを有するPd層6bとを含むとともに、n側オーミック電極9に、約1nmの厚みを有するとともにn型GaN基板1の下面に接触して形成されるSi層9aと、Si層9aの下面上に形成される約6nmの厚みを有するAl層9bと、Al層9bの下面上に形成される約30nmの厚みを有するPd層9cとを含む。

(もっと読む)

141 - 160 / 391

[ Back to top ]