Fターム[5F003BE90]の内容

バイポーラトランジスタ (11,930) | エミッタ (1,226) | 形状、段付エミッタ、エミッタメサ (391)

Fターム[5F003BE90]に分類される特許

41 - 60 / 391

バイポーラトランジスタおよびその製造方法

【課題】HBTの高速性および信頼性が向上できるようにする。

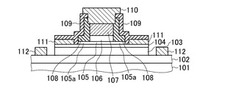

【解決手段】エミッタメサの部分の側面およびレッジ構造部105aの表面には、これらを被覆するように、窒化シリコン(SiN)からなる第1絶縁層108が形成されている。また、第1絶縁層108の周囲からベース電極111の上面にかけて(渡って)窒化シリコンからなる第2絶縁層109が形成されている。第2絶縁層109は、第1絶縁層108の側面、レッジ構造部105aとベース電極111との間のベース層104の上、およびベース電極111の上面を覆うように形成されている。基板101の平面方向において、レッジ構造部105aの外形は第1絶縁層108の外形と同じに形成されている。また、エミッタメサより離れる方向のベース電極111の外周部分が、第1絶縁層108の外周部分に重なって形成されている。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】ダイヤモンド薄膜内に存在する結晶欠陥、不純物等を減少させ、高品質なダイヤモンド薄膜を作製可能なダイヤモンド薄膜作製方法を提供すること。

【解決手段】ダイヤモンドが安定な高圧力下でアニールを行う。これにより、結晶中に含まれる格子欠陥等が回復、除去され、ダイヤモンド結晶薄膜を高品質化する事ができる。「(ダイヤモンドが)安定な、安定に」とは、ダイヤモンドがグラファイト化せずにダイヤモンドの状態を保つ状態を指す。ダイヤモンドが安定にアニール出来る領域内でアニールを行う温度(アニール温度、とも呼ぶ)Tおよびアニールを行う圧力(アニール圧力、とも呼ぶ)Pが決定される。この領域は、図21に示される、P>0.71+0.0027TまたはP=0.71+0.0027Tを満たし、なおかつP≧1.5GPaの領域である。このような領域は、図21中の斜線部分である。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】エミッタメサの加工精度を損ねることなく、HBTの高速性および信頼性が向上できるようにする。

【解決手段】エミッタメサの部分の側面およびレッジ構造部105aの表面には、これらを被覆するように、SiNからなる第1絶縁層108が形成されている。また、第1絶縁層108の周囲には、酸化シリコンからなる第2絶縁層109が形成されている。第2絶縁層の下端部には、レッジ構造部1105aが形成されている領域より外側に延在し、第1絶縁層108およびレッジ構造部105aの側方のベース層104との間に空間を形成する庇部109aが形成されている。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】薄膜トランジスタ用半導体層の材料として、高い正孔移動度を示すp形半導体多結晶薄膜を、かつ、低い成膜温度でのプラスチック基板上への成膜をも行うことのできるp形半導体多結晶薄膜を、提供する。

【解決手段】ガラスまたはプラスチックまたはステンレス基板のような非結晶質または多結晶基板1上に、該基板の温度を300℃以下とし、成長膜へのガリウム(Ga)、アンチモン(Sb)、及びヒ素(As)原子のそれぞれの供給量JGa,JSb,及びJAsを、JSb<JGa<JAs+JSbを満たすような値として、Ga,Sb,及びAs原子を同時供給して真空蒸着により成膜してなる、Sb組成yが0.5<y<1を満たすp形GaSbyAs1-y多結晶薄膜6を形成する製造方法による。

(もっと読む)

電流増幅素子

【課題】なだれ増倍を利用して電流を直接増幅することが可能であると共に、リニアモード動作において、高感度と応答速度の速さとを両立させることができる電流増幅素子を提供する。

【解決手段】電流増幅素子は、半導体基板の表面に平面視が円形となるように中心軸の周りに対称に形成されたn型半導体ウエル(n−ウエル)104、n−ウエル内に同心円状に形成されたp型半導体領域112、p型半導体領域内に同心円状に形成されたn型半導体領域112、及び順バイアス電圧と逆バイアス電圧とを印加するための複数の電極を備えている。n−ウエルの内側の面は、中心軸から予め定めた距離の範囲内では基板裏面に向って半径が小さくなると共に、範囲より外側では基板裏面に向って半径が大きくなるように形成されている。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】HBTによる段差を低減し、接合面積をより小さくできるようにする。

【解決手段】半絶縁性のInPからなる基板101の上に形成されたアンドープInPからなる第1半導体層102と、第1半導体層102の上に接して形成された第1導電型のInPからなるエミッタ層103と、第1半導体層102の上に接して形成された第2導電型のInGaAsからなるベース層106と、第1半導体層102の上に接して形成されたInGaAsからなるコレクタ層107とを少なくとも備える。加えて、エミッタ層103,ベース層106,およびコレクタ層107は、これらの順に第1半導体層102の平面上で配列して接続されている。

(もっと読む)

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】CMOS回路側の仕様で不純物領域の深さや濃度が制約を受けるような場合でもhFEの向上を可能とする。

【解決手段】1つのバイポーラトランジスタが、横型の主トランジスタ部と、縦型の補助トランジスタ部とから形成されている。横型の主トランジスタ部は、エミッタ領域31と、ベース領域14Bの表面側部分とコレクタ側部領域13Bとを電流チャネルとして動作する。縦型の補助トランジスタ部は、エミッタ領域31と、その底面に接するベース領域14Bの深部側部と、コレクタ深部領域12Bとを電流チャネルとして動作する。

(もっと読む)

半導体基板及び半導体発光素子

【課題】 GaN基板上に結晶成長する各半導体層の平坦性が、半導体素子の寸法相当において向上した半導体基板を提供し、更には、この半導体基板を基礎として、特性の高性能化された半導体発光素子、半導体素子を提供する。

【解決手段】基板11と、この基板11上に積層された窒化物系III−V族化合物半導体単結晶層12と、基板11と窒化物系III−V族化合物半導体単結晶層12との間に設けられた、不純物元素を5x1017cm-3以上2x1019cm-3以下含有する層10とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSプロセスへの導入が容易で、エミッタ−ベース間のリーク電流(電界強度)を低減し、ノイズやサージ電圧の影響を受けにくい高性能な半導体装置とその製造方法の提供。

【解決手段】導電膜をマスクとして、2回のイオン注入を行ってエミッタを形成する。第2エミッタ領域111bは、低濃度の不純物イオン注入によって形成し、第1エミッタ領域111aは、高濃度の不純物イオン注入によって形成する。その結果、エミッタの周縁部に低濃度の第2エミッタ領域が形成され、電界が緩和され、リーク電流が低減する。また、導電膜とエミッタ電極116とが接続され、ノイズの影響を受けにくくなる。

(もっと読む)

横方向のエミッタおよびコレクタを有するバイポーラトランジスタならびに製造方法

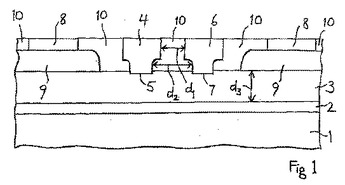

バイポーラトランジスタは、半導体材料からなる基板(1)と、基板内の高移動度層(2)と、高移動度層に隣接したドナー層(3)とを含む。エミッタ端子(4)がドナー層上のエミッタコンタクト(5)を形成し、コレクタ端子(6)がドナー層上のコレクタコンタクト(7)を形成する。ベース端子(8)が高移動度層に導電接続される。当該トランジスタは、GaAsのHEMT技術またはBiFET技術で製造可能である。  (もっと読む)

(もっと読む)

半導体基板、電子デバイスおよび半導体基板の製造方法

【課題】エピタキシャル成長により形成された結晶膜の成長面内における物性値を均一な値に近づける。

【解決手段】第1化合物半導体および第2化合物半導体を積層した積層半導体を含み、前記第1化合物半導体の所定物性値が第1面内分布を有し、前記第2化合物半導体の前記所定物性値が前記第1面内分布とは異なる第2面内分布を有し、前記積層半導体における前記所定物性値の面内分布の幅が、前記第1面内分布の幅または前記第2面内分布の幅より小さい半導体基板を提供する。

(もっと読む)

バイポーラ半導体素子

【課題】高温や電流密度が高い条件下でも基板へ少数キャリアが到達するのを防いで、順方向電圧の増大を防ぐことができるバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20では、n型SiC基板21とn型バッファ層22との間に形成したn型少数キャリア消滅層31は、n型バッファ層22よりも炭素空孔欠陥の濃度が高く、少数キャリア消滅層31の炭素空孔欠陥はp型のアノード層24,25からの正孔のトラップとして働く。よって、小数キャリア消滅層31に達した正孔(少数キャリア)がトラップされ、小数キャリア消滅層31において正孔密度K2が急激に減衰する。これにより、正孔(少数キャリア)が基板21へ到達することを防いで、基板21から積層欠陥が拡大するのを防いで、順方向電圧の増大を防止できる。

(もっと読む)

増大した直線性および製造可能性を有するFETを含むBiFET

【課題】基板上に位置するBiFETにおいて、HBT性能の低下を引起すことなくFETの製造可能性増大を達成させる。

【解決手段】基板上に位置するBiFET100は、基板の上に位置するエミッタ層部分122を含み、エミッタ層部分は第1のタイプの半導体を含む。HBTはエッチストップ層の第1の部分126をさらに含み、エッチストップ層の第1の部分はInGaPを含む。BiFETは基板の上に位置するFET106をさらに含み、FETはソース領域およびドレイン領域を含み、エッチストップ層の第2の部分146はソース領域およびドレイン領域の下に位置し、エッチストップ層の第2の部分はInGaPを含む。FETはエッチストップ層の第2の部分の下に直接接して位置する第2のタイプの半導体層をさらに含む。エッチストップ層はFETの線形性を増大させ、HBTの電子の流れを低下させない。

(もっと読む)

大面積ナノ可能マクロエレクトロニクス基板およびその使用

【課題】複数の半導体デバイスを有する電子的な基板を得るための方法および装置。

【解決手段】ナノワイヤ薄膜が、基板上に形成される。ナノワイヤ薄膜は、動作電流レベルを達成するのに十分なナノワイヤの密度を有するように形成される。複数の半導体領域が、ナノワイヤ薄膜に画定される。コンタクトが、半導体デバイス領域において形成され、それによって、電気的な接続を複数の半導体デバイスに提供する。さらに、ナノワイヤを製造するための様々な材料、p型ドーピングナノワイヤおよびn型ドーピングナノワイヤを含む薄膜、ナノワイヤヘテロ構造、発光ナノワイヤヘテロ構造、ナノワイヤを基板上に配置するためのフローマスク、ナノワイヤを成膜するためのナノワイヤ噴霧技術、ナノワイヤにおける電子のフォノン散乱を減少または除去するための技術、および、ナノワイヤにおける表面準位を減少させるための技術が、説明される。

(もっと読む)

SiC結晶成長層の製造方法およびバイポーラ型半導体素子

【課題】層厚さが厚くてもSiC結晶中にある炭素空孔を低減できるSiC結晶成長層の製造方法を提供する。

【解決手段】SiC結晶成長層としてのドリフト層23を成長させる工程内に、シリコン原料ガスであるシランと炭素原料ガスであるプロパンのうちのプロパンのみを結晶成長表面に供給する第2の期間を設けている。このことで、結晶成長表面の炭素の過飽和度を上げ、成長途中の表面に過剰な格子間炭素を発生させる。これにより、成長後のSiC結晶成長層としてのドリフト層23の表面から離れている比較的深い箇所での炭素空孔を減少させることができる。

(もっと読む)

ヘテロ接合バイポーラトランジスタ、及び、ヘテロ接合バイポーラトランジスタの製造方法

【課題】良好なIn組成比及び結晶性を有するヘテロ接合バイポーラトランジスタ、及び、ヘテロ接合バイポーラトランジスタの製造方法を提供する。

【解決手段】六方晶系窒化ガリウム系半導体からなりn型窒化ガリウム系半導体層5bを有するコレクタ層5と、Inを含むp型窒化ガリウム系半導体層からなり、コレクタ層5の主面S4に設けられたベース層7と、他のn型窒化ガリウム系半導体層からなり、ベース層7の主面S5に設けられたエミッタ層9と、を備えるヘテロ接合バイポーラトランジスタ1であって、コレクタ層5の主面S4は、コレクタ層5の六方晶系窒化ガリウム系半導体のc軸に対して60度以上80度以下の角度で傾斜している。

(もっと読む)

有機トランジスタ、回路素子及びそれらの製造方法

【課題】低電圧で作動するとともに大きなベース電圧を印加した場合でも耐電圧が高く、各種の回路素子への応用が容易で、製造コストを抑えた有機トランジスタ及び回路素子を提供する。

【解決手段】コレクタ電極1とエミッタ電極2と両電極間に設けられた有機半導体層3と有機半導体層3内に設けられたベース電極4とを有する縦型トランジスタ部、及び、ベース電極4とベース電圧電源端子7との間に設けられた抵抗部6、を有する。抵抗部6は、コレクタ電極1と同じ材料からなりベース電圧電源端子7に接続する第1電極21と、エミッタ電極2と同じ材料からなりベース電極4に接続する第2電極22と、有機半導体層3と同じ材料からなり第1電極21及び第2電極22間に挟まれた抵抗層24とを有する。

(もっと読む)

半導体基板

【課題】AlGaAs/InGaP界面の遷移層の形成を抑制する。

【解決手段】ヒ素化合物からなる第2半導体と、リン化合物からなる第3半導体とを含み、前記第2半導体と前記第3半導体とが接触しており、前記第2半導体が第1原子を第2濃度で含有し、かつ第2原子を含有し、前記第1原子が前記第2半導体に第1伝導型のキャリアを発生させ、前記第2濃度が、前記第2半導体にドープする前記第1原子の量を増加するに従い増加するキャリア数が飽和し始める前記第1原子の濃度以上の濃度であり、前記第2原子が前記第2半導体におけるフェルミ準位と電荷中性準位との差を小さくする半導体基板提供する。

(もっと読む)

41 - 60 / 391

[ Back to top ]