Fターム[5F003BH18]の内容

バイポーラトランジスタ (11,930) | 電極、配線 (1,046) | 断面形状 (205)

Fターム[5F003BH18]に分類される特許

41 - 60 / 205

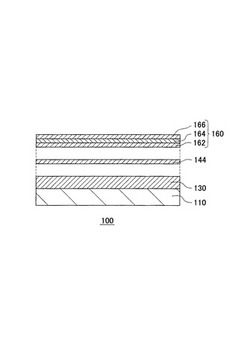

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】単一半導体基板上にHBTおよびFETのような異なる種類の複数デバイスを形成するに適した化合物半導体基板を提供する。

【解決手段】第1半導体110と、第1半導体上に形成された、電子捕獲中心または正孔捕獲中心を有するキャリアトラップ層130と、キャリアトラップ層上にエピタキシャル成長され、自由電子または自由正孔が移動するチャネルとして機能する第2半導体144と、第2半導体上にエピタキシャル成長したN型半導体/P型半導体/N型半導体で表される積層体、または前記第2半導体上にエピタキシャル成長したP型半導体/N型半導体/P型半導体で表される積層体を含む第3半導体160とを備える半導体基板。

(もっと読む)

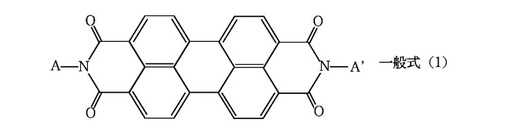

トランジスタ素子

【課題】エミッタ電極−コレクタ電極間において、オフ電流が小さく、かつ、低電圧で大電流変調が可能であるオン/オフ比に優れたトランジスタ素子を提供すること。

【解決手段】エミッタ電極とコレクタ電極との間に、有機半導体層とシート状のベース電極とが設けられているトランジスタ素子において、該有機半導体層が、下記一般式(1)で表される化合物を含んでいるトランジスタ素子。 (もっと読む)

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】エミッタ接地直流増幅率のばらつきを低減し、かつ抵抗の増大を防止できる、信頼性に優れるバイポーラトランジスタを得ること。

【解決手段】本発明は、N−型エピ層3aやP−型シリコン基板1aを含む半導体基板、N+型ポリシリコン層21a、タングステン層25、シリサイド層27a、シリサイド層39a、ベース電極36a、エミッタ電極36b及びコレクタ電極36cを少なくとも備える。半導体基板上に形成されたN+型ポリシリコン層21aはシリサイド層27aに覆われる。シリサイド層27a上の形成されたタングステン層25はシリサイド層39aに覆われる。

(もっと読む)

有機縦型トランジスタ

【課題】キャリア移動度が高く、低駆動電圧で大電流変調を可能とする有機縦型トランジスタを提供すること。

【解決手段】有機縦型トランジスタ1は、基板7と、エミッタ電極2と、第1有機半導体層3と、ベース電極4と、第2有機半導体層5と、コレクタ電極6とを備え、第1および第2有機半導体層3,5は、正孔輸送材料で形成され、各層を形成する有機半導体材料は、その分子構造に平面部分を有し、各分子の平面部分が基板7に対して略平行に配列し、その分子の形成するπ軌道が上下の分子のπ軌道と重なりを有し、分子が積層される配列方向に、エネルギー−波数(E−k)の関係を示す所定のバンド分散幅を有したエネルギーバンドを形成する。エミッタ電極2は、正孔を第1および第2有機半導体層3,5に注入する電極であり、エミッタ電極2およびコレクタ電極6は仕事関数が大きい材料、ベース電極4は仕事関数が小さい材料で形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、容量素子の誘電体膜の膜厚がフォトレジストの剥離の際に一部除去され、その容量値がばらつき、耐圧特性が劣化するという問題があった。

【解決手段】本発明の半導体装置では、容量素子1の下部電極8上面に誘電体膜としてのシリコン窒化膜12が形成され、シリコン窒化膜12上面に上部電極15が形成される。上部電極15は、シリコン窒化膜12を保護する多結晶シリコン膜13とシリコン膜14の積層構造から成る。この構造により、フォトレジストの剥離の際等にシリコン窒化膜12の一部が除去され、容量素子1の容量値がばらつきや耐圧劣化が防止される。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法

【課題】アスペクト比の高いサブミクロンサイズのエミッタ電極パタンを線幅制御性良く形成することを可能とするヘテロ接合バイポーラトランジスタの製造方法を提供すること。

【解決手段】エミッタコンタクト層6上にTi層(図示せず)、エッチングストッパー用のW層7、Au層8、エッチングマスク用W層9、フォトレジストパタン10を形成し、フォトレジストパタン10をマスクとしてエッチングマスク用W層9を選択的に除去することによってWパタン9とし、Wパタン9をマスクとして、Au層8を、酸素ガスを含有する混合ガスを用いる反応性イオンエッチング法により選択的に除去し、Wパタン9をマスクとして、エッチングストッパー用のW層7、Ti層を選択的に除去することを特徴とするヘテロ接合バイポーラトランジスタの製造方法を構成する。

(もっと読む)

半導体装置

【課題】製造後に電流増幅率hFE特性を変化させることができるバイポーラトランジスタを備えた半導体装置を提供する。

【解決手段】P型半導体層1に、N型拡散層からなるコレクタ3、P型拡散層からなるベース5、N電型拡散層からなるエミッタ7が形成されてバイポーラトランジスタが形成されている。そのバイポーラトランジスタはベース5上及びコレクタ3にゲート絶縁膜9を介してゲート電極11を備えている。コレクタ3にはコレクタ配線13が接続されている。ベース5にはベース配線15が接続されている。エミッタ7にはエミッタ配線17が接続されている。ゲート電極11にはゲート電極配線19が接続されている。配線13,15,17,19は互いに電気的に絶縁されている。

(もっと読む)

半導体装置

【課題】統合型のインテリジェントスイッチデバイス、統合型の入力信号・伝達ICまたは統合型のパワーICなどに用いられる横型MOSFETにおいて、複雑な分離構造を用いずに、より小さいチップ面積で高ESD耐量および高サージ耐量を具えた半導体装置を提供する。

【解決手段】P型半導体よりなるエミッタ領域25、ベース領域として機能するNウェル領域10およびP型エピタキシャル成長層13およびP型半導体基板12をコレクタとするベースオープンの縦型バイポーラトランジスタの表面電極26と、横型MOSFETのドレイン電極22とを金属電極配線27により電気的に接続し、高ESD電圧や高サージ電圧が印加されたときに、ベースオープンの縦型バイポーラトランジスタの動作によりESDおよびサージエネルギーを吸収するとともに、破壊に至る横型MOSFETの降伏耐圧以下の電圧に制限する。

(もっと読む)

半導体装置

【課題】高耐圧化及び高温動作を実現できる、HBTとFETを備える半導体装置を提供する。

【解決手段】本発明に係る半導体装置100は、基板101の上に順時積層されたn+型GaN層103及びn型GaN層104と、p型InGaN層105と、アンドープGaN層106及びn型AlGaN層107と、HBT領域121のn+型GaN層103と電気的に接続されたコレクタ電極114と、HBT領域121のp型InGaN層105と電気的に接続されたベース電極113と、HBT領域121のn型AlGaN層107と電気的に接続されたエミッタ電極112と、HFET領域120のn型AlGaN層107と電気的に接続されたソース電極109及びドレイン電極111と、n型AlGaN層107の上に形成されたゲート電極110とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】線形性に優れた半導体抵抗素子を提供する。

【解決手段】本発明の半導体装置は、GaAs基板101上に形成され、3−5族化合物半導体から構成されるHBT130と、GaAs基板101上に形成され、HBT130を構成する半導体エピタキシャル層の少なくとも1層から構成される半導体抵抗素子120とを備え、半導体抵抗素子120は、ヘリウム不純物を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ高製造歩留まりで、BiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】シャロートレンチ3、ディープトレンチ6に囲まれた半導体層2の基板領域17に、p型の単結晶半導体からなるエピタキシャル・ベース層24が島状に形成される。当該島状領域を含む半導体層2上の全面に窒化シリコン膜42、酸化シリコン膜43が形成される。島状領域上の異なる位置の窒化シリコン膜42、酸化シリコン膜43には、少なくとも2つの開口部が形成され、開口部が形成された窒化シリコン膜42、酸化シリコン膜43上に半導体膜44が形成される。当該半導体膜44が選択的に除去され、一方の開口部において島状領域に接続するベース電極と、他方の開口部において島状領域に接続するエミッタ電極とが同時に形成される。

(もっと読む)

半導体装置

【課題】 同一基板上に形成された半導体素子間に流れる寄生電流による半導体素子の誤動作を抑制する構造を有する半導体装置を提供することを目的とする。

【解決手段】

p型半導体基板1に電気的に接続されたn型のコレクタ引き出し層53を備えた小信号素子であるバイポーラトランジスタ50と、p型半導体基板1に電気的に接続されたn型拡散層67を備えたパワートランジスタ素子であるDMOSトランジスタ60と、p型半導体基板1に電気的に接続され、かつ、ダミー電極13に接続されたn型のダミーN島10と、p型半導体基板1に電気的に接続され、かつ、フィールド電極23に接続されたp型のフィールド部20と、ダミー電極13とフィールド電極23を接続し、ボンディングパット70に接続する配線30とを備える。

(もっと読む)

シリコン基板上に形成されるCMOSデバイスおよびIII−V族デバイスのための電気コンタクト

半導体構造体は、基板(12)と、基板を覆うシード層(13)と、シード層上に配置されるシリコン層(22)と、シリコン層中のトランジスタデバイス(27)と、シード層上に配置されるIII−V族デバイスと、複数の電気コンタクトと、を備え、それぞれの電気コンタクトは、TiNまたはTaNの層(32)と、TaNまたはTiNの層上の銅またはアルミニウムの層(34)と、を備え、電気コンタクトの1つは、トランジスタ(27)に電気的に接続され、電気コンタクトの別の1つは、III−V族デバイスに電気的に接続される。 (もっと読む)

半導体装置および半導体装置の製造方法

【課題】寄生容量を低減しつつ、トランジスタが形成される半導体層に歪応力を与える。

【解決手段】半導体層3に形成されたコレクタ層3aの表面および裏面にストレス印加層5を形成し、ストレス印加層5を介して埋め込み絶縁層6上に配置されたベース層9をコレクタ層3aの側壁に選択的に形成し、ベース層9の側壁を絶縁膜10から露出させる開口部12を形成し、開口部12を介してベース層9の側壁に接続されたエミッタ層13aを埋め込み絶縁層6上に形成する。

(もっと読む)

トランジスタ素子及びその製造方法並びに発光素子及びディスプレイ

【課題】エミッタ電極−コレクタ電極間において、低電圧で大電流変調を可能とするトランジスタ素子を提供する。また、そうしたトランジスタ素子の製造方法、また、そのトランジスタ素子有する発光素子及びディスプレイを提供する。

【解決手段】エミッタ電極3とコレクタ電極2との間に、半導体層5(5A,5B)とシート状のベース電極4が設けられているトランジスタ素子により、上記課題を解決する。半導体層5は、エミッタ電極3とベース電極4との間及びコレクタ電極2とベース電極4との間に設けられて、それぞれ第2半導体層5B及び第1半導体層5Aを構成し、さらに、ベース電極の厚さが80nm以下であることが好ましい。また、少なくともエミッタ電極とベース電極との間又はコレクタ電極とベース電極との間には、暗電流抑制層が設けられていてもよい。

(もっと読む)

半導体装置およびその製造方法

【課題】電気特性、熱伝導特性に優れ、長寿命および低コストの半導体装置およびその製造方法を提供する。

【解決手段】半導体チップ1と、半導体チップ1のエミッタ側に接合されるエミッタ電極2と、半導体チップ1のコレクタ側に接合されるコレクタ電極3と、エミッタ電極2の半導体チップ1と反対側に接合される第1放熱体4と、コレクタ電極3の半導体チップ1と反対側に接合される第2放熱体5と、半導体チップ1とエミッタ電極2と第1放熱体4、半導体チップ1とコレクタ電極3と第2放熱体5を接合する接合材料(2a、2b、2c、3a、3b、3c)とを具備するモジュール半導体装置において、接合材料(2a、2b、2c、3a、3b、3c)をエミッタ電極2、コレクタ電極3および第1放熱体4および第2放熱体5の表面に予め形成したことを特徴とする半導体装置およびその製造方法。

(もっと読む)

半導体装置及びその製造方法並びにその半導体装置を用いたスーパーヘテロダイン方式の通信機

【課題】バイポーラトランジスタのベース走行時間の低減とエミッタ・ベース接合容量の低減により、遮断周波数と低電流駆動性能の向上を図ったバイポーラトランジスタを提供する。

【解決手段】半導体基板上に設けられた第1導電型の第1の半導体層5と、前記第1の半導体層の上に設けられた第1導電型の第2半導体層6と、前記第2半導体層上に設けられた第2導電型の第3の半導体層7と、該第3の半導体層上に設けられ、開口部を有する第1の絶縁膜9と、前記開口部内に設けられた第1導電型の第4の半導体層11と、前記第4の半導体層上に設けられた第1導電型の第5の半導体層13とで構成され、第4の半導体層が第1の絶縁膜の側壁に接しないように形成し、少なくとも前記第4の半導体層と第1の絶縁膜で囲まれた空洞12を有して成ることを特徴とする。

(もっと読む)

P型電界効果トランジスタ及びその製造方法

【解決手段】GaAsを用いることができる基板(1)の上方にn層(3)が配置され、前記n層上にp層(4)が配置される。前記p層は、ゲート電極(10)によって2つの別個の部分に分けられ、ソース及びドレインが形成されている。前記ゲート電極は、ゲート絶縁膜(6)によって半導体材料から絶縁されている。ソース/ドレインコンタクト(11)が、前記p層の前記2つの別個の部分に電気的に接続されている。 (もっと読む)

トランジスタ素子およびその製造方法

【課題】

ベース電極とコレクタ半導体の電荷注入障壁の制御が可能である、高性能な縦型薄膜のトランジスタ素子および製造方法を提供する。

【解決手段】

基板10上に、第一電極20と、コレクタ半導体層30と、ベース電極40と、エミッタ半導体層31と、第二電極21とを順次積層するトランジスタ素子において、コレクタ半導体層とエミッタ半導体層の間にベース電極が存在するようにするとともに、コレクタ半導体層が金属酸化物よりなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】外部からの高周波ノイズに対して誤動作しにくい半導体装置およびその製造方法を提供する。

【解決手段】n型コレクタ層11上に配置されたp型ベース層12bと、p型ベース層12b上に配置されたn型エミッタ層13bと、p型ベース層12b上にp型ベース層12bを包囲するように配置されたn型ベースコンタクト層21と、n型コレクタ層11上にp型ベース層12bと離隔して配置されたp型アノード層12cと、n型エミッタ層13bに接続されたエミッタ電極16cと、p型ベース層12bおよびn型ベースコンタクト層21に接続されたベース電極16aと、p型アノード層12cに接続され、かつエミッタ電極16cと共通接続されたアノード電極16bと、エミッタ電極16cとベース電極16a間に接続された第1抵抗R1と、ベース電極16aに接続された第2抵抗R2とを備える。

(もっと読む)

41 - 60 / 205

[ Back to top ]