Fターム[5F082BA47]の内容

Fターム[5F082BA47]に分類される特許

21 - 40 / 369

トランジスタ素子及びトランジスタ用エピタキシャルウェハの製造方法

【課題】GaAs基板からHBT構造層に伝搬する転位を抑制したトランジスタ素子及びトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】GaAs基板2上に高電子移動度トランジスタ構造層3が形成され、高電子移動度トランジスタ構造層3上にヘテロバイポーラトランジスタ構造層4が形成されたトランジスタ素子において、GaAs基板2の転位密度が10,000/cm2以上100,000/cm2以下であり、高電子移動度トランジスタ構造層3とヘテロバイポーラトランジスタ構造層4との間に、InGaPからなるエッチングストッパ層12と、エッチングストッパ層12上に設けられたGaAsからなる安定化層21と、を設けたものである。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】BiFETデバイスに含まれるFETのオン抵抗の悪化を抑制する。

【解決手段】共通基板1上に第1SL10及び第2SL20積層体が順に形成された半導体装置であって、第2積層体が除去されて残存する第1積層体は、電界効果型トランジスタを構成し、第1積層体上に積層された第2積層体は、電界効果型トランジスタとは異なる素子(バイポーラトランジスタ)を構成し、電界効果型トランジスタを構成する第1積層体は、第1積層体に形成されるリセスの停止位置を規定し、かつInGaPから成るエッチング停止層10と、リセス内に配置されるゲート電極25の下方に配置され、かつAlGaAsから成る下部化合物半導体層8と、エッチング停止層10と下部化合物半導体層8との間に挿入され、エッチング停止層に含まれるリンが下部化合物半導体層まで熱拡散し、下部化合物半導体層を構成する元素と化合することを抑止するスペーサ層9とを含む。

(もっと読む)

高電圧バイポーラベースESD保護構造

【課題】面積効率の良い高電圧の単極性ESD保護デバイスを提供する。

【解決手段】ESD保護デバイス300は、p型基板303と、基板内に形成され、カソード端子に接続されるn+及びp+コンタクト領域310、312を包含し、第1のpウェル308−1と、基板内に形成され、アノード端子に接続されるp+コンタクト領域311のみを包含する第2の別個のpウェル308−2と、第1及び第2半導体領域を取り囲み且つこれら半導体領域を分離するように基板内に形成された、電気的にフローティングのアイソレーション構造304、306、307−2とを含む。カソード及びアノードの端子に、トリガー電圧レベルを上回る正電圧が印加されると、ESD保護デバイスは、構造を通り抜ける低インピーダンス経路を提供してESD電流を放電するよう、内在サイリスタをスナップバックモードに入らせる。

(もっと読む)

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

抵抗変化型メモリ

【課題】 メモリの動作特性の向上を図る。

【解決手段】実施形態の抵抗変化型メモリは、ビット線BLとワード線WLと、第1エミッタ21と、第1ベース23と、第1コレクタ22とを有する、第1駆動型の第1バイポーラトランジスタ2と、第2エミッタ31と、第2ベース33と、第2コレクタ32とを有する第2駆動型の第2バイポーラトランジスタ3と、第1及び第2端子を有する抵抗変化型メモリ素子1と、を具備し、メモリ素子1の第1端子は第1及び第2エミッタ21,31に接続され、メモリ素子1の第2端子は、ビット線BLに接続され、第1及び第2ベース23,33はワード線WLに接続される。

(もっと読む)

エピレス基板における分離型の相補型MOS装置

【課題】高い実装密度を得ることが可能な半導体装置の製造プロセスを提供する。

【解決手段】半導体装置を電気的に分離するための構造は、エピタキシャル層を含まない半導体基板240内にドーパントを打込むことにより形成される。この打込みに続き、極めて限られた熱収支に上記構造を晒すことでドーパントが顕著に拡散しないようにする。その結果として、上記分離構造の寸法が制限かつ規定され、こうして、エピタキシャル層を成長させる工程とドーパントを拡散させる工程とを含む従来のプロセスを用いて得られるよりも高い実装密度を得ることができる。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

電源システム抑止方法ならびにその装置および構造

【課題】電源制御装置システム(25)の動作中に、システム(25)の動作を抑止する方法を提供する。

【解決手段】例えば、負荷(63)にシステム(25)の動作を抑止する条件を検出した場合、抑止トランジスタ(35)をオンにし、出力(48)を低に引き下げ、キャパシタ(49)を放電させる。キャパシタ(49)が初期電圧値より低い値まで放電されると、検出器40は、トランジスタ(44)をオンにし、装置(12)のトランジスタ(15)をオフにする。その結果、システム(25)は、出力(21)から供給される第2出力電流の供給を抑止し、第2出力電流よりはるかに小さい第1出力電流のみを出力(19)から供給する。制御装置(51)が動作しないため、システム(25)から負荷(63)への電圧供給が停止される。

(もっと読む)

半導体装置

【課題】支持基板に接地電極を備えることなく、第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供する。

【解決手段】支持基板10を、第1導電型領域10aと第2導電型領域10bとを有し、第1素子形成領域20にノイズが印加されてノイズが伝播されたときの当該ノイズの伝播経路中に、第1、第2導電型領域10a、10bで構成されるPNP接合またはNPN接合を有するものとする。このような半導体装置では、PNP接合またはNPN接合の間に構成される空乏層により、第1、第2素子形成領域20、30の間でノイズが伝播することを抑制することができる。

(もっと読む)

半導体装置

【課題】同一基板上にヘテロ接合バイポーラトランジスタ(HBT)と電界効果トランジスタ(FET)とが形成され、HBTのコレクタ抵抗が低減されてHBTの特性が向上され、かつFETのゲートリセスのエッチング精度が良好で、FETのオン抵抗が低い半導体装置を安定的に提供する。

【解決手段】HBT101Aにおいては、サブコレクタ層が複数の半導体層13〜15の積層構造からなり、かつ、サブコレクタ層においてコレクタ層17より張り出した部分上にコレクタ電極28が形成されている。FET101B、101Cにおいては、HBT101Aのサブコレクタ層をなす複数の半導体層のうち半導体基板1側の少なくとも1層の半導体層13が、キャップ層の少なくとも一部の層を兼ねている。HBTサブコレクタ層の総膜厚が500nm以上であり、FETキャップ層の総膜厚が50nm以上300nm以下である。

(もっと読む)

半導体装置

【課題】占有面積を増大させずに、電源投入開始後のチップ動作時にESD保護素子で発生するリーク電流を低減することができるESD保護素子を提供する。

【解決手段】電源ライン及び接地ラインを含む電子回路が形成された半導体基板10と、半導体基板10において電源ライン(Vdd)及び接地ライン(Vss)間に設けられ、サイリスタSCR及びサイリスタを駆動するトリガーダイオードTDを含む静電気放電保護素子とを有し、トリガーダイオードは、半導体基板10に形成されたアノード拡散層22と、アノード拡散層22から離間して半導体基板10に形成されたカソード拡散層21と、アノード拡散層22及びカソード拡散層21間において半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極17とを有し、外部電源に接続された外部端子(パッド電極27)がゲート電極17に電気的に接続されている構成とする。

(もっと読む)

半導体装置

【課題】 立ち上がり電圧低減と高耐圧実現の両立を可能とする構造を提案する。

【解決手段】 SiC縦型ダイオードにおいて、カソード電極21と、n++カソード層10と、n++カソード層上のn−ドリフト層11と、一対のp+領域12と、n−ドリフト層11とp+領域12の間に形成され、且つ一対のp+領域12に挟まれたn+チャネル領域16と、n++アノード領域14と、n++アノード領域14とp+領域12に形成されたアノード電極22を備える。

(もっと読む)

半導体集積回路装置

【課題】絶縁素子分離型のバイポーラトランジスタの放熱性を改善する。

【解決手段】薄い半導体層の第1のエリアに配置された第1のトランジスタと、薄い半導体層の第2のエリアに配置された第2のトランジスタで構成される回路部と、を備え、第1のトランジスタは、並列接続された複数のバイポーラトランジスタ素子を構成する複数の単位能動領域の配列全体を囲って配置された素子分離溝を含み、素子分離溝を能動領域から少なくとも1μm離間して設け、能動領域で生成される熱を単位能動領域を囲んで存在する半導体領域から外方に放熱させる構成を備えてなり、第2のトランジスタは、バイポーラトランジスタ動作を行う単位能動領域と、単位能動領域を取り囲んで形成され単位能動領域から1μm以下の位置に配置された素子分離溝を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】MIMキャパシタの耐圧低下や耐湿劣化を防ぐことができる半導体装置及びその製造方法を得る。

【解決手段】半導体基板1上にベース電極4を形成する。ベース電極4を覆うようにレジスト膜5を形成する。レジスト膜5をマスクとした等方性エッチングにより、ベース電極4の周辺の半導体基板1を掘り込んでベースメサ溝6を形成する。ベース電極4上に絶縁膜7を形成する。絶縁膜7上に配線電極8を形成する。レジスト膜5の外周とベース電極4の外周との最小幅wは、ベースメサ溝6がベース電極4の下に入り込まないような値に設定されている。

(もっと読む)

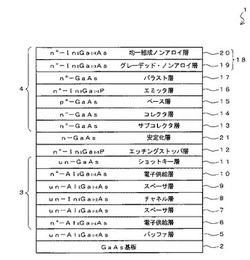

トランジスタ素子

【課題】GaAs基板上にHEMT、HBTを順次積層してなるトランジスタ素子において、HEMTの移動度の低下を抑制することが可能なトランジスタ素子を提供する。

【解決手段】GaAs基板2上に高電子移動度トランジスタ(HEMT)3が形成され、HEMT3上にヘテロバイポーラトランジスタ(HBT)4が形成されたトランジスタ素子において、HEMT3がアンドープInGaAsPからなるバリア層10を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】結晶欠陥による接合リークを防止しながら、バイポーラトランジスタの面積を縮小し、コレクタ容量の低減によってトランジスタ特性を向上できるようにした半導体装置及びその製造方法を提供する。

【解決手段】活性領域1からSTI4上にかけて連続して形成したSiGe膜は、半導体基板3上ではSiGeエピ膜6となり、STI4上ではSiGeポリ膜7となる。半導体基板3とSTI4の境界はSiGe−HBT形成工程以前の洗浄工程によって段差15が生じており、SiGeエピ膜6及び半導体基板3には、上記境界を基点とした結晶欠陥が応力によって発生する可能性がある。この境界に第1のP型不純物層8及び第2のP型不純物層9を設けることで、結晶欠陥をこれらP型不純物層8、9に内包し、接合リークの発生を抑制する。

(もっと読む)

高保持電圧デバイス

高保持電圧(HVO静電放電(ESD)保護回路が、シリコン制御整流器(SCE)デバイスと、SCRデバイスの保持電圧を高める、SCRデバイスのアノードとカソードとの間の長さ(LAC)内に設置された補償領域とを備える。補償領域は、負のフィードバック機構をSCRデバイスに導入することで、SCRのループゲインに影響を及ぼし、高保持電圧で回生フィードバックに達しうる。  (もっと読む)

(もっと読む)

トレンチにより制限された分離拡散領域を備えた相補型アナログバイポーラトランジスタ

【課題】表面上に素子をより高密度に実装する。

【解決手段】第1のトレンチと第2のトレンチとの間の位置において、エピタキシャル層の表面から基板へと下方に延在するドーパントのウェルは、エピタキシャル層の背景ドーピング濃度とは異なるドーピング濃度を有し、エピタキシャル層の残りの部分と第1および第2の接合を形成する。第1の接合は、第1のトレンチの底部から基板に延在し、第2の接合は、第2のトレンチの底部から前記基板に延在する。ウェルおよび第1および第2のトレンチは分離構造を構成し、分離構造は、分離構造の一方側のエピタキシャル層に形成された第1の素子と分離構造の他方側のエピタキシャル層に形成された第2の素子とを電気的に分離する。分離構造による電気的分離は第1および第2のトレンチとPN接合とによってもたらされ、ウェルは第1の導電型の材料でドープされ、基板およびエピタキシャル層は、第1の導電型とは反対の第2の導電型の材料でドープされ、第1および第2の接合はPN接合である。

(もっと読む)

21 - 40 / 369

[ Back to top ]